3.功能描述

3.1 UART串行协议

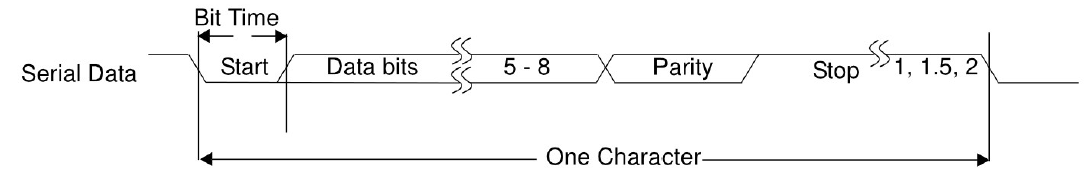

因为DW_apb_uart和所选设备之间的串行通信是异步的,所以在串行数据中添加了额外的位(开始和停止)来指示开始和结束。利用这些位可以同步两个设备。这种带有起始和停止位的串行数据结构称为一个字符。其结构如下图所示:

可以向串行字符中添加额外的奇偶校验位,该位出现在字符结构中最后一个数据位和停止位之前,以使DW_apb_uart能够对接收到的数据执行简单的错误检查。

DW_apb_uart线路制寄存器用于控制串行字符特性。数据字的各个位在起始位之后发送,从最低有效位(LSB)开始,接着是奇偶校验位(可选),最后是停止位(可配为1、1.5或2)。

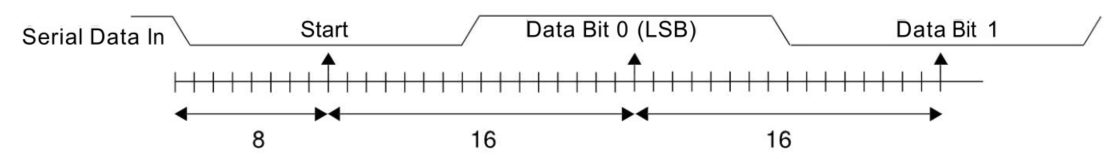

传输中的所有位(使用1.5个停止位时的半停止位除外)的传输时间完全相同,这称为位周期或位时间。一位时间等于16波特时钟,为确保线路的稳定性,一旦检测到起始位,接收器就会在大约位时间的中点对串行输入数据进行采样。由于每个位传输的波特时钟的确切数量是已知的,因此采样的中点为起始位的中点采样后每16个波特时钟。下图显示了串行字符中前几位的采样点。

作为16550标准的一部分,提供了一个可选的波特时钟参考信号(baudout_n),以向需要它的接收设备提供时序信息。DW_apb_uart的波特率由串行时钟(单时钟实现中的sclk或pck)和除数锁存寄存器(DLH和DLL)控制。下圖顯示了針對不同除數值得 baudout_n 輸出的時序圖。

3.2 IrDA 1.0 SIR协议

红外数据协会(IrDA)1.0串行红外(SIR)模式支持使用红外辐射作为传输介质与远程设备进行双向数据通信。IrDA 1.0 SIR模式指定最大波特率为115200。

数据格式类似于标准串行(sout和sin)数据格式。每个数据字符以串行方式发送,以一个起始位开始。随后是8个数据位,并以至少一个停止位结束。因此,可以发送的数据位数是固定的,在这种模式下,不能提供奇偶校验信息,并且只使用一个停止位。

使用线路控制寄存器(LCR)调整发送的数据位数或启用奇偶无效。当DW_apb_uart配置为支持IrDA 1.0 SIR时,可使用模式控制寄存器(MCR)的位6来启用。当 DW_apb_uart未配置为支持IrDA SIR模式时,不执行任何逻辑且无法激活该模式,减少总门数。当SIR模式启用并处于活动状态时,串行数据分别在sir_out_n和sir_in端口上发送和接收。

逻辑0表示发送单个红外脉冲,逻辑1表示不发送脉冲,每个脉冲的宽度是正常串行位时间的3/16ths。因此,每个新字符都以红外脉冲作为起始位开始。然而,由于红外脉冲激励IrDA接收器的光电晶体管基集,接收到的数据与传输的数据相反,从而将其输出拉低。然后将此反相晶体管输出馈送到DW_apb_uart_sir_in端口,该端口具有正确的UART极性。下图显示了IrDA SIR数据格式与标准串行格式的时序图。

DW_apb_uart可配置为支持低功耗接收模式,在此模式下配置DW_apb_uart时,支持接收1.41微秒(最小脉冲持续时间)的SIR脉冲,以及正常串行位时间的3/16。使用这种低功耗接收模式需要对低功耗除数锁存器(LPDLL/LPDLH)寄存器进行编程。

启用IrDA SIR模式时,DW_apb_uart操作与禁用模式时类似。当IrDA SIR模式启用时,数据传输只能以半双工方式发生,这是因为IrDA SIR物理层指定发送和接收之间的最小延迟为10ms,这10ms的延迟必须由软件产生。

3.3 FIFO模式

DW_apb_uart可配置为使用FIFO以缓冲发送和接收数据。如果未选择FIFO支持,则不实施FIFO,并且一次只能将单个接收数据字节和发送数据字节存储在RBR和THR中。

在FIFO模式下,FIFO可选择为外部客户提供的FIFO RAM或内部基于DesignWare D触发器的RAM(DW_ram_r_w_s_dff)。如果配置的FIFO深度大于256,则FIFO存储器选择被限制为外部。此外,内部存储器选择将数据读取端口类型限制为基于D触发器的同步读取端口RAM。

选择外部RAM支持时,可使用同步或异步RAM。异步RAM在内存地址和读取信号处于活动状态的时钟周期内提供读取数据,以便在下一个时钟上升沿采样。同步单级RAM将数据寄存在当前地址输出,直到下一个时钟周期(第二个时钟上升沿)才可用。下图显示了异步和同步RAM的时序图。

类似的,也可使用同步RAM进行写入,将数据注册到当前地址。下图显示了RAM写入的时序图。

选择FIFO模式后,可选的可编程FIFO访问模式可用于测试目的,它允许主机写入接收FIFO,主机读取发送FIFO。当未选择FIFO访问模式时,不执行任何相应的逻辑并且无法启用该模式,从而减少总门数。选择FIFO访问模式后,可使用FIFO访问寄存器(FAR[0])启用它。一旦启用,发送和接收FIFO的控制部分将被重置,并且FIFO被视为空。

数据能够正常写入发送FIFO,然而,在这种模式下不会发生串行传输(正常操作停止),因此没有数据离开FIFO。已写入发送FIFO的数据可以通过发送FIFO读取(TFR)寄存器读回,读取时该寄存器在发送FIFO顶部提供当前数据。

同样,可以正常从接收FIFO中读取数据,由于DW_apb_uart的正常操作在此模式下停止,因此必须将数据写入接收FIFO以便可以回读。使用接收FIFO写(RFW)寄存器将数据写入接收FIFO,寄存器位10的高两位用于将帧错误和奇偶错误检测信息写入接收FIFO,设置RFW[9] 指示帧错误,设置RFW[8] 指示奇偶校验错误。虽然这些位不能通过接收缓冲寄存器读回,但可以通过读取线路状态寄存器并在相关数据位于接收FIFO顶部时检查相应位来检查它们。

3.4 时钟模式

DW_apb_uart可配置为具有一个系统时钟(pclk)或两个系统时钟(sck)。实施第二个异步串行时钟(sclk)可适应准确的穿行波特率设置以及APB总线接口要求。选择两个时钟设计时,使用同步模块用于同步两个系统时钟边界的所有控制和数据。数据同步模块具有待处理数据功能。下图的时序显示了这个过程。

完全同步握手发生在所有“数据同步”的信号上,所有“电平同步”的信号只需通过两个目标时钟寄存器即可。这两种同步类型都会导致额外的数据路径延迟。然而,除了将串行时钟(sclk)限制在不超过pclk时钟的四倍(用于无空闲断言的背靠背串行通信)之外,该额外延迟对接收或传输的数据没有负面影响。

如果串行时钟快于pclk的4倍,则没有足够的时间接收完整的输入字符并将其推入接收器FIFO。然而,在大多数情况下,pclk的信号比串行时钟快,因此这不会成为问题。在初始串行控制寄存器编程之后,在串行数据发送或接收之前,还需要等待一段时间。

串行时钟模块必须有时间查看新的寄存器值并重置各自的状态机。总时间保证不超过两个系统时钟中较慢的8个时钟周期。因此,在配置之后的最长时间到期之前,不应发送或接收任何数据。在只有一个时钟的系统中,没有额外的延迟。

3.5 中断模式

只要启用并激活几种优先中断类型之一,就会出现DW_apb_uart中断输出信号(intr)的断言。以下几种中断类型可通过IER寄存器启用:

-

接收错误中断;

-

接收数据有效中断;

-

字符超时中断(仅在FIFO模式下有效)

-

传输保持寄存器空或低于阈值(在可编程THRE中断模式下)

-

调制解调器状态

3.6 自动流量控制

DW_apb_uart可配置为具有16750兼容的Auto RTS和Auto CTS串行数据流控制模式可用。如果未实现FIFO,则无法选择此模式,当未选择自动流量控制时,不执行任何相应的逻辑并且无法启用该模式,从而减少总门数。选择自动流量控制模式后,可使用调制解调器控制寄存器(MCR[5])启用它。下图显示了自动流量控制功能的框图。

Auto RTS和Auto CTS功能描述如下:

1. Auto RTS:发生以下情况时激活:

- 在配置期间选择自动流量控制;

- 选择FIFO模式;

- RTS(MCR[1] 和MCR[5] 均被置位);

- FIFO已使能(FCR[0] 被置位);

- SIR模式被禁用(未置位MCR[6]);

当Auto RTS激活时,并且接收器FIFO电平达到FCR[7:6] 设置的阈值时,RTS_n输出被强制非激活(即高电平)。当rts_n连接到另一个UART设备的cts_n输入时,另一个UART停止发送串行数据,直到接收FIFO有可用空间(直到它完全为空)。

可选择的接收FIFO阈值为:1、1/4、1/2和“2小于满”。由于rts_n变为非活动状态后(由于数据已经进入另一个UART中的发送模块),可能会向DW_apb_uart发送一个额外的字符,因此将阈值设置为“小于满2”允许最大限度地使用FIFO,并保证安全一个字符的区域。

一旦通过读取接收缓冲寄存器(RBR)使接收FIFO完全为空,rts_n再次变为有效(低有效),向另一个UART发出继续发送数据的信号。

如果选择了其他所有选项并设置了正确的MCR,如果通过FCR[0] 禁用FIFO或UART处于SIR模式(MCR[6] 设置为1)时,自动流量控制也会被禁用。当Auto RTS未实现或禁用时,rts_n仅由MCR[1] 控制。下图显示了Auto RTS操作的时序图。

2. Auto CTS:发生以下情况时激活:

- 在配置期间选择自动流量控制;

- 选择FIFO模式;

- AFCE(MCR[5] 被置位)

- FIFO被启用(通过FCR[0])

- SIR模式被禁用(MCR[6] 被置位)

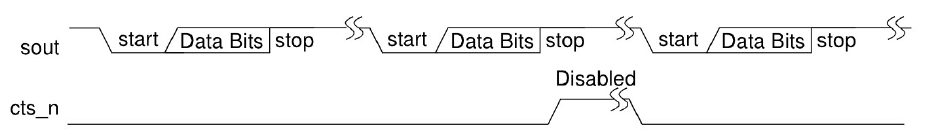

当Auto CTS启用(激活)时,只要cts_n输入变为非激活(高有效),就会禁用DW_apb_uart发送器,这可防止UART的接收FIFO溢出。如果cts_n输入在最后一个停止位的中间没有被禁用,则在禁用发送器之前发送另一个字符。当发送器被禁用时,发送FIFO仍可被写入,甚至溢出。

在使用Auto CTS模式时,会发生以下情况:

- 可以读取UART状态寄存器以检查FIFO是否已满(USR[1]设置为0)

- 当前FIFO级别可通过TFL寄存器读取

- 必须启用可编程THRE中断模式才能通过线路状态寄存器(LSR)访问“FIFO满”状态

当使用“FIFO已满”状态时,软件可在每次写入发送器FIFO之前对其进行轮询。当cts_n输入再次变为有效(低)时,传输恢复。即使选择了其他所有内容,如果FIFO被禁用(通过FCR[0]),自动流量控制也被禁用。当Auto CTS未实现或禁用时,发送器不受cts_n影响。下图显示了Auto CTS操作的时序。

3.7 可编程THRE中断

DW_apb_uart可配置为具有可编程THRE中断模式以提高系统性能。如果未实现FIFO,则无法选择此模式。当未选择可编程THRE中断模式时,不执行任何逻辑且无法启用该模式,从而减少总门数。

选择可编程THRE中断模式时,可以通过中断启用寄存器(IER[7])启用它。当FIFO和THRE模式被实现并启用时,THRE中断和dma_tx_req_n在编程的发送FIFO空阈值电平及以下有效,而不是空阈值。

下图为可编程THRE中断模式的中断产生流程图。

若要按照上图所示控制THRE中断,必须满足以下条件:

- FIFO_MODE != NONE

- THRE_MODE == Enabled

- FIFOs enabled (FCR[0] == 1)

- THRE模式使能(IER[7] == 1)

该阈值电平使用FCR[5:4] 进行编程,可用的空阈值为:空、2、4和Vz。最佳阈值的选取取决于系统及时开始新传输序列的能力。但是,通过防止发送FIFO为空,这些阈值之一可证明在提高系统性能方面是最佳的。

除了中断变化之外,线路状态寄存器(LSR[5])还将功能从指示发送FIFO为空切换到FIFO为满。这允许软件在写入另一个字符之前通过轮询LSR[5] 来填充每个发送序列的FIFO。然后流程变为“只要发生中断并且有数据要发送,就填充发送FIFO”,而不是等到FIFO完全为空。每当系统太忙而无法立即响应时,等到FIFO为空会导致性能下降。当此模式与自动流量控制结合使用时,可以进一步提高系统的效率。

即使选择并启用了其他所有功能,如果通过FCR[0] 禁用FIFO,也会禁用可编程THRE中断模式。未选中或禁用时,THRE中断和LSR[5] 正常工作(均反映THR或FIFO空)。非可编程THRE中断模式时产生THRE中断的流程如下图所示。

若要按上图来控制THRE中断,必须满足以下一个或多个条件:

-

FIFO_MODE == NONE

-

THRE_MODE == disabled

-

FIFOs disabled (FCR[0] == 0)

-

THRE模式未启用(IER[7] == 0)

443

443

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?