概念:

一种高速串行计算机扩展总线标准。

物理:

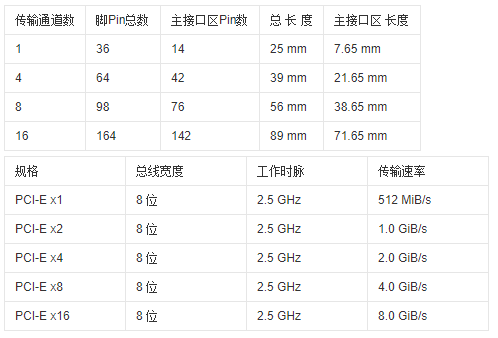

PCIExpress卡适合其物理尺寸或更大的插槽(使用×16作为最大的)。实际连接到插槽的通道数量也可能少于物理槽大小所支持的数量。一个例子是一个×16插槽可以运行×1、×2、×4、×8、×16的卡,当运行×4卡时只提供4条通道。其规格可以读为“×16(×4模式)”,而“×size @×速度”符号(“×16 @×4”)也是常见的。

标准:

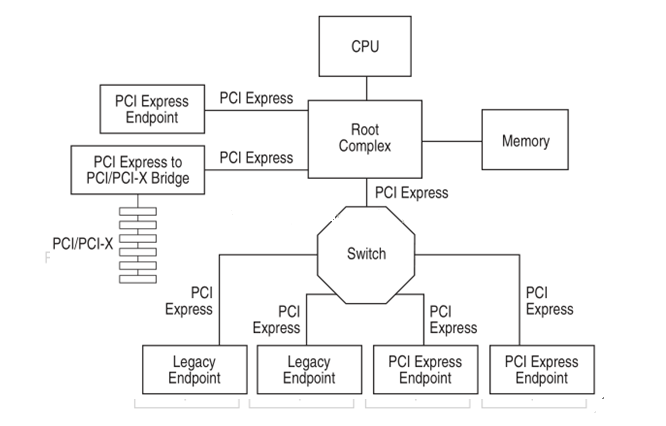

总线架构:

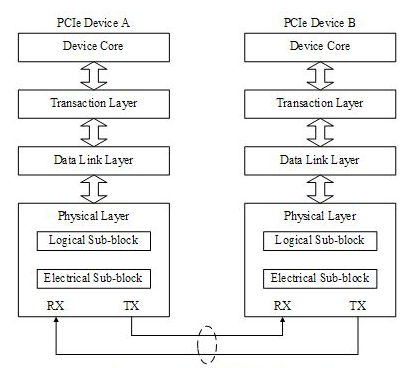

分层结构:

它共分为四层,从下到上分别为:物理层(Physical Layer)、数据链路层(Link Layer)、处理层(Transaction Layer)和软件层(Software Layer)。图中并木有显示出软件层。

1、物理层

物理层是最底层,它负责接口或者设备之间的连接。物理层决定了PCIe总线接口的物理特性,如点对点串行连接、微差分信号驱动、热拨插、可配置带宽等,决定了其四根线全双工的串行数据传输方式。

在物理层的另一处重要方面就是中断。PCIe总线支持两个类型的中断,现行的PCI INTx (x= A, B, C, or D) 中断(即PCI总线的中断)被保留下来了,仍可在PCIe总线中应用。还有一个新的中断类型,那就是MSI (Message Signaled Interrupt,信息信号中断),INTx中断方式可以用信号方式中断主机芯片请求,它可以与现行的PCI总线的驱动程序和操作系统兼容。PCIe设备必须支持INTx和MSI两种中断模式,原有设备将压缩INTx中断信息在PCIe处理信息中。MSI中断是通过内存写处理操作边沿触发和发送的。重新编写驱动程序对于MSI边沿触发中断是非常有利的,MSI方案在使用数据包协议通过串行连接中是一种行之有效的本地中断方式。MSI在多处理器系统中任何设备都可以发送中断,比起主机直接发送中断更加有效,所以现在许多多处理器系统和I/O架构都对MSI中断技术提供支持。

2、数据链路层

数据链路层的主要职责就是确保数据包可靠、正确的传输。确保数据包的完整性,并在数据包中添加序列号和发送冗余校验码到处理层。大多数数据包是由处理层发起的,基于信任的原则,数据流控制协议确保数据包只在终端缓存空闲时进行传输。排队了所有数据的重试,使得信道带宽浪费现象得到有效地约束。但数据链路层在信号中断时自动重新传输数据包。

3、处理层

处理层的作用主要是接受从软件层送来的读、写请求,并且建立一个请求包传输到数据链路层。所有请求都是分离执行的。处理层同时接受从链路层传来的响应包,并与原始的软件请求关联。处理层还整合或者拆分处理级数据包来发送请求,如数据读、写请求,并且操纵链接配置和信号控制。以确保端到端连接通信正确,没有无效数据通过整个组织(包括源设备和目标设备,甚至包括可能通过的多个桥接器和交换器)。处理层包括4个地址空间,其中3个是PCI接口原有的,如内存、I/O和配置地址空间,加上一个PCie新增的“信息空间”。

4、软件层

软件层是保持与PCI总线兼容的关键。其目的在于使系统在使用PCIe启动时,像在PCI下的初始化和运行那样,无论是在系统中发现的硬件设备,还是在系统中的资源,如内存、I/O空间和中断等,它可以创建非常优化的系统环境,而不需要进行任何改动。在PCIe体系结构中保持这些配置空间和I/O设备连接的规范稳定是非常关键的。事实上,在PCIe平台中,所有操作系统在引导时都不需要进行任何编辑,也就是说在软件方面完全可以实现从PCI总线平稳过渡。

在软件响应时间模式方面,PCIe体系结构支持PCI的本地存储、共享内存模式,这样所有PCI软件在PCIe体系中运行都不需任何改变。当然新的软件可能包括新的特性。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?