UCIe是目前业界Die-to-Die主流互连技术。UCIe技术通过提供高带宽、低延时的Die-to-Die互连解决方案,使得AI PC中的不同Die或功能模块能够更紧密地协同工作,进而加速AI任务的执行和数据处理能力。这种互连技术的优化,对于提升AI PC的整体性能和用户体验具有重要意义。同时,为了提升芯片的处理能力,需要扩充外部存储接口以提升存储能力。

目前,基于UCIe的Multi-Die方案的AI PC 扩充IO有三种方法:

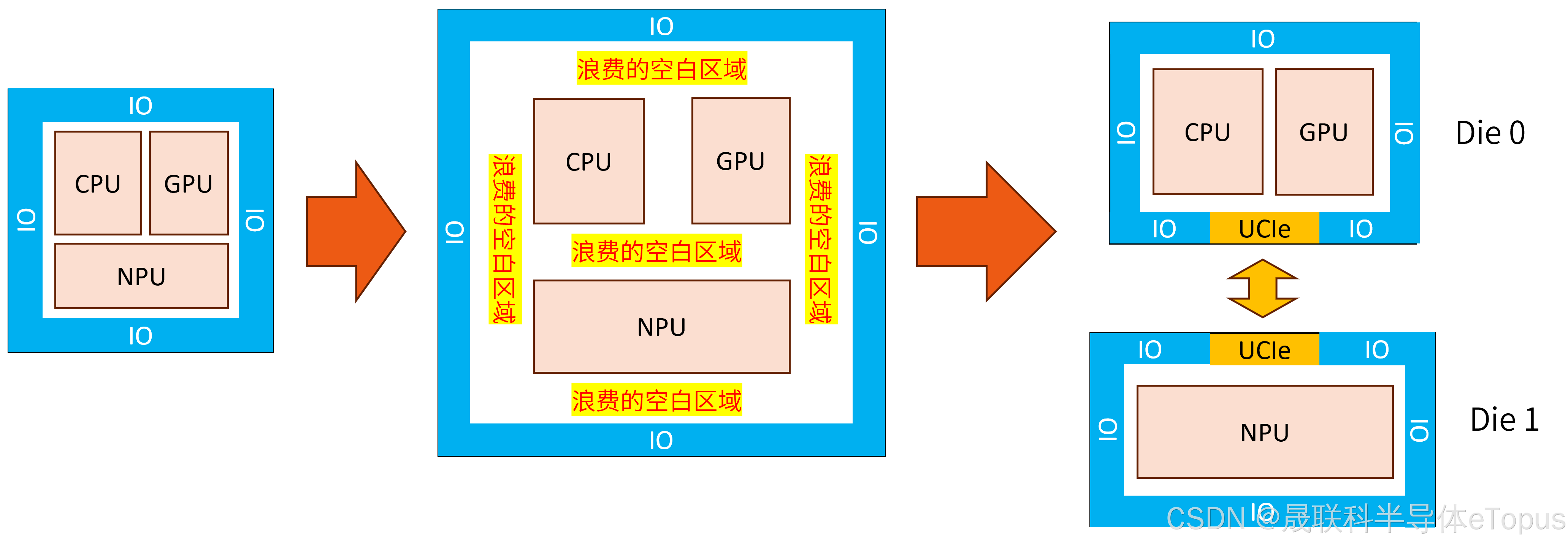

分离功能模块为不同的Die,从而扩充外围IO接口

将部分功能模块如NPU拆分出来放在单独的Die上,这样不仅可以容纳更多IO接口,也消除了因扩大IO而导致的中间空白区域的浪费。

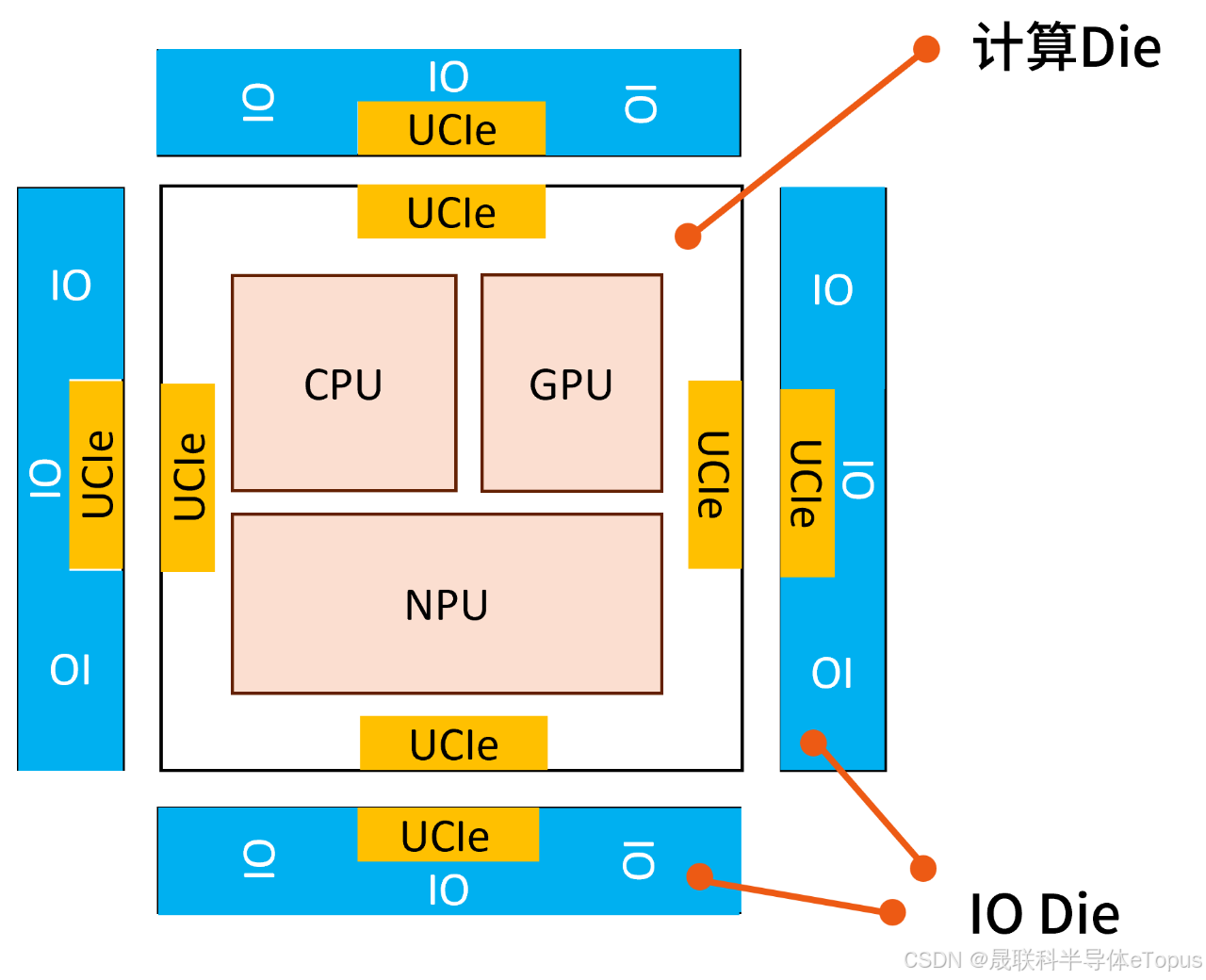

IO Die

IO Die

• 将IO部分(主要包括Memory、PCIe和UCIe)单独放在一个Die上,在计算Die的四周都可以放满,以满足芯片对高IO带宽的需求;

• 凹形布局可以最大化IO模块的面积,并通过UCIe跟计算Die进行互连;

• IOD和计算Die可以采用不同Foundry的不同Process Node,并拥有不同的产品迭代周期,优化产品Time-to-Market,降低总体成本。

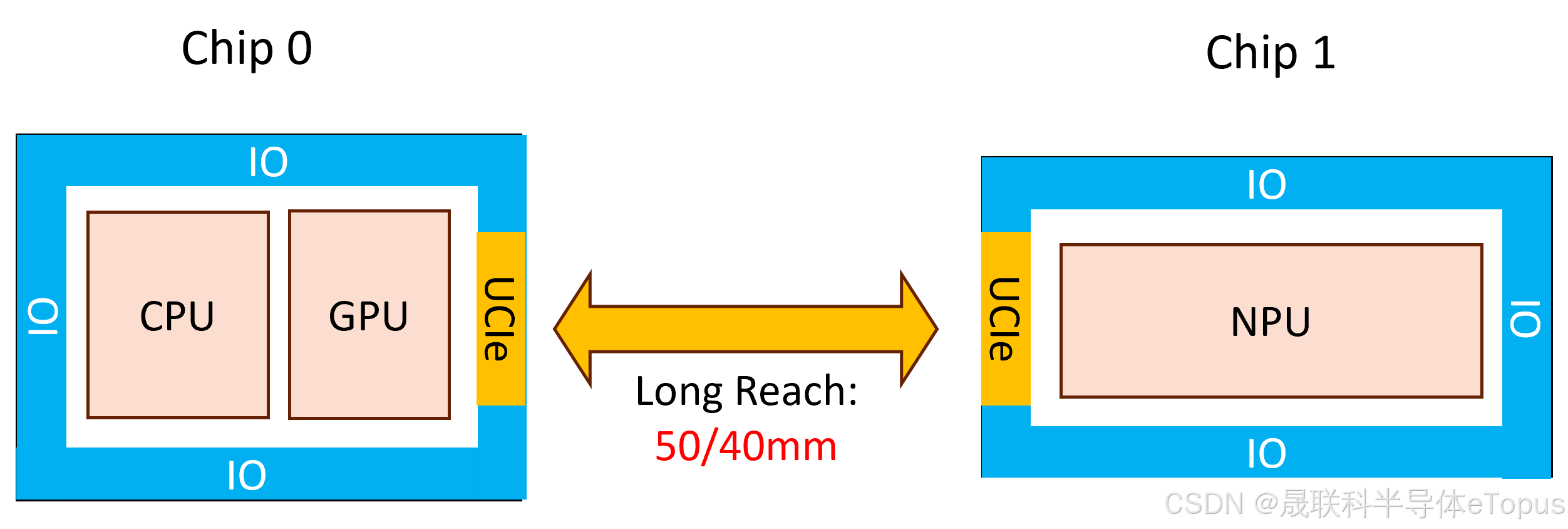

跨封装的Long Reach UCIe互连

跨封装的Long Reach UCIe互连

• 将CPU和GPU合封在一个芯片里,NPU作为另外一个单独的芯片,这样在设计上可以实现最大程度的解耦,进一步提升灵活性并降低成本;

• 两个芯片可以由两家不同的公司提供,发挥出每家公司的特长,提高产业链协同效率;

• CPU芯片可以是x86、ARM和RISC-V等架构,NPU可以跟不同的CPU协同工作,并充分利用不同的架构软件生态。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?