时序电路也被称为(有限)状态机FSM(Finite State Machine),这种更正式的称谓经常出现在技术文献之中,因为它们的功能行为可以用有限的状态个数来表示,通常用(原始)状态图来描述。状态机容易构成良好的同步时序逻辑模块,可用于解决大规模逻辑电路设计中的竞争和冒险现象。

一 任务描述

根据所学的时序电路的知识利用VerilogHDL描述一个可综合的序列检测器用于检测输入数据码流中的特定序列1101。

本次实验要求采用Moore型状态机和Mealy型状态机对该序列检测器进行设计,同时需要完成一段式、二段式、三段式代码的编写及仿真测试。

二 实验原理

一 状态机的分类

状态机主要分为两种类型:

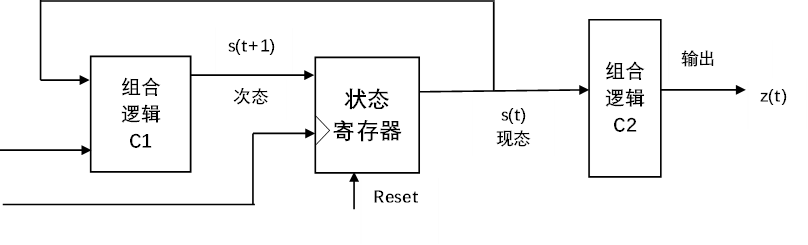

1、 Moore型状态机:下一状态只由当前状态决定。即:次态=f(现状,输入),输出=f(现状);

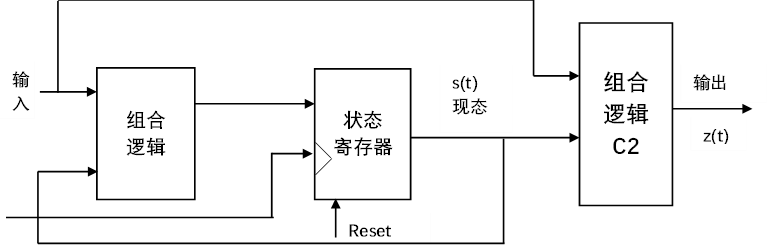

2、 Mealy型状态机:下一状态不但与当前状态有关,还与当前输入值有关。即:次态=f(现状,输入),输出=f(现状,输入)。

二 状态机的写法

有限状态机具有多种描述风格,常用的有一段式描述、二段式描述和三段式描述。

1、 一段式描述:把状态译码、状态寄存、状态输出都放在一个always块中,这种描述方式是代码编写简单,缺点是对代码的修改和维护比较困难。

2、 二段式描述:把状态译码、状态输出都放在一个always块中(通常用组合逻辑描述),状态寄存放在另外一个always块中(通常用时序逻辑描述)。

3、 三段式描述:把状态译码、状态输出和状态缓存分别放在三个always块中,相对于二段式状态机层次逻辑更清晰,同时便于修改和维护。

三 实验过程及步骤

一 分析题目

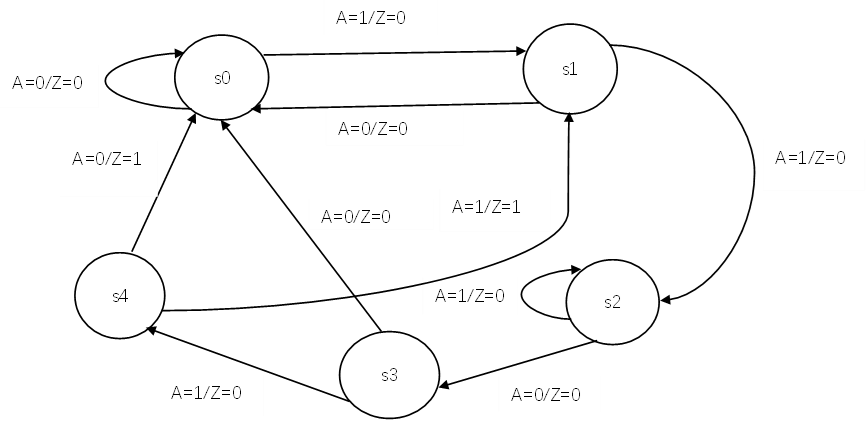

在本题中我们需要设计一个“1101”序列的检测器,只有当检测到“1101”的时候显示高电平,其余时候均显示低电平。分析该状态检测机的状态转移过程:复位键有效的时候,一直停留在s0状态;在s0状态时,当输入为1的时候跳转到下一个状态s1,输入为0的时候仍旧停留在s0。在s1状态时,当输入为1的时候,跳转到下一个状态s2,输入为0的时候返回状态s0。在s2状态时,当输入为0的时候,跳转到下一个状态s3,输入为1的时候,仍旧停留在s2。在s3状态时,当输入为1时,跳转到下一个状态s4,输入为0时,返回状态s0。在状态s4的时候意味着该检测器已经检测到序列“1101”,无条件返回s0。综上分析,只有在状态s4的时候,输出为高电平,其他状态下输出均为低电平。

二 状态转移图

根据上述分析,分别绘制Moore型和Mealy型状态转移图

Moore型状态转移图

Mealy型状态转移图

三 编写代码

1 新建工程,命名为:xuliejianceqi。

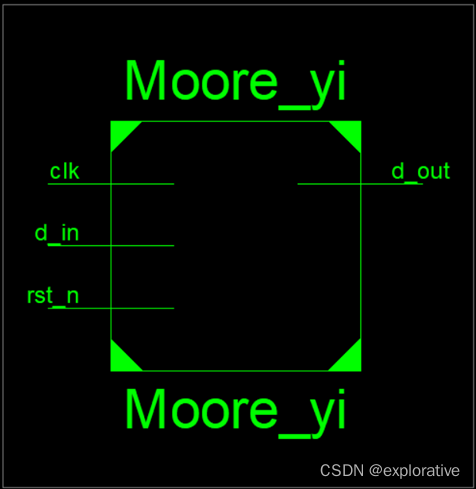

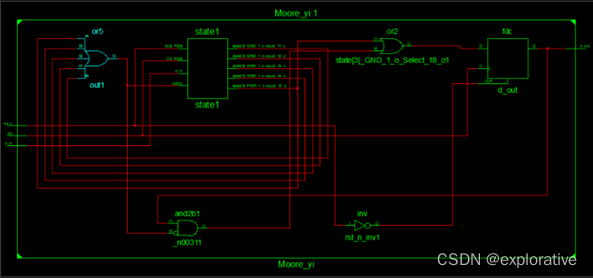

2 首先用一段式描述方法编写Moore型序列检测器的代码,新建新建 Verilog Module 文件,命名为Moore_yi

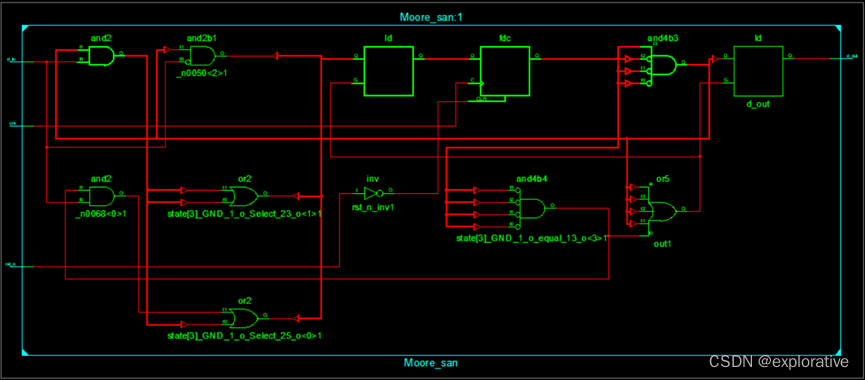

3 运行无误后,查看RTL图如下:

双击此图

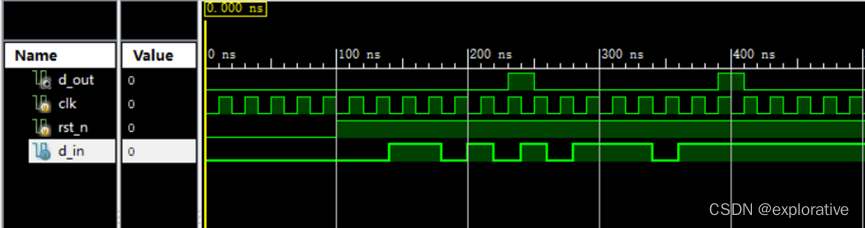

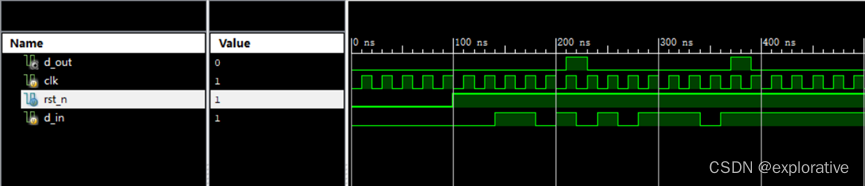

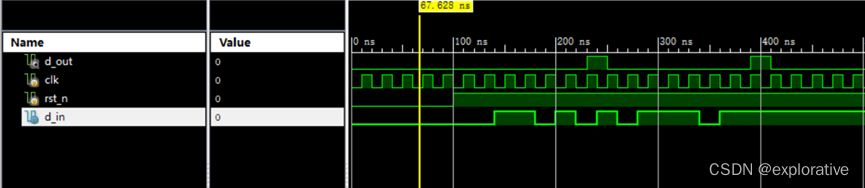

4 编写仿真测试代码,得到波形图如下:

根据我们的测试代码可知,在140-200ns和300-360ns有码流“1101”。通过波形图可以看出,在230ns和390ns的时候输出为高电平。

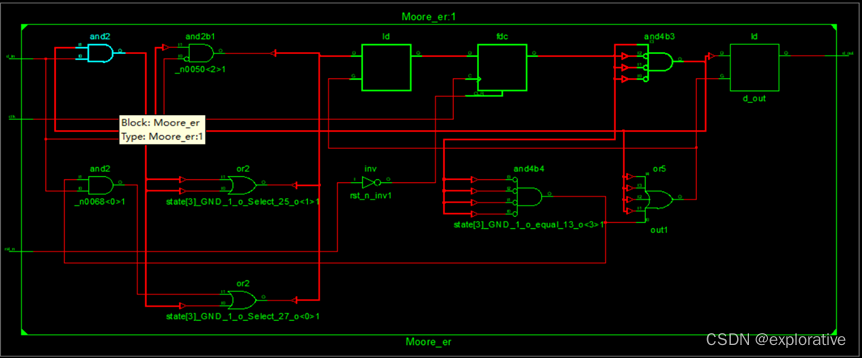

4 用两段式编写程序,新建Verilog Module 文件,命名为:Moore_er

得到RTL图如下:

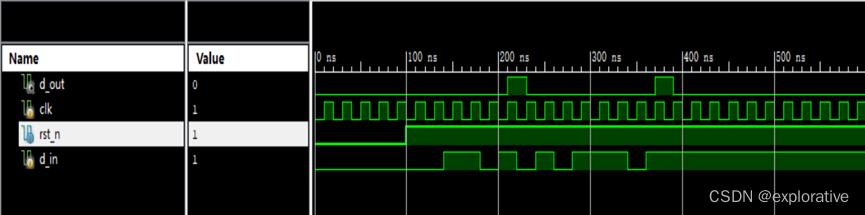

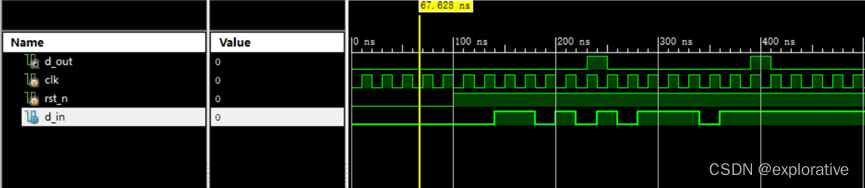

5 编写仿真测试代码,得到波形图如下:

6 用两段式编写程序,新建Verilog Module 文件,命名为:Moore_er

得到RTL图如下:

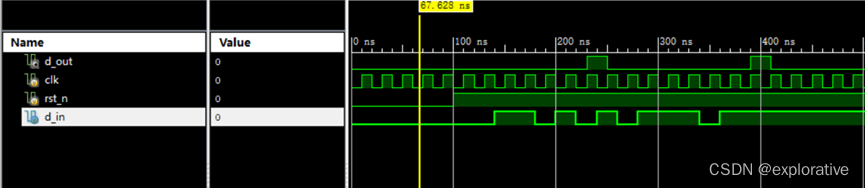

编写仿真代码,得到波形图如下:

7 接下来,编写Mealy型序列检测器

一段式仿真波形图如下:

二段式仿真波形图如下:

三段式仿真波形图如下:

四 实验总结

通过本次实验,我学习了状态机一段式、二段式和三段式的写法,同时也明白了Moore型状态机和Mealy形状机的不同。在状态编码时应该根据状态机状态数目采用独热码或者格雷码编写。尽量采用三段式编写方法,方便后期修改。在状态机编写过程中,体现了容错原则,要考虑处理状态不能不受控制死循环的情况,用if时不能缺少else;用case时不能缺少default。对比Moore型状态机和Mealy型状态机,不难发现:Moore状态机的检测结果输出是与时钟同步的;而Mealy状态机的检测结果输出是异步的,当输入发生变化时,输出就立即变化。因此Mealy状态机的输出比Moore状态机状态的输出提前一个周期。

本文详细介绍了如何使用Verilog HDL设计并实现一个Moore和Mealy型状态机,以检测数据流中的特定序列1101。涵盖了状态转移图绘制、一段式、二段式和三段式代码编写,以及Moore与Mealy状态机的异同分析。

本文详细介绍了如何使用Verilog HDL设计并实现一个Moore和Mealy型状态机,以检测数据流中的特定序列1101。涵盖了状态转移图绘制、一段式、二段式和三段式代码编写,以及Moore与Mealy状态机的异同分析。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?