Verilog HDL语言

Verilog HDL 是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

任务描述

运用所学的组合逻辑电路的知识完成三人表决器的设计,实现少数服从多数的表决规则,并进行验证测试。熟悉 Verilog HDL 文本设计流程,掌握组合逻辑电路的设计仿真和硬件测试的方法。最后完善一个三人表决器电路的功能描述风格 Verilog HDL 代码。

题目来源

举重比赛有三名裁判,当运动员将杠铃举起后,须有两名或两名以上裁判认可,方可判

定试举成功,若用 A、B、C 分别代表三名裁判的意见输入,同意为 1,否定为 0;F 为裁判

结果输出,试举成功时 F=1,试举失败时 F=0。

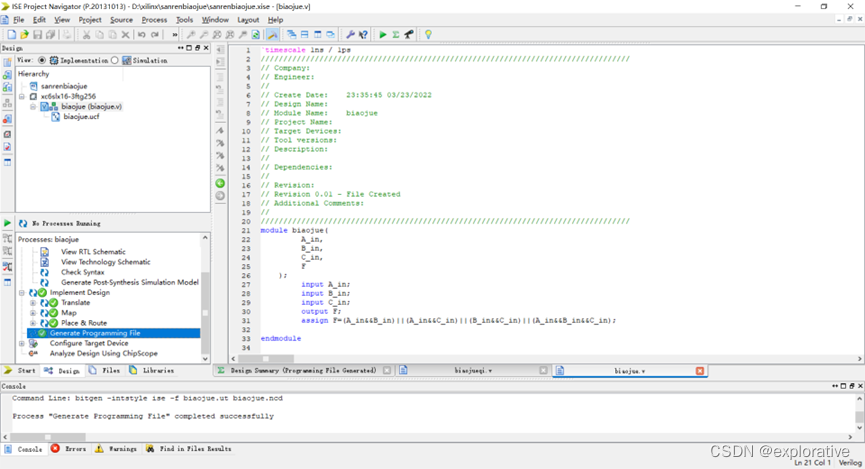

实验原理

在三人表决电路中,当表决某个提案时,多数人同意,则提案通过;反之,不通过。

假设 key_1,key_2,key_3 为三个裁判。同意用 1 表示,不同意用 0 表示;输出 LED0 为 1

的时候提案通过;反之,不通过。

1、真值表

A_in B_in C_in F

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

2、逻辑表达式

F=B_inC_in+A_inC_in+A_inB_in+A_inB_inC_in)

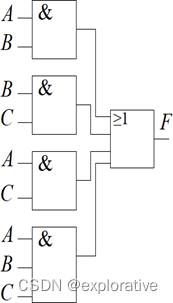

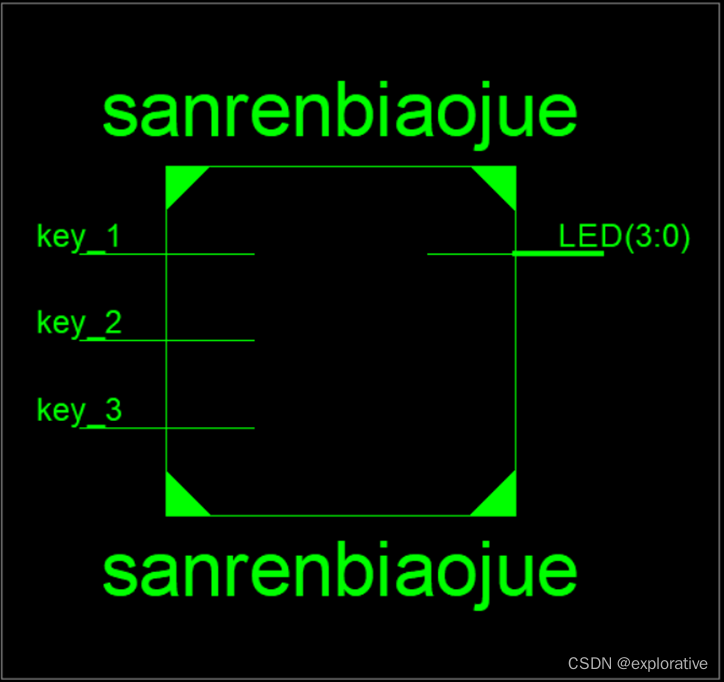

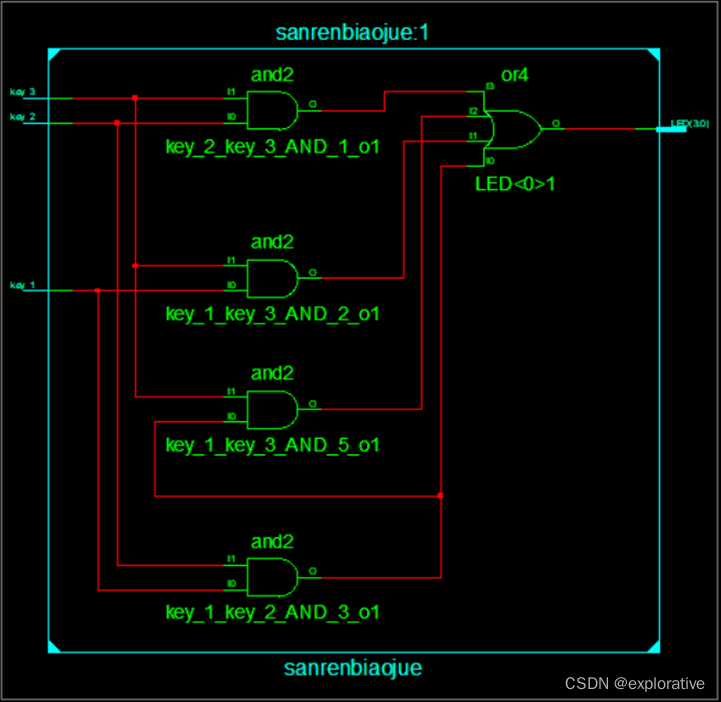

3、逻辑电路图

4、用 Verilog 语言写出该逻辑表达式

F=(B_in&&C_in)||(A_in&&C_in)||(A_in&&B_in)||(A_in&&B_in&&C_in);

在 verilog 语言中,&&代表逻辑与;||代表逻辑或

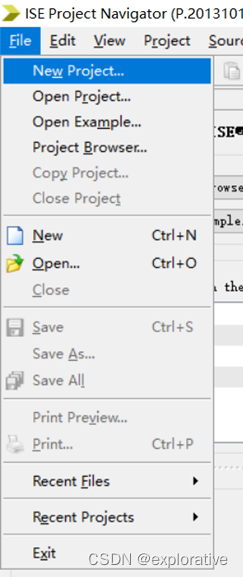

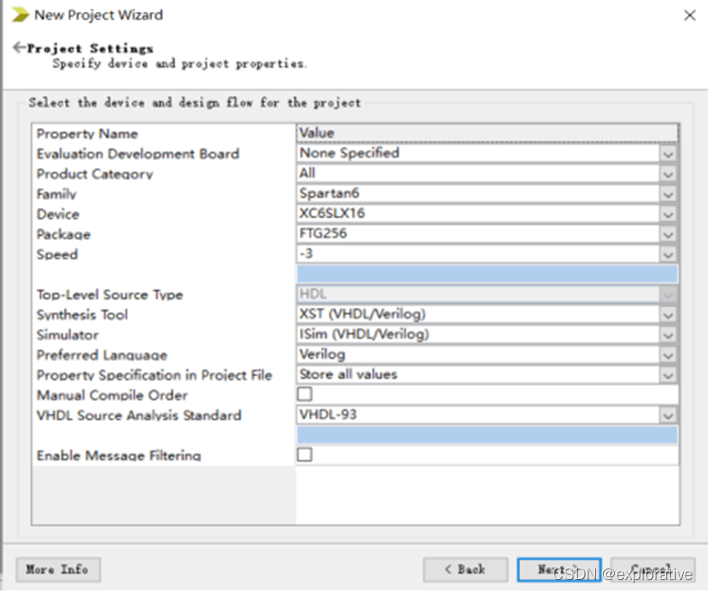

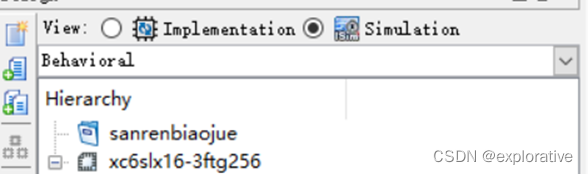

5、新建工程,将工程名命为:sanrenbiaojue

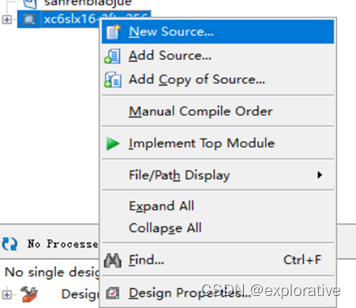

6、右击,选择 New Source

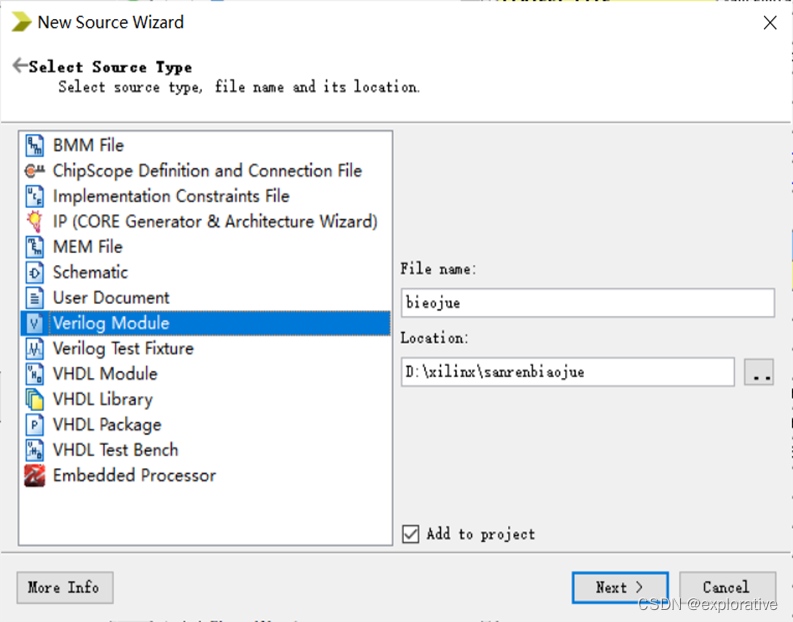

7、选择 Verilog Module,并命名为 biaojue

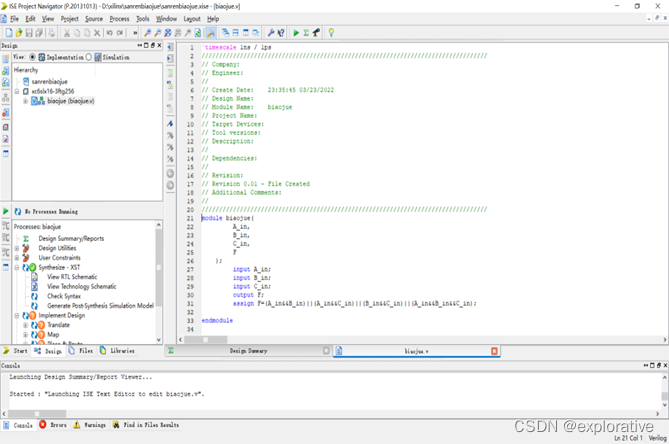

8、编写代码

9、运行该程序,检查 RTL 电路

双击放大如下:

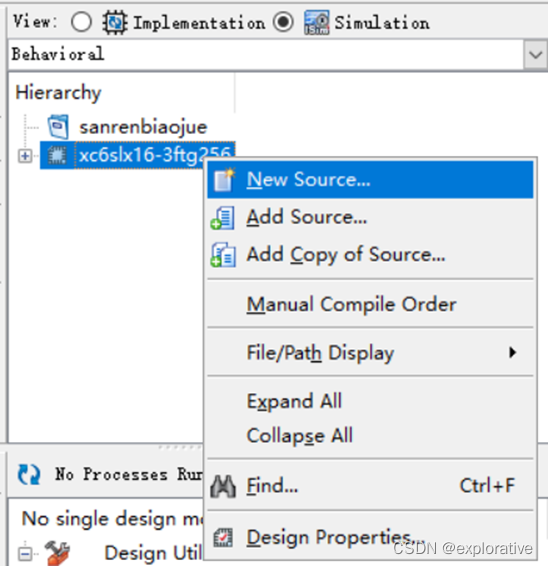

10、新建仿真文件

先点击 Simulation

右击,选择 New Source

选择 Verilog Test Fixture,命名为:sanrenbiaojue

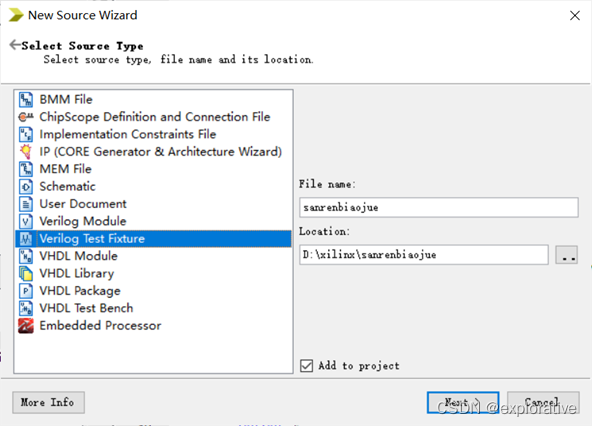

编写仿真代码

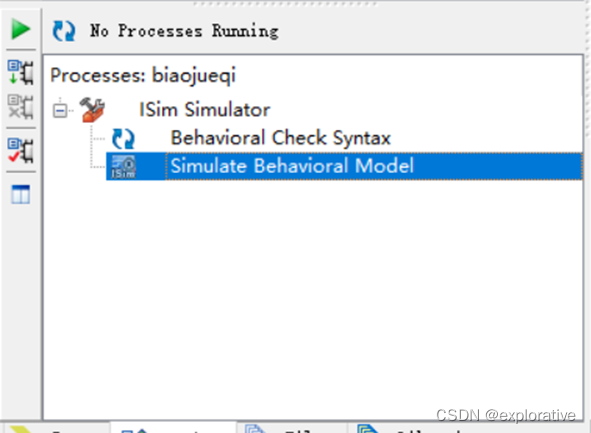

写完代码,双击 Simulate Behavioral Model

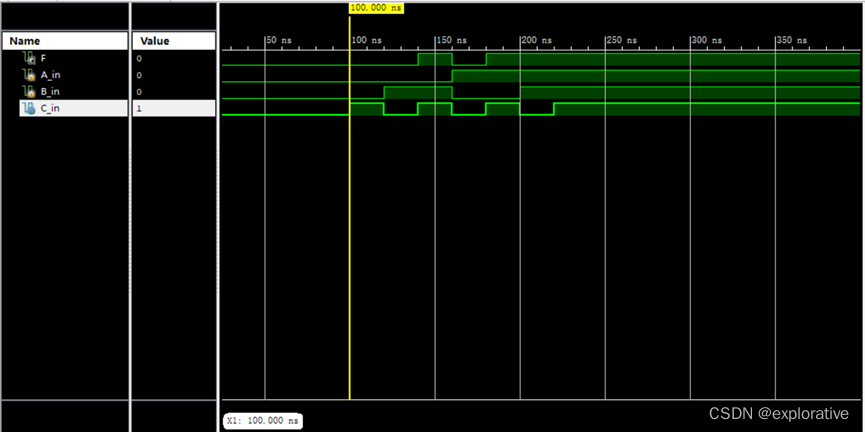

得到如下仿真波形图:

根据上面的波形图我们可以知道,

在 0-100ns 之间,A_in=0,B_in=0,C_in=0,F=0;

在 100ns 时,A_in=0,B_in=0,C_in=1,F=0;

在 120ns 时,A_in=0,B_in=1,C_in=0,F=0;

在 140ns 时,A_in=0,B_in=1,C_in=1,F=1;

在 160ns 时,A_in=1,B_in=0,C_in=0,F=0;

在 180ns 时,A_in=1,B_in=0,C_in=1,F=1;

在 200ns 时,A_in=1,B_in=1,C_in=0,F=1;

在 220ns 时,A_in=1,B_in=1,C_in=1,F=1;

在 220ns 之后一直保持 A_in=1,B_in=1,C_in=1,F=1

换言之,F 只有在 A_in,B_in,C_in,中有两个及两个以上的高电平时输出高电平;否

则,F 输出为低电平。

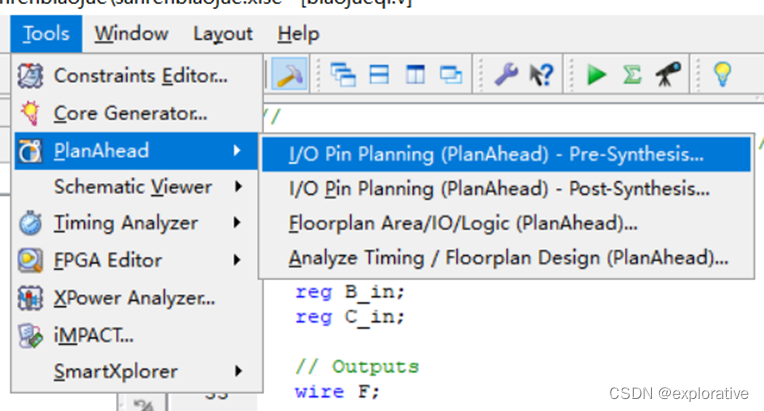

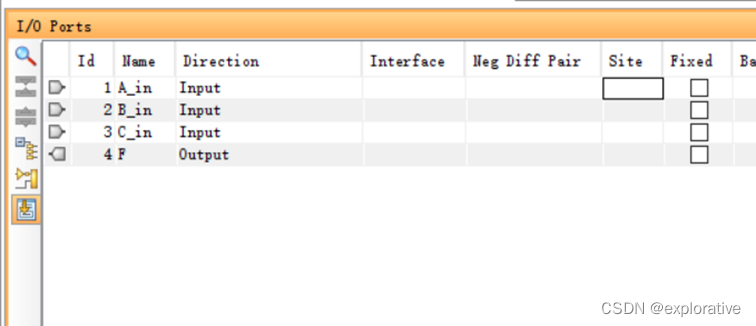

11、进行引脚标注

选择上方工具栏里面的 Tools,接下来点击 PlanAhead,然后选择第一个,如下图所示:

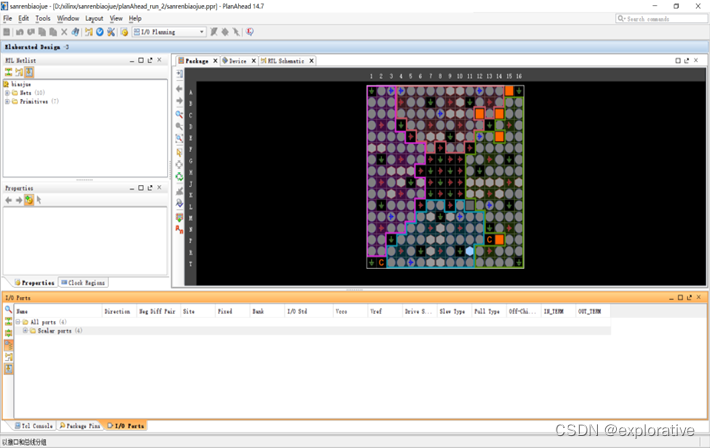

进入如下界面后,点击红色箭头所指的图标

在 Site 内输入相对应的引脚位置:

根据下表输入:

引脚名 引脚位置

A_in L5

B_in M3

C_in L4

F P6

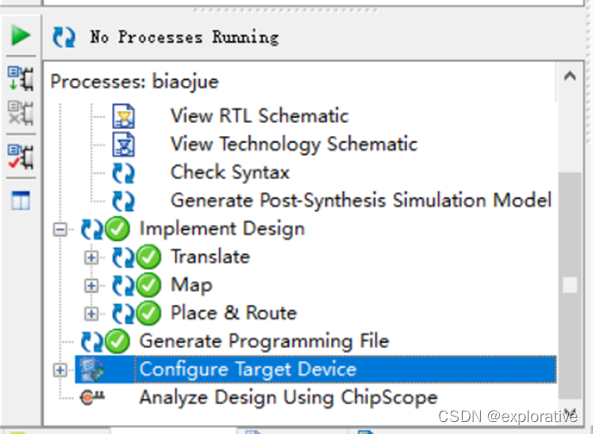

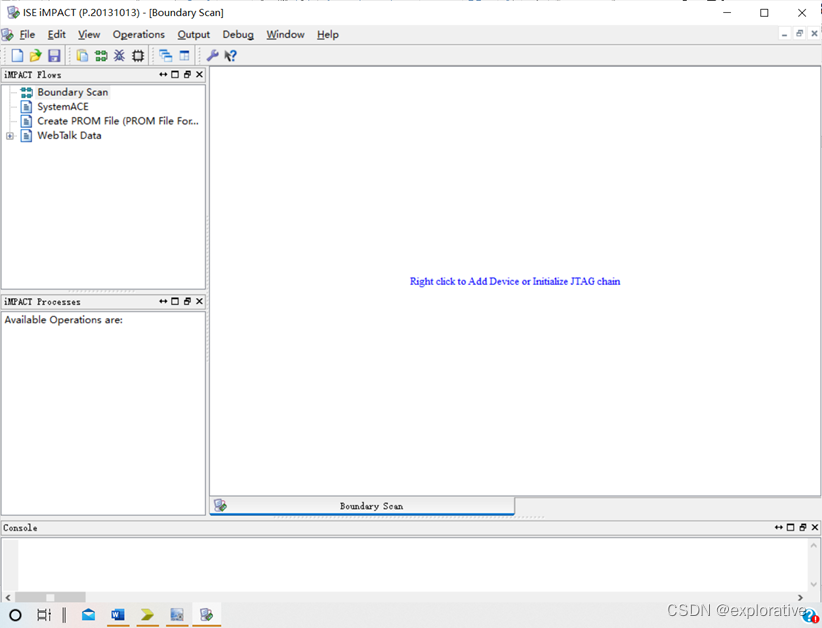

12、下载到开发板,进行实物实验

首先将开发板与电脑连接,再进行如下步骤

双击 Generate Programming File ,如果显示为绿色的勾勾

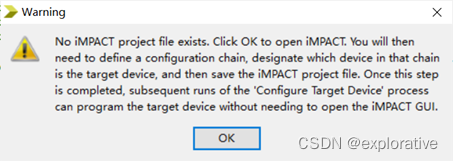

双击 Configure Target Device

点击 OK

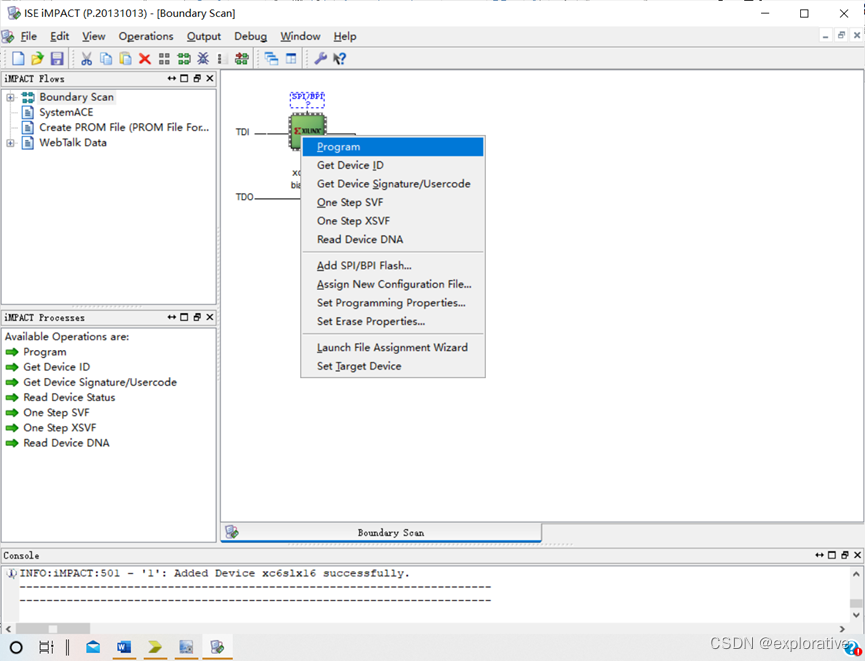

双击 Boundary Scan

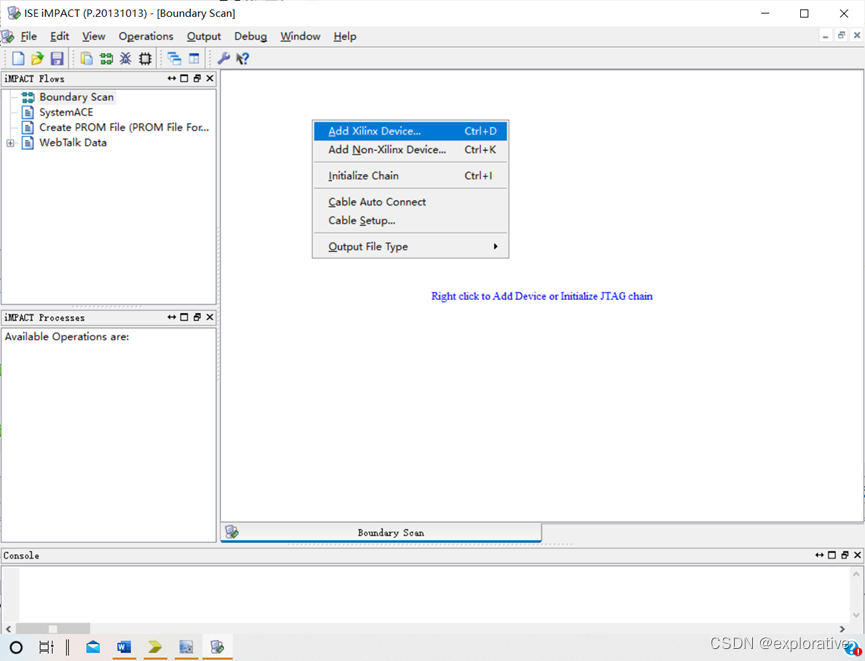

在白色区域内,右击,选择 Add Xilinx Device

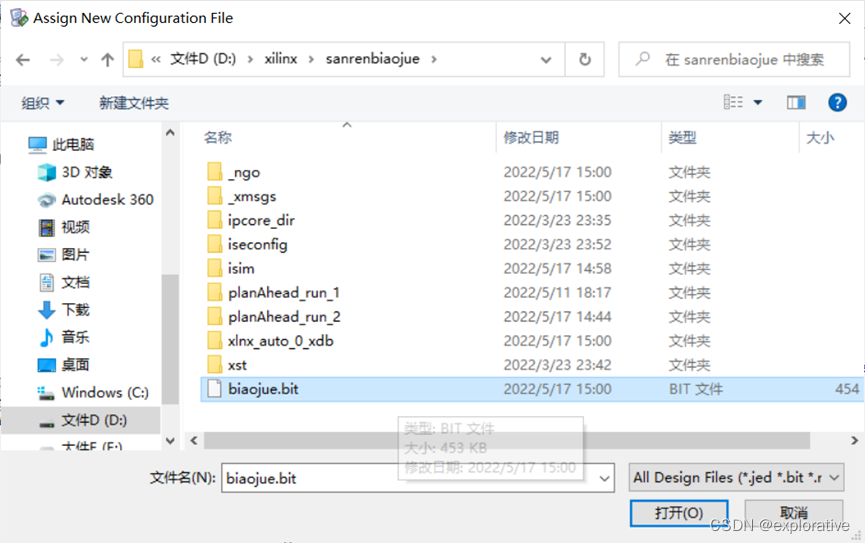

找到相对应的.bit 文件,打开

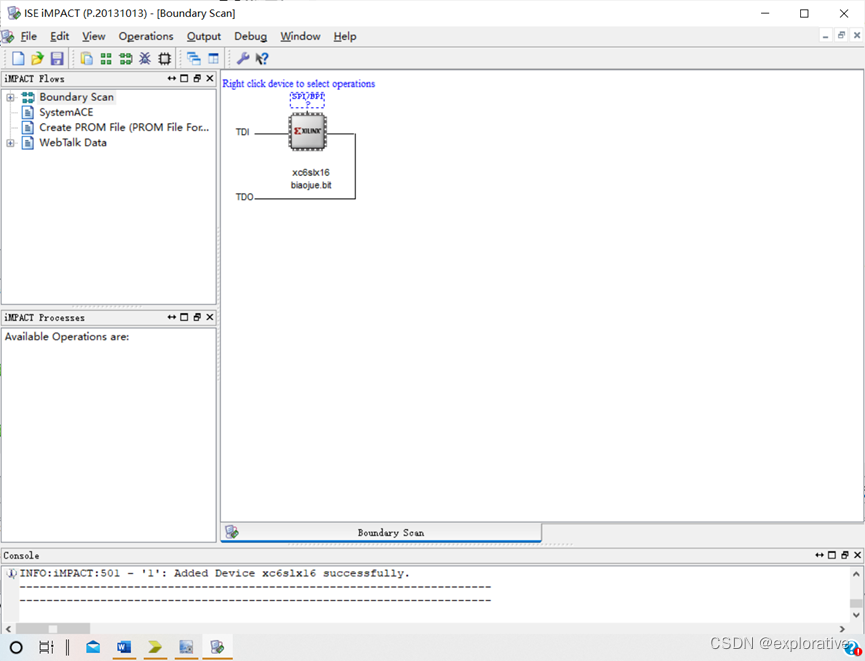

右击上述图片红色箭头指示的位置,选择 Program

六、实验结论

通过本次实验,我熟悉了 ISE 软件的基本操作,掌握了使用 Verilog HDL 描述电路功能

的编写,学习组合逻辑电路的设计仿真和测试,熟悉了 EDA 实验的基本流程。

七、实验相关代码及代码解释

module biaojue(

//变量名

A_in,

B_in,

C_in,

F

);

//定义输入输出变量

input A_in;

input B_in;

input C_in;

output F;//在这里将 F 默认定义为 wire 类型

assign F=(A_in&&B_in)||(A_in&&C_in)||(B_in&&C_in)||(A_in&&B_in&&C_in);//对

wire 类型变量 F 赋值用 assign 语句

endmodule

仿真测试代码:

module biaojueqi;

// Inputs

reg A_in;

reg B_in;

reg C_in;

// Outputs

wire F;

// Instantiate the Unit Under Test (UUT)

biaojue uut (

.A_in(A_in),

.B_in(B_in),

.C_in(C_in),

.F(F)

);

initial begin

// Initialize Inputs

A_in = 0;

B_in = 0;

C_in = 0;

// Wait 100 ns for global reset to finish

#100;

A_in = 1;

B_in = 0;

C_in = 0;

#20

A_in = 1;

B_in = 1;

C_in = 0;

#20

A_in = 0;

B_in = 1;

C_in = 0;

#20

A_in = 0;

B_in = 1;

C_in = 1;

// Add stimulus here

#20

A_in = 1;

B_in = 1;

C_in = 1;

#20

A_in = 0;

B_in = 0;

C_in = 1;

end

endmodule

396

396

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?