1 ARMv8-A

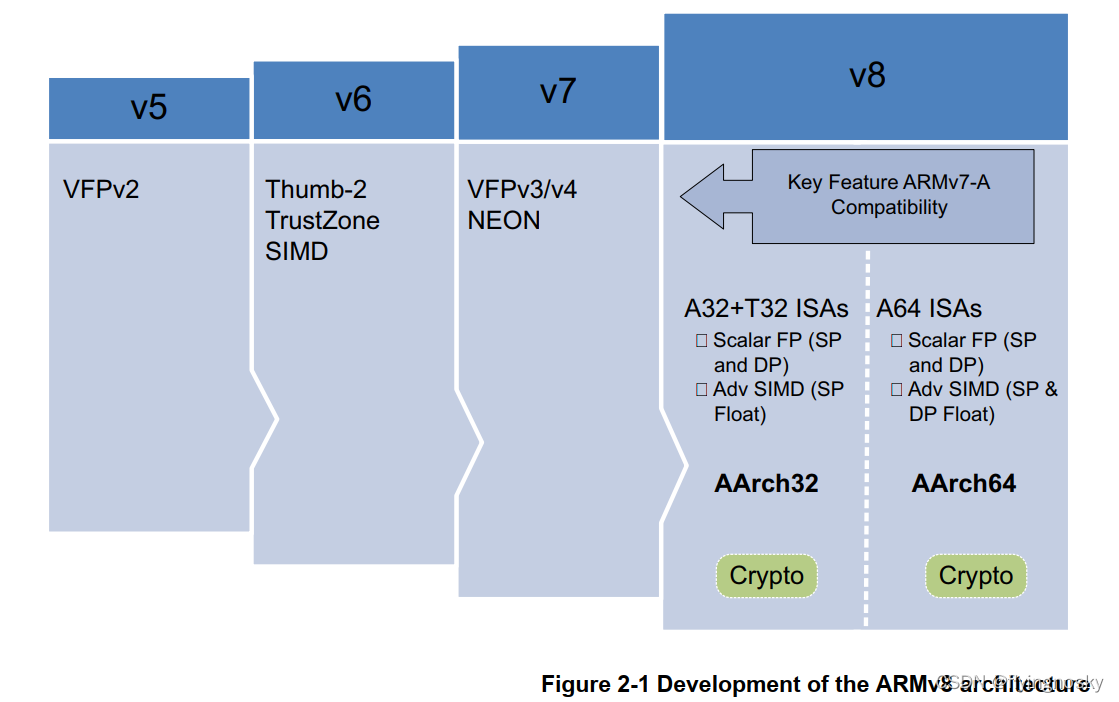

ARMv8-A架构是最新一代以应用profile为目标的ARM架构。名字ARMv8-A用于描述整个架构,现在包括32位和64位执行。它引入了用64位宽寄存器执行,但也保留了与ARMv7软件兼容的能力。

ARMv8-A架构引入了一些修改,它使能了设计的更高性能的处理器实现。

Large Physical Address: 它使能处理器超过4G物理内存的访问

64bit virtual Address: 它使能了超过4GB限制的虚拟内存。这对现代桌面和服务器软件使用内存映射的文件IO或解析地址非常重要。

Automatic Event signaling: 这使能了电源有效和高性能的spinlock。

Larger Register Files: 31个64位通用寄存器用于提升性能和减少栈的使用。

Efficient 64bit immediate generation:需要更少的文字池。

Large PC-relative addressing range:对共享库和位置无关的执行文件中有效数据的 A+/-4GB地址范围。

Additional 16KB和4KB转换粒度:这减少了TLB miss率和页walk的深度。

New execption level: 这减少了OS和hypervisor的软件复杂度。

Effient cache management: 用户空间的CACHE操作可以改善动态代码产生效率。使用Data Cache Zero指令快速的清除数据CACHE。

Hardware-accelerated cryptography: 提供3倍或10倍的软件加密性能。这对小粒度的解密和加密太小不能有效的进行硬件加速特别有用,比如https。

Load-Acquire, Stronore-Release instructions: 为C++11,C11,和Java内存模型设计。它们通过减少明显的内存barrier指令来改善线程安全的代码。

NEON double-precision floating-point advanced SIMD: 这使能SMID来应用于更宽的一组算法,如科学计算,HPC和超算。

2 ARMv8-A处理器属性

下表比较了ARMv8-A架构实现的处理器属性:

| processor | ||

| Cortex-A53 | Cortex-A57 | |

| Release data | July 2014 | January 2015 |

| 典型时钟速率 | 2GHZ 28nm | 1.5~2.5GHZ 20nm |

| 执行顺序 | 有序 | 无序,预测发出,超级标量 |

| core核数 | 1~4 | 1~4 |

| 集成最大吞吐量 | 2.3MIPS/MHZ | 4.1~4.76MIPS/MHZ |

| 浮点单元 | Yes | Yes |

| 半精度 | Yes | Yes |

| 硬件除法 | Yes | Yes |

| 融合乘法积累 | Yes | Yes |

| 流水线级数 | 8 | 15+ |

| 返回栈的数目 | 4 | 8 |

| GIC | 外部 | 外部 |

| AMBA 接口 | 64位I/F AMBA 4 | 128位I/F AMBA 4 |

| L1 CACHE大小(指令) | 8KB~64KB | 48KB |

| L1 CACHE结构(指令) | 2路组相连 | 2路组相连 |

| L1 CACHE大小(数据) | 128KB~2MB | 32KB |

| L1 CACHE结构(数据) | 4路组相连 | 2路组相连 |

| L2 CACHE | 可选 | 集成 |

| L2 CACHE SIZE | 128KB~2MB | 512KB~2MB |

| L2 CACHE 结构体 | 16路组相连 | 16路组相连 |

| 主TLB项 | 512 | 1024 |

| uTLB项 | 10 | 48 指令 32 数据 |

2.1 ARMv8处理器

本节描述了实现ARMv8-A架构的每个处理器。它仅给出了每种情况的通用描述。对于每个处理器的更多特殊情况,看上表。

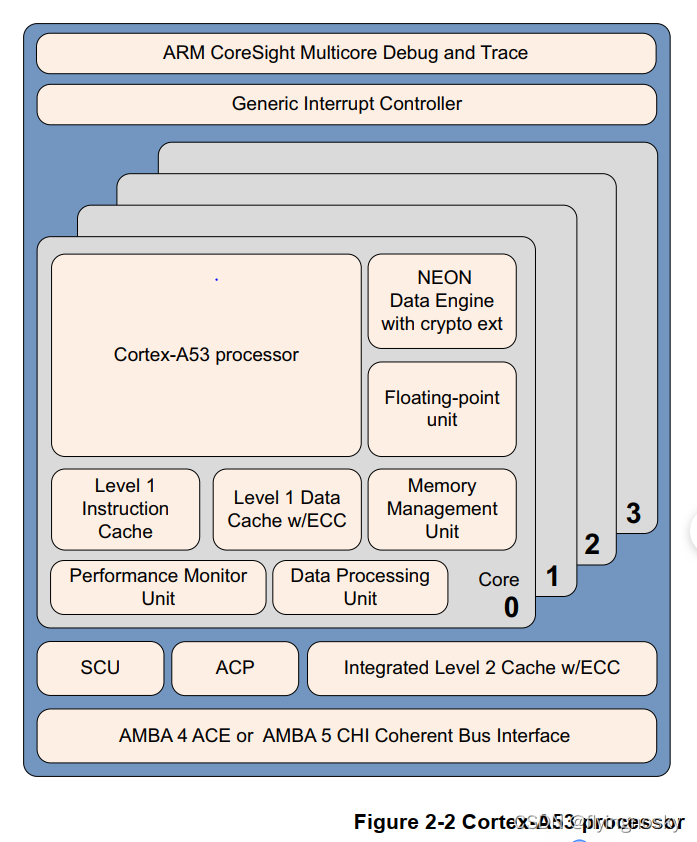

Cortex-A53处理器

Cortex-A53处理器是中等范围,在一个cluster中包含1~4个core的低功耗处理器,每个core带L1 CACHE子系统,可选的集成GICv3/4接口,和可选的L2 cache控制器。

Cortex-A53处理器是一个极度电源效率的处理器,它支持32位和64位代码的能力。它传递明显的性能高于Cortex-A7处理器。它具有部署为一个独立的应用处理器的能力,或与Cortex-A57处理器一起组成大小核配置来优化性能,规模和电源效率。

Corext-A53具有如下特性:

(1)顺序执行,8级流水线。

(2)通过使用层级时钟门限,电源域,和更先进的保留模式实现低功耗。

(3)增加了双端能力,如执行资源的复制,双指令的解码。

(4)电源优化的L2 cache设计,它具有更低的时延,让性能与效率的平衡。

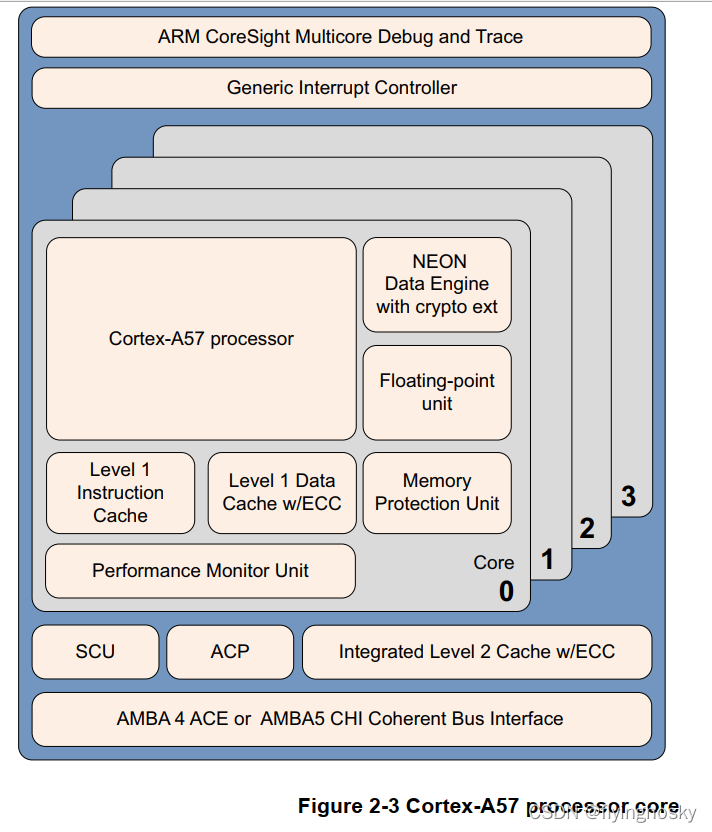

Cortex-A57处理器

Cortex-A57的目标为移动电话和企业计算应用包括计算型64位应用如高端计算机,桌面和服务器产品。可以用它与Cortex-A53处理器一起组成大小核配置来实现大规模性能和有效的能源应用。

Cortex-A57处理器提供与其他处理器的cache一致性的互操作性,包括用于GPU计算的ARM Mali家族的GPU和为高性能企业应用提供可选的可靠性和规模性的特征。它提供了明显更高于ARMv7 Cortex-A15更高的性能,且更高的电源效率级别。包含扩展的加密特性,提供了10倍于之前代处理器的加密算法。

Cortex-A57处理器完全实现了ARMv8-A架构。它在一个cluster中实现了1~4个处理器的多核操作。多个一致性SMP cluste通过AMBA5 CHI或AMBA 4 ACE技术实现。可通过CoreSight技术让debug和trace有效。

Cortex-A57处理器具有如下特征:

(1)乱序执行,15+流水线。

(2)节能技术包括路预测,tag减少,和cache查找。

(3)通过执行资源的复制来增加最大的指令吞吐量。本地解码,3-wide解码带宽来实现电源优化指令。

(4)L2 cache设计的性能使能在一个cluster中超过1个core来同时访问L2。

913

913

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?