3 cluster中多核cache一致性

一致性意味着在系统中的所有处理器或总线master对共享内存有相同的视角。它意味着对core中cache中数据的修改对其他core也可见,让其他core不能看到其他无效或旧的数据拷贝。不缓存可以简单的解决这个问题,即禁用共用内存位置的缓存,但这通常会以性能降低为代价。

软件管理一致性:软件管理一致性是一个更通用的处理数据共享的方法。数据被缓存,但软件,通常为设备驱动,必须清脏数据或无效化cache中的数据。这需要时间,也增加了软件的复杂性,当存在大量的共享时也会减少性能。

硬件管理一致性:硬件维护cluster中level1数据缓存的一致性。当上电时core自动参与一致性方案,该core有自己的D cache和MMU使能,地址被标记为一致性的。

但是cache一致性逻辑不能维护数据和指令cache之间的一致性。

在ARMv8-A架构和相关的实现中,更可能由硬件管理一致性方案。这确保在硬件一致性管理系统中任何被标记为shareable的数据可以被其他core和shareability域中的其他总线master看到相同的值。这需要对内部互连和cluster增加硬件复杂性,但简化了软件且使应用不需要使用软件一致性。

这里有一些cache一致性方案运行的标准方法。ARMv8处理器使用MOESI协议。ARMv8处理器也可以与AMBA 5 CHI内部互连,该cache一致性协议也与MOESI类似。

依赖于使用哪个协议,SCU使cache中的cache line有如下属性:M(Modified),O(Owned),E(Exclusive),S(Shared),I(Invalid)。它们描述如下:

Modified: cache line的最新版本在cache中。在其他cache中并没有内存的拷贝。Cache line中的内容不再与主内一致。

Owned: 该状态描述了脏的cache line且可能存在多个cache中。在owned状态的cache line保持着最近,正确的数据拷贝。仅有一个core可能保持owner状态。其他core可以保持数据在shared状态。

Exclusive: 在cache中cache line存在且与主内一致。在其他cache中没有内存的其他拷贝。

Shared: 在cache中cache line存在但不一定与主内一致,给出了允许脏cache line的Owned被拷贝到shared cache line中。但是,它存在最新版本的数据。数据的拷贝也可以在其他cache中。

Invalid: cache line无效。

此协议的标准实现需要遵守如下规则:

- 如果cache line处于M或E状态时,只能发出写操作。如果它为S状态时,所有其他缓存的拷贝必须先无效化。写操作会将cache line改变为M状态。

- cache可以在任何时候丢弃一个共享的cache line,将其变为无效状态。M状态的cache line首先被回写。

- 当其他cache在读取该cache line时,存在E状态的cache line的CACHE必须将cache line变成共享状态。

- 共享状态可能不准确。如果一个cache丢弃一个共享的cache line,其他cache可能没有意识到它现在将cache line变为E状态。

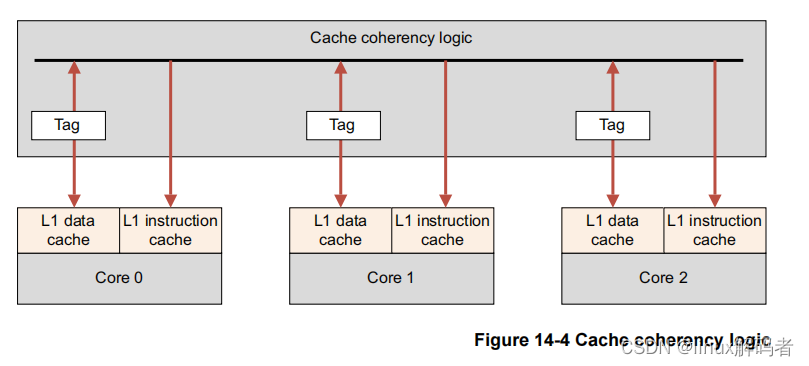

处理器cluster包含SCU,该SCU包含存储在独立L1数据cache中tag的多个拷贝。因此cache一致性逻辑:

- 维护L1数据cache间的一致性;

- 仲裁L2接口的访问,对指令和数据;

- 由多个tag RAM来跟踪在每个core的数据中分配的是什么数据;

上图中的每个CORE都由自己的数据和指令cache。cache一致性逻辑包含来自D cache的本地拷贝。但是指令cache不参与一致性。这是2路数据cache和一致性逻辑之间的通信。

ARM多core处理器也实现一些优化,拷贝干净数据,将脏数据直接放入L1 cache而不需要访问和等待外部内存。这些活动由多核系统中的SCU处理。

多核计数的重要方面如下:

3.1 SCU

SCU维护每个core的L1数据cache的一致性并负责管理下列内联行为:

- 仲裁

- 通信

- Cache to cache和系统内存转换

处理器也将这些能力暴露给其他系统加速器和非cache的DMA外设来增加性能和减少系统级的功耗。系统一致性也在维护每个OS驱动软件一致性时减少软件复杂性。

每个core可以单独配置参与或不参与数据cache一致性管理方案。在处理器中的SCU设备自动维护在cluster中core间的level1 数据cache一致性。

因为执行的代码修改得比较少,这个功能并没有扩展到L1指令cache。通过MOESI协议实现一致性管理,被优化来减少外部内存的访问。为了对内存访问一致性的管理,所有下列必须符合:

- SCU通过位于私有内存区域的控制寄存器来使能。SCU有配置的访问控制,严格控制哪些处理器可以配置它;

- MMU被使能;

- 页被标记为normal shareable访问,cache策略为write-back, write-allocate。设备和严时序的内存不会cacheable,从core的角度write-through cache就像uncached内存。

SCU只能委会单个cluster之间的一致性。如果有其他的处理器或其他总线master在系统中,当在多核之间有共享内存时,需要明确的软件同步。

3.2 加速器一致性端口

SCU中AMBA 4 AXI兼容slave接口为直接与ARMv8处理器连接的master提供了内部互联点:

- 接口支持所有标准的读和写事务而不需要其他一致性的要求。但是,任何对SCU相互作用的内存一致性区域的读事务用来测试是否信息已经被保存在L1 cache中。

- SCU强制写一致性在写被发往内存系统中,也可能分配到L2 cache中,将电源和性能直接移除片下内存。

3.3 cluster之间的cache一致性

前面描述了在一个cluster中多个处理器共享数据的cache是如何维护的。系统也包含在cluser之间维护一致性的硬件,它们通过处理shareable数据事务和广播barrier和维护指令。cluster可以被动态的添加或移除一致性管理,比如,当整个cluster,包含L2 cache,被下电。操作系统可以通过内置的PMU监控一致性内联的活动。

3.4 域

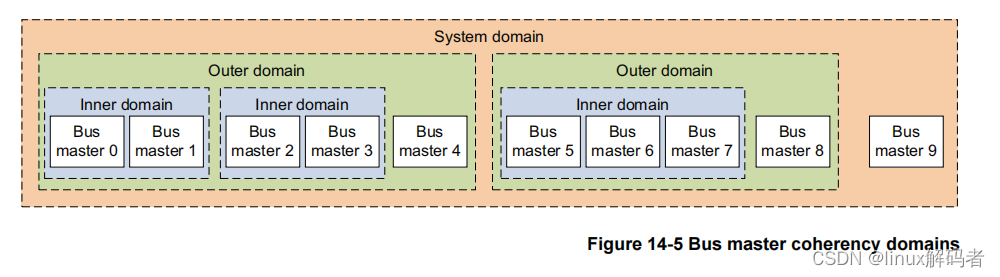

在ARMv8-A架构中,术语domain用于表示主要总线master的集合。domain决定了哪些master被窥探。Snooping用于检查master的cache来看是否要求的位置被存储。有四种定义的域类型:

- Non-shareable

- Inner Shareable

- Outer shareable

- System

通常运行在相同的操作系统下的master在相同的inner shareable域,共享cacheable数据但并不临近的master在相同的outer shareable域。在相同的inner shareable域的master必须也在相同的outer shareable域。内存访问的域选择是通过页表项来控制的。

113

113

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?