对于现代复杂硬件设计系统而言,系统可能设计多个子系统,一个子系统对应一个PCB单板;一个PCB单板包含多个独立模块,一个独立模块完成一套整体的业务。一个独立模块内部包含多个小的子系统或者IP核。这样一套复杂的系统,某一项业务夸多个大的子系统,数据之间进行交换,这样对于系统级别的数据交互和通信方式直接会影响到系统级别的整体性能能。

比方说1:对于庞大的接入网系统而言,一套系统设备一般包含多多个子单板,各个子单板完成特定的业务功能模块。每一块单板上面有划分为控制CPU和转发类芯片模块,为了实现两者之间的通信还需要单独配备转发类芯片。对于一个CPU或者转发类芯片内部有划分各个不同的子系统模块,比方说CPU内部包含了多核设备,同时包含了网络基本接收模块等。当然随着IC工艺和设计工艺的逐步提高,很多PCB级别的模块组件被集成到SOC片内部。

比方说2:对于服务器端的AI设备卡而言,对于一套复杂的集成环境,一般存在一整套的设备集群。对于每一个独立的服务器而言,设备内部包含控制CPU中心和多个AI设备卡。对于设备卡而言,系统内部又包含了编解码,AI NN和控制MCU等小IP模块。

进程与线程同步互斥

1. 多进程之间的数据的方式:管道pipe、命名管道FIFO、消息队列MessageQueue、共享存储SharedMemory、信号量Semaphore、套接字Socket和信号 ( sinal )

2. 线程间的通信目的主要是用于线程同步,所以线程没有像进程通信中的用于数据交换的通信机制。

锁机制:包括互斥锁、条件变量、读写锁、自旋锁

信号量机制(Semaphore):包括无名线程信号量和命名线程信号量

信号机制(Signal):类似进程间的信号处理

3. Linux内核自旋锁使用对比:

| 接口API的类型 | spinlock中的定义 | raw_spinlock的定义 |

| spinlock之后这个核不能进行调度了,但这个核上的中断还可能来 | spin_lock | raw_spin_lock |

| 获取指定的spin lock同时disable本CPU中断,如果资源在中断中处理函数中也是使用的,使用这个借口哦 | spin_lock_irq | raw_spin_lock_irq |

| 保存当前中断寄存器flag状态,关中断,进入临界区,在退出临界区时,把保存的中断状态写回到中断寄存器,不确定中断是否肯定开的情况下使用这个接口 | spin_lock_irqsave | raw_spin_lock_irqsave |

| 获取指定的spin lock同时disable本CPU的bottom half | spin_lock_bh | raw_spin_lock_bh |

| 尝试去获取spin lock,如果失败,不会spin,而是返回非零值 | spin_trylock | raw_spin_trylock |

1. 系统级

1.1. 高速

对于系统级别,为了能够是多个设备集合在一起,一般使用高速serdes或者高速网络接口实现多个子系统时间的级联。

1.2. 低速

一般可以使用UART、I2C等低速接口进行连接

2. 单板级别

单板级别可以使用网络芯片或者单板级别的serdes进行连接传输高速数据,PCB信号线实现模块之间的控制信号连接。

3. SOC级别

多处理器多内核或者多IP进行工作协同处理的时候,需要多核之间进行数据沟通交互协同和消息(信号沟通)。对于同一个芯片多核紧凑型的CPU处理器,锁这种机制就利用了特定的汇编指令实现了多核之间的同步,使得多核在同一时间只能有一个核可以对某一块数据区域进行修改编码。当然锁也可以防护同一个内核多个不同线程之间的数据共用,这个这里不做过多的说明。除了以上的特殊情况,多核之间数据交互目前主要通过多核消息、中断体系网络和硬件信号完成。

3.1. 消息

这种消息类似socket套接字编程,在复杂系统内部我们通过一个转发类型的芯片(NOC)实现多核之间数据互通工作。具体实现方式是在内部网络中维护一个二层VLAN域网络,对各个IP和定义格子的MAC地址和所属VLAN域,在进行多核数据交互时只需要当前和发送带有目的MAC地址的消息到交换芯片就可以将数据转发到芯片核内部其他IP。

3.2. 中断网络(+内存空间)

中断网络这种数据信息的互通工作实际开发过程中情况太多了(中断+DDR),开始最原始的中断消息互通是通过GIC这种中断网络将SOC上面的硬件模块和ARM核链接起来。这种类型的中断信号通过中断控制器调度以后将中断信号给到ARM内核,具体数据处理这一块不同类型的外部核有不同类型的驱动动与之对应,完成相应的外部设备的数据处理。这种类型的中断信号只是告知不包含数据,具体数据决定于实际的硬件驱动,且这种信号是由外部硬件到内部ARM核的单向通信。

另外一种中断网络类似于消息队列的形式(中断+ringbuf或者MailBox),只是通过硬件类维护,使用者将消息数据添加到消息队列中,只要是消息队列数据不空,这种类型的硬件消息队列IP就会发送中断给另外一个与之对应的IP核,这个样子就会完成数据互通工作。

除了这种方式之外,还有一种中中断消息机制是利用中断实际只用过程只有1bit这个特性,将寄存器的剩余bit数据留给读写地址或者是一个函数指针。当然也可以在中断寄存器之上配套给定几个数据寄存器用来保存信息配合中断寄存器完成数据地址或者函数指针的交互工作。

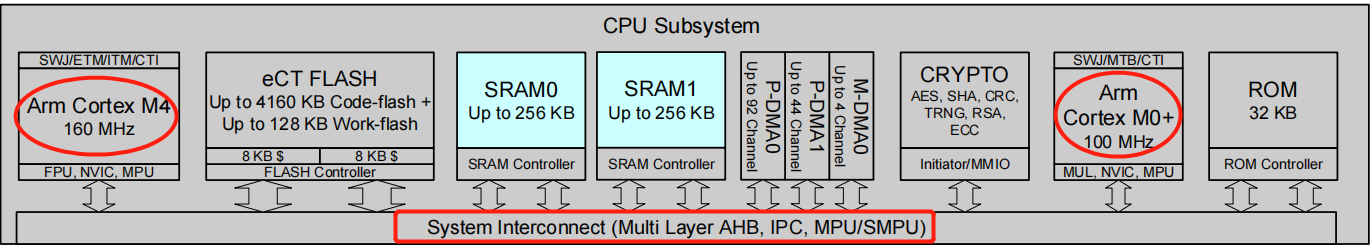

现在很多的芯片都会几个core核,有的用的是Cortex M0+、M4、M7、A53、A73等等,有的是2核、3核、4核甚至6核8核,不同的核的主频支持度不一样,适用的具体应用场景也不同。

那么核间通信Inter-processor communication即IPC,一般作为核间通信使用。

可以看到处理器A和处理器B在进行IPC通信的时候,会用到Channel和Interrupt两个结构体,而且这是是共享的,关于共享可以从AHB总线层面和存储结构体两个层面来理解。

3.3. 硬件信号

通过硬件信号这种设计和中断类似,不同的是这里发出的直接是一个高或者低电平信号通知下一个IP核模块,相应的IP核收到信号消息以后一般是直接完成一系列硬件的操作动作最终结束。比方说在项目中可能有这么一种情况,一个核将数据准备好以后(硬件的动作),然后这个核硬件层面可以拉一个信号给DMA让其完成数据搬运到另外一个内存区域中。

3.4. UART等低速接口

对于性能要求不是特别高的设备,可以在内部集成低速的UART串口完成多核之间的数据通信。

4. 系统性能

对于产品而言,系统级别的性能才是有意义的。多子系统构成的数据处理庞大系统,多个系统之间进行数据处理串行执行,中间通过buf缓冲完成数据的堆叠累加。系统第一次开始运行时间是所有数据处理环节时间和,当多个任务开始并行的时候,系统性能和buf空间和设备链路上处理数据最慢的环节有关系。也就是说多个环节并行处理,系统性能决定于所有环节中最慢的那个处理环节。这一点计算方式是和功耗不同的,功耗总值为各个模块功耗之和。

- 对于整体流程而言,可以通过优化处理流程,流程环节减少,将串行处理流程设计成并行处理流程,这样可以在整体处理流程上面提升系统处理性能。

- 某一个具体子流程常见一些技术手段有,多进程并行、提升频率电压、软件流程硬化、软件流程优化和软件算法优化等。提升频率电压可以提高核的运行速率。而使用多进程或者多核的方式是简单的堆人方式来提升效率。软件方面的提升就是算法和处理流程提升,或者直接软件硬化方式来完成。

- 子流程中某一个数据处理环节可以使用帮徒的方式,设置影子寄存器、DMA数据存取和DMA数据预取、乒乓数据缓冲等方式讲需要处理的数据提前准备好。前面三个是方向是为数据处理提前准备好基本的材料,相当于给配一个小工,这也与当前内存IO限制系统处理性能的情况想匹配。

技术无大小,技术无高低。

4406

4406

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?