CPU体系结构

CPU(Central Processing Unit,中央处理单元)也称为微处理器(Microprocessor).

cpu是计算机的核心部件,主要由运算器、控制器、寄存器组和内部总线等构成。

CPU中指令的执行过程有3步骤:取指令,取操作数,执行操作。

CPU的主要性能指标

(1)主频

主频也叫时钟频率,单位是MHz(或GHz),用来表示CPU的运算和处理数据的速度。

主频仅仅只是CPU性能的一个方面,不能代表CPU的整体运算能力,但是人们还是习惯于用主频来衡量CPU的运算速度。

(2)位和字长

位:计算机中采用二进制代码来表示数据,代码只有0和1两种。无论是0还是1,在CPU中都是1"位"。

字长:CPU在单位时间内能一次处理的二进制数的位数称为字长。通常一次处理16bit数据的CPU就叫做16位的CPU。

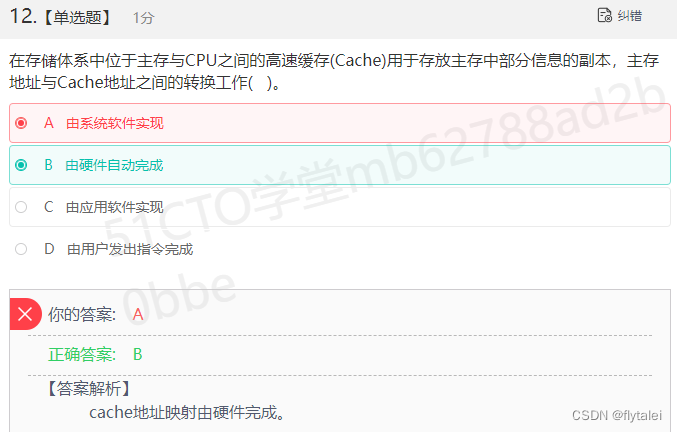

(3)缓存

缓存是位于CPU和内存之间的高速存储器,通常其容量比内存小,但速度却比内存快,甚至接近CPU的工作速度。

缓存主要是为了解决CPU运行速度与内存读写速度之间不匹配的问题。

缓存容量的大小是CPU性能的重要指标之一。缓存的结构和大小对CPU速度的影响非常大。

通过CPU有三级缓存:一级缓存、二级缓存和三级缓存,用于解决CPU和内存的速度不匹配的问题。

一级缓存(L1 Cache)是CPU的第一层高速缓存,分为数据缓存和指令缓存。

受制于CPU的面积,L1通常很小。

二级缓存(L2 Cache)是CPU的第二层高速缓存,按芯片所处的位置分为内部和外部两种。

内部的芯片二级缓存运行速度与主频接近,而外部芯片的二级缓存运行速度则只有主频的50%左右。

L2高速缓存容量也会影响CPU的性能,理论上芯片的容量是越大越好,但实际上会综合考虑成本与性能等各种因素,CPU的L2高速缓存一般是2~4MB。

三级缓存(L3 Cache)的作用是进一步降低内存延迟,提升大数据量计算时处理器的性能。

因此在数值计算领域的服务器CPU上增加L3缓存可以在性能方面获得显著的效果。

控制器组成

控制器由程序计数器PC、指令寄存器IR、地址寄存器AR、数据寄存器DR、指令译码器等组成。

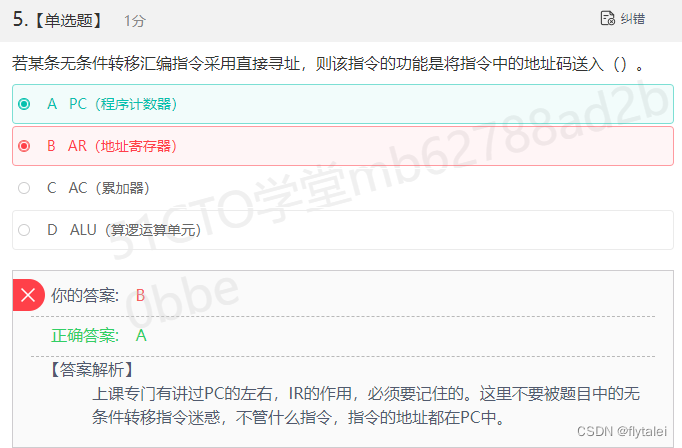

(1)程序计数器PC(Program Counter):指向下一条指令的地址。

(2)指令寄存器IR(Instruction address register):保存当前正在执行的这条指令的代码。

(3)地址寄存器AR(Address Register):用于存放CPU当前访问的内存单元地址。

(4)数据寄存器DR(Data Register):用于暂存从内存储器中读出或写入的指令或数据。

(5)指令译码器:用于对获取的指令进行译码。

运算器组成

运算器由算术逻辑单元ALU、通用寄存器、数据暂存器等组成、程序状态字寄存器,它接收从控制器送来的命令并执行相应的动作,主要

负责对数据的加工和处理。

(1)算术逻辑单元ALU:用于进行各种算术逻辑运算。

(2)通用寄存器:用来存放操作数、中间结果和各种地址信息的一系列存储单元。

常见通用寄存器有:

数据寄存器

AX: Accumulator Register,累加寄存器,算术运算的主要寄存器;

BX: Base Register,基址寄存器;

CX: Count Register,计数寄存器,串操作、循环控制的计数器;

(3)数据暂存器:用来暂存从主存储器读出的数据,这个数据不能存放在通用寄存器中,否则会破坏其原有的内容。

(4)程序状态字寄存器PSW:用于保留与算术逻辑运算指令或测试指令的结果对应的各种状态信息。

移位器在ALU输出端用暂存器来存放运算结果,具有对运算结果进行移位运算的功能。

CPU指令的执行

计算机中的一条指令就是机器语言的一个语句,由一组二进制代码来表示。

一条指令由两部分构成:操作码和地址码。

CPU中指令的执行过程分为以下3个步骤:

(1)取指令。

(2)取操作数。

(3)执行操作。

CPU指令系统

CPU根据所使用的指令集可以分为CISC指令集和RISC指令集两种。

(1)复杂指令集(Complex Instruction Set Computer, CISC)

处理器中不仅程序的各条指令是顺序串行执行的,而且每条指令中的各个操作也是顺序串行执行的。

计算机各部分的利用率低,执行速度相对较慢。为了能兼容以前开发的各类应用程序,

现在还在继续使用这种结构。

(2)精简指令集(Reduced Instruction Set Computer, RISC)

技术是在CISC指令系统基础上发展起来的,实际上CPU执行程序时,

各种指令的使用频率非常悬殊,使用频率最高的指令往往是些非常简单的指令。

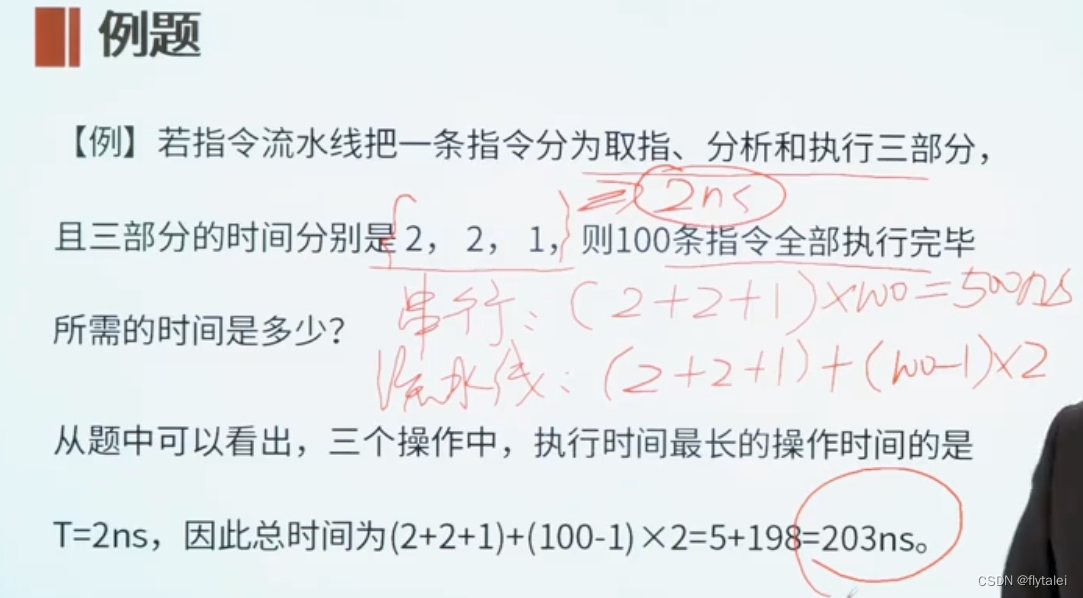

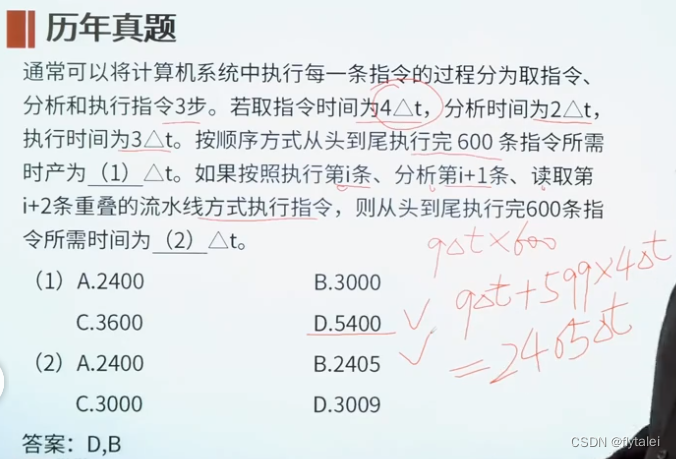

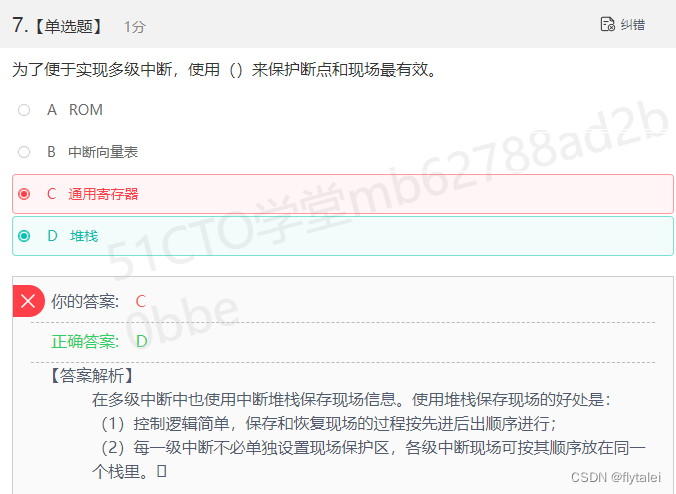

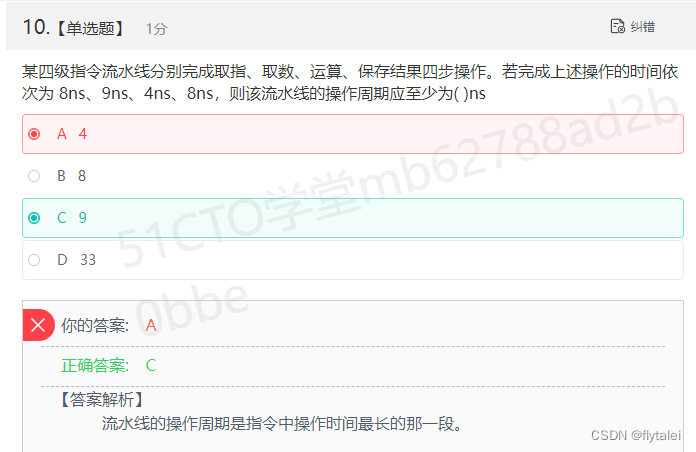

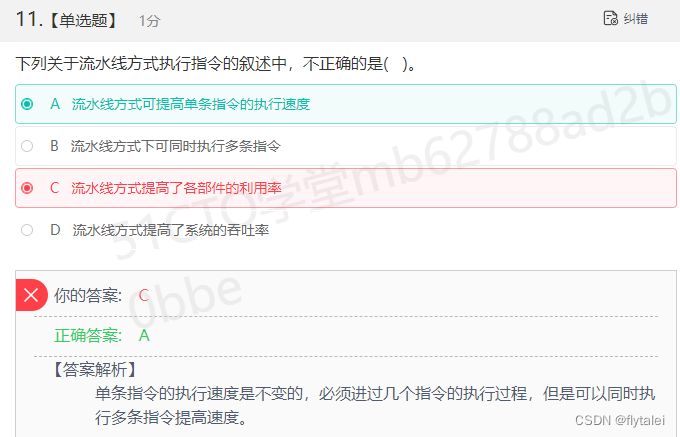

流水线技术

相关知识点:流水线技术,流水线的效率,加速比等计算。

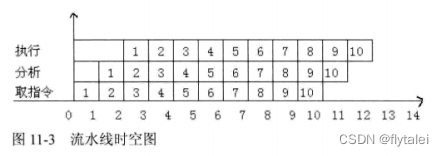

流水线(Pipe line)

是一种将指令分解为多个小的步骤,并让几条不同指令的各个操作步骤重叠,

从而实现几条指令并行处理,以加速程序运行速度的技术。

一条指令至少有"取指"、"分析"、"执行"这三个步骤

其实这三个步骤就对应CPU的三个部件,如果串行执行这三个步骤的话,

就是指令过来"取指部件先取指令"==>"然后分析部件再分析"==>"最后执行部件再执行指令"

此时

第一个时钟周期,取指完成后取指部件就等待分析部件去分析,此时取指部件是空闲的,于是就等来了第二个时钟周期;

第二个时钟周期,分析部件分析完成后就等待执行部件去执行,此时分析部件又是空闲的,而取指部件已经空闲了两个时钟周期了;然后就来到了第三个时钟周期;

第三个时钟周期,执行部件执行完后一条指令的过程才算走完。

以上这些步骤的串行执行,前面的部件空闲时间较长,这样部件资源利用率不高,从而导致整个过程效率不高。

应用流水线的技术就是:

三个部件并行执行,

取指部件取指完成后就接着取指下一个指令;

分析部件分析完后就接着分析下一条指令;第一个始终周期分析部件是空闲的,因为取指部件还正在取指令,执行部件亦然。这是流水线刚开始建立的一个过程。

此时,流水线建立完成后,三个部件就并行满负荷运转了。这样执行效率大大提升了。

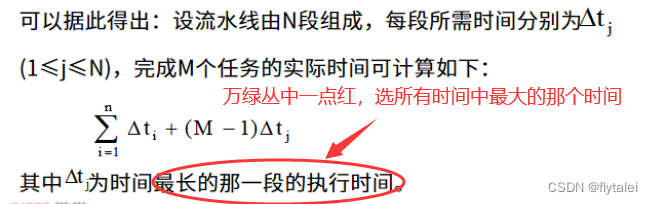

由流水线时空图可以看到,每经过一个T时间,就会有一条指令执行完毕, 因此执行N条指令的总时

间是3T+(n-1)XT,也就是第一条指令从开始执行到执行完毕的总时间是3T,以后每隔一一个T时间就

会多完成-条指令。因此只要再过(n-1)XT时间后,余下的n-1条指令都会执行完毕。从上面的分析还

可以看出,在线性流水线中,流水线各段执行时间最长的那段变成了整个流水线的瓶颈。一般地,将

其执行时间称为流水线的周期。所以执行的总时间主要取决于"流水操作步骤中最长时间的那个操作"。

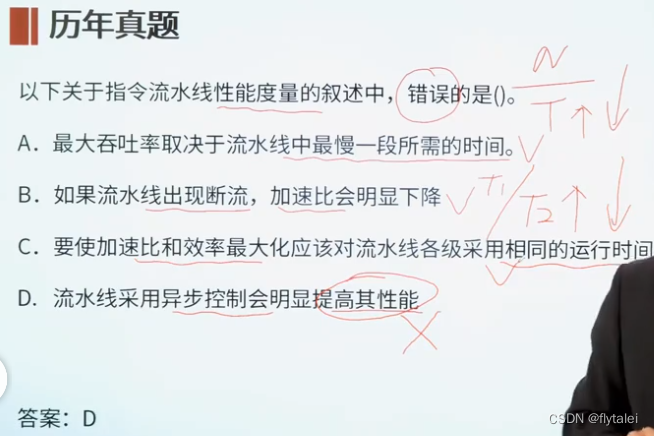

流水线的性能指标

一种流水线处理方式的性能高低主要有吞吐率、加速比和效率这三个参数来决定

(1)吞吐率。

吞吐率指的是计算机中的流水线在单位时间内可以处理的任务或执行指令的个数。

例题中,执行100条指令的吞吐率可以表示为TP=N/T=100/203*10^-9,

其中N表示指令的条数,T表示执行完N条指令的时间。

(2)加速比。

加速比是指某流水线采用串行模式的工作速度与采用流水线模式的工作速度的比值。

加速比数值越大,说明这条流水线的工作安排方式越好。

例题中,若串行执行100条指令的时间是T1=5 X 100= 500ns,

采用流水线工作方式的时间T2=203ns,

因此加速比R=T1/T2=500/203=2.463。

(3)效率。

效率是指流水线中各个部件的利用率。

由于流水线在开始工作时存在建立时间,在结束时存在排空时间,

各个部件不可能一直在工作,总有某个部件在某一个时间处于闲置状态。

用处于工作状态的部件和总部件的比值来说明这条流水线的工作效率。

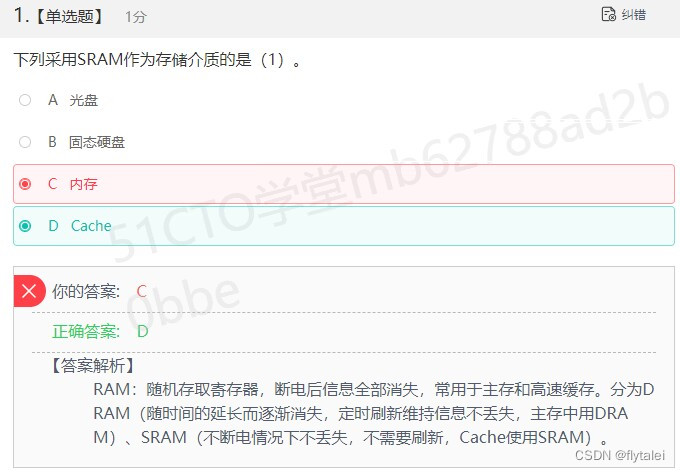

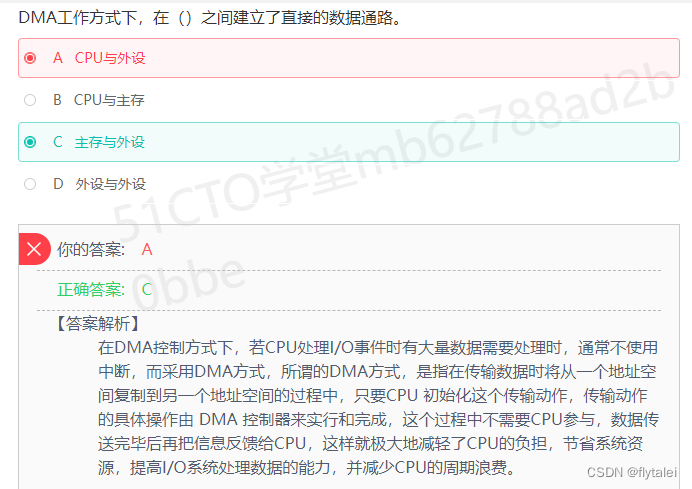

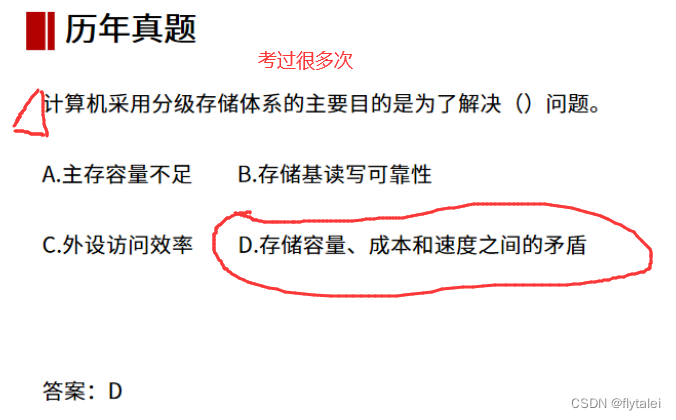

内存结构与内存储器类型

相关知识点:存储器类型、内存容量计算、命中率的计算等。

存储器按用途大致可分为两类:主存储器和辅助存储器。

主存储器也称为内存储器

辅助存储器也称为外存储器。

外存通常是磁性介质或光盘,能长期保存信息(如硬盘、磁带等),其速度相对内存而言要慢很多。

在计算机中,存储器按照数据的存取方式可以分为五类

(1)随机存取存储器(Random Access Mermory,RAM)。

RAM又分DRAM和SRAM

DRAM(动态随机存取存储器,Dynamic Random Access Memory):

随时间的延长而逐渐消失,定时刷新维持信息不丢失,主存中用DRAM)

SRAM(静态随机存取存储器,Static Random Access Memory):

所谓静态,就是不断电情况下存储的数据不丢失,不需要刷新,Cache使用SRAM)

(2)只读存储器(Read Only Memory,ROM)。

(3)顺序存取存储器(Sequential Access Memory,SAM)。磁带

(4)直接存取存储器(Direct Access Memory,DAM)。

(5)相联存储器(Content Addressble Memory,CAM)。

寻址方式

立即寻址:

指令的地址字段指出的不是操作数的地址,而是操作数本身,这种寻址方式称为立即寻址。

指令执行时间很短。

如:MOV AX,#1314H (MOV是把1314H这个数放到AX寄存器里面的一条指令,而1314不是一个地址,直接是一个数字)

注意:立即数只能作为源操作数。

直接寻址:

是一种基本的寻址方法,在指令格式的地址字段中直接指出操作数在内存中的地址。

由于操作数的地址直接给出而不需要经过某种变换,所以称这种寻址方式为直接寻址方式。

间接寻址:

指令地址字段中的形式地址不是操作数的真正地址,而是操作数地址的指示器,或者说此形式地址单元的内容才是操作数的有效地址。(中间有一个变换过程,把指示器中间的内容变换成真正的地址)

相对寻址方式

相对寻址是把程序计数器PC内容加上指令格式中的形式地址而形成操作数的有效地址。

基址寻址方式

在基址寻址方式中将CPU的基址寄存器的内容,加上变址寄存器的内容而形成操作数的有效地址。

基址寻址的优点是可以扩大寻址能力,从而可以在较大的存储空间中寻址。

8372

8372

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?