1、基本情况

HI3559AV100和690t之间使用pcie2.0 x2接口连接,3559作为RC端,690T作为EP端,驱动使用XDMA。系统主要功能是FPGA采集srio接口过来的图像数据,再通过pcie把数据传递给3559,3559再实现图像数据的存储、AI处理、编码输出等。

2、问题及过程

2.1、内核配置RC功能

参考海思手册即可,主要是在kernel的menuconfig中打开相应的功能即可。

2.2、LINKUP失败

系统启动后,通过lspci不能查看到ep设备,但是FPGA的PCIE状态显示linkup。

后偶然发现,对3559软复位后,lspci可以查看到ep了,显示如下:

由此判断,可能是RC启动快于EP,需要等待EP的启动。

修改代码如下:

修改后,多次测试rc可以直接检测到ep。

2.3、XDMA驱动加载失败

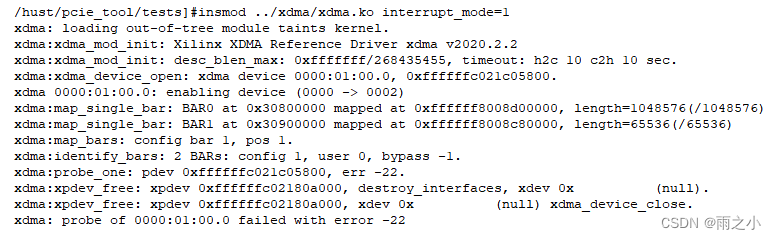

编译xdma驱动后,加载驱动失败,显示如下:

经过尝试发现驱动配置为poll模式可以正常,加载结果如下:

2.4、数据调试过程

数据的调试过程需要和FPGA精密配合,最后我这边形成的状态是访问对应的DMA通道设备即可完成和FPGA的PCIE接口数据交互。

2.4.1、RC数据接收测试

./dma_from_device -v 1 -d /dev/xdma0_c2h_0 -f output_datafile_4K.bin -s 0x5eec00 -c 10

结果显示如下:

由结果得知,实测的RC读速度为500MB/s,而理论的pcie2.0 X2速度为1000MB/s。

2.4.2、RC数据发送测试

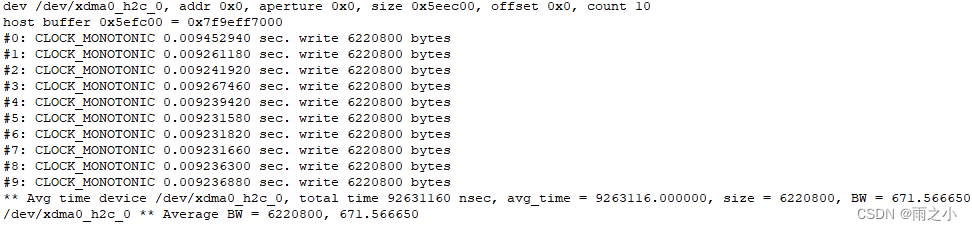

./dma_to_device -v 1 -d /dev/xdma0_h2c_0 -f data/datafile_32M.bin -s 0x5eec00 -c 10

结果显示如下:

由结果得知,实测的RC写速度为670MB/s,而理论的pcie2.0 X2速度为1000MB/s。

3、遗留问题

3.1、PCIE的中断模式使用失败

待查

3.2、PCIE的实际速度和理论速度有较大差异

待查

2777

2777

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?