上文![]() https://blog.csdn.net/fzktongyong/article/details/134963814?spm=1001.2014.3001.5501 上一篇文中PCIE实测速度和理论计算有较大偏差,经过尝试后有所提升。

https://blog.csdn.net/fzktongyong/article/details/134963814?spm=1001.2014.3001.5501 上一篇文中PCIE实测速度和理论计算有较大偏差,经过尝试后有所提升。

1、提升效果

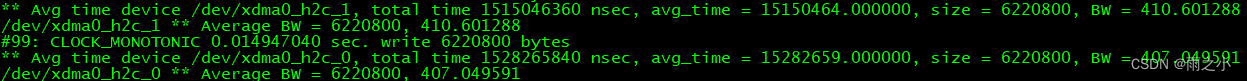

1)、RC写操作,实测速度817MB/s(410+407)

先前为670MB/s。

2)、RC读操作,实测速度710MB/s(357+353)

先前为500MB/s。

2、提升原理

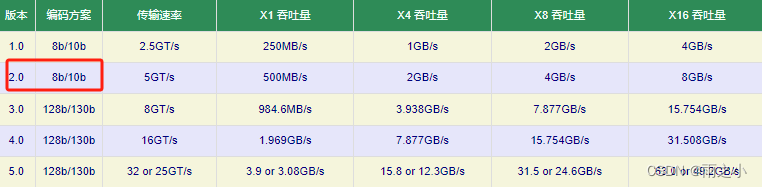

标准的PCIE接口速率如下:

因为FPGA的PCIE速度是可以接近于理论的,主要是CPU的控制管理速度跟不上,所以我尝试了XDMA的双通道接口,XDMA最多有4通道。多通道理论上是可以实现对FPGA的DMA并行控制,因此如果使用4通道的DMA可能会有更多的速度提升。

382

382

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?