假设我们想使用直流的芯片测量交流信号:由于交流信号的输出电压范围超过了芯片的量程,所以要按照比例缩小;由于交流信号有正有负,所以需要把交流信号电压抬升。

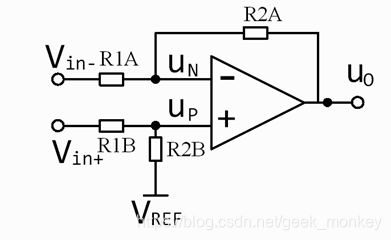

假设需要把电路抬高的幅度为V_REF。改进上一节学习过的带分压电路的同相比例运算电路,将同相输入端的参考电压由0V改为V_REF,得到交流信号运放电路

图 交流信号运放电路

同样,为了保证运放输入级差分电路的对称性,保证两个输入端的电流“看到”的阻抗是一样的,对应电阻的阻值要一致:R1A=R1B=R1,R2A=R2B=R2。

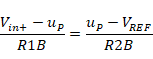

由于虚短:

由于虚断,分别分析P点与N点的电流关系:

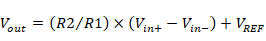

两式相加,得

如果无需抬高电压,即V_REF=0,交流信号通过同相输入端与反相输入端传入电路,这就是常见的交流信号运算放大电路。如果V_REF=0,V_(in-)=0,那么此公式与带分压电路的同相比例运算电路完全一样。

电子设计教程26:交流信号转为直流信号测量电路

最新推荐文章于 2025-04-28 19:43:19 发布

本文探讨了如何使用直流芯片有效测量交流信号,通过调整电路设计实现信号的缩小与抬升,确保信号适应芯片量程,并保持电路对称性。

本文探讨了如何使用直流芯片有效测量交流信号,通过调整电路设计实现信号的缩小与抬升,确保信号适应芯片量程,并保持电路对称性。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?