1、实验目的

掌握变量译码器的的逻辑构成和逻辑功能

用变量译码器实现组合函数

采用原理图设计电路模块

进一步熟悉 ISE 平台及下载实验平台物理验证

2、实验内容

任务 1:原理图设计实现 74LS138 译码器模块

任务 2:用 74LS138 译码器实现楼道灯控制器

3、实验过程

任务 1:原理图设计实现 74LS138 译码器模块

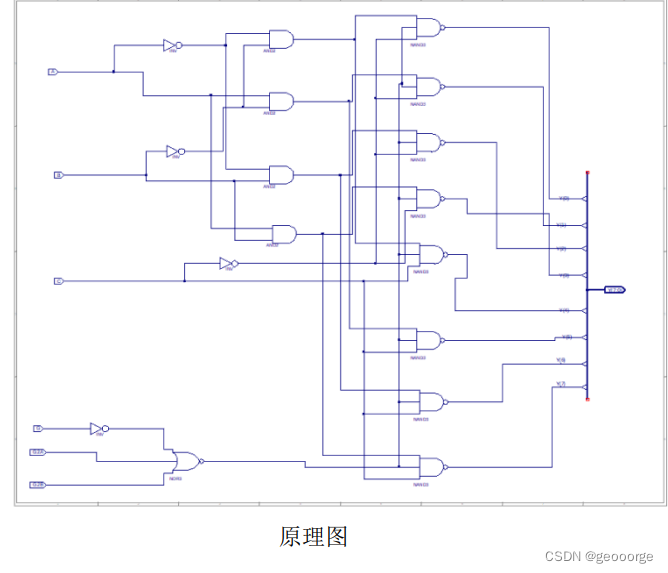

1.创建工程并绘制原理图

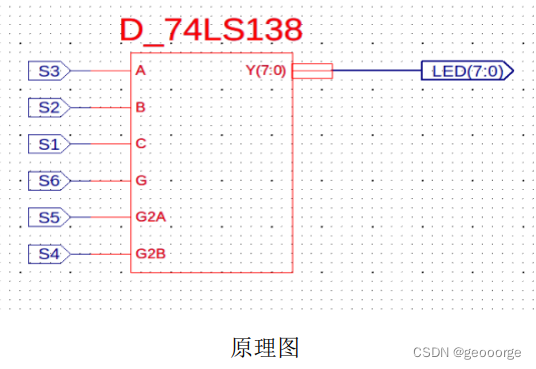

建立工程 D_74LS138_SCH,创建原理图文件 D_74LS138,按原理图设计

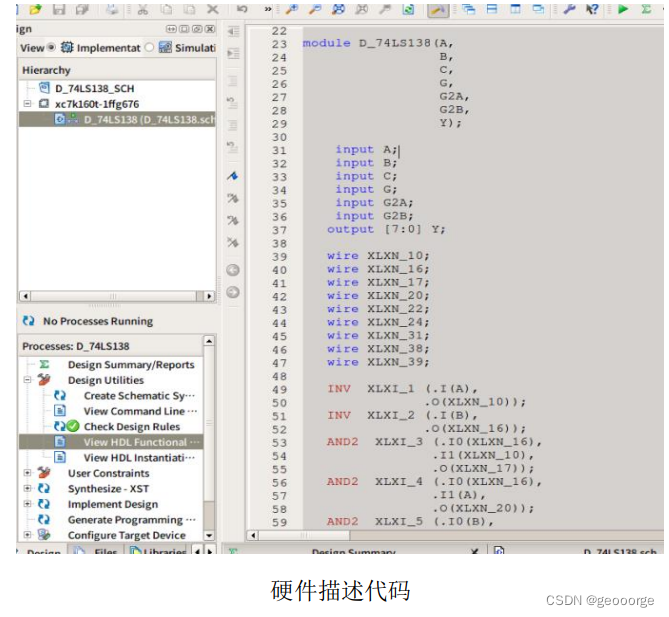

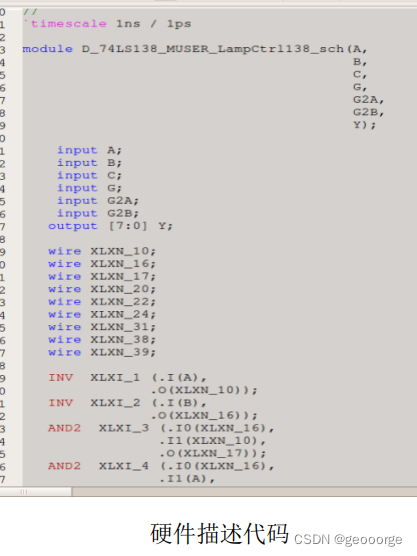

Check Design Rules 后,查看输入电路的硬件描述代码

2.原理图仿真

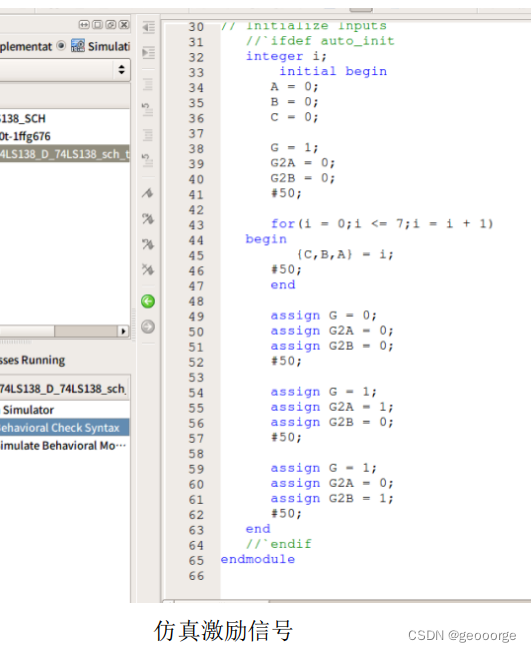

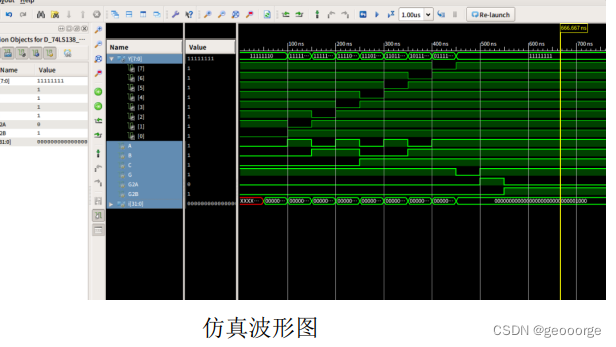

建立基准测试波形文件 D_74LS138_sim,输入仿真激励信号,在 Process 窗口中选择 Simulate Behavioral Model,可以得到模拟出 的波形图:

3.生成逻辑符号图

在 Design Ubilities 中打开 Create Schematic Symbol,自动生 成模块的逻辑符号图文件,符号图是.sym 类型,位于工程根目录, 可以用 Tools 菜单的 Symbol Wizard 修改,新工程使用时只需要把文 件复制到新工程的目录即可。

4. 新建测试工程并复制部分文件

新 建 工 程 D_74LS138_Test , 新 建 Schematic 类 型 的 文 件 D_74LS138_Test。复制过来.sym 和.sch 文件,按照下面的原理图设 计测试文件。

5.验证 D_74LS138 的功能

可以在模块右键菜单中的 Symbol 中选择 Push into Symbol 查看 模块的原理图,之后可以在右键菜单中点击 Pop to calling Schematic 回到上层模块。

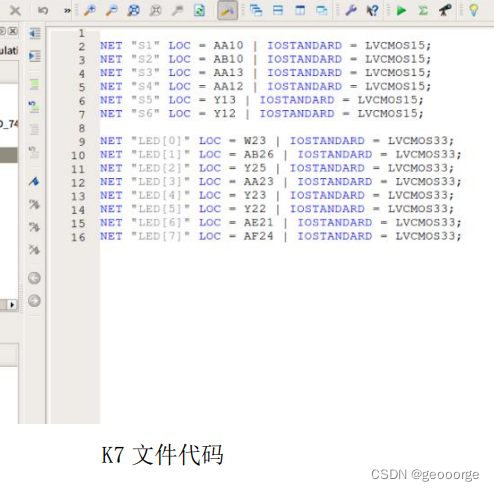

建立 K7.ucf 文件分配引脚,并查看引脚分配结果

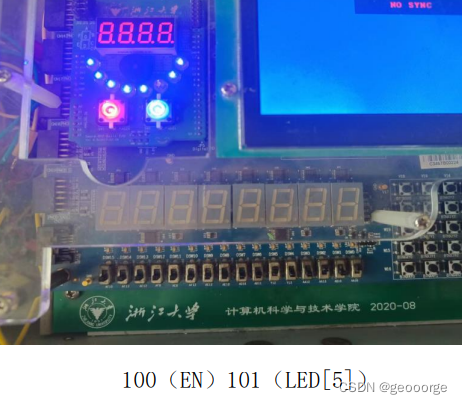

之后按照真值表验证功能即可。当 G 连接的 S6 开关处于高电平, 并且 G2A 连接的 S5、G2B 连接的 S4 都处于低电平时,整个电路处于 Enable 状态,此时 S1、S2、S3 的每一种组合都对应了灯泡的一种状 态。

而当 S4、S5、S6 并非是这种组合时,电路处于 unable 状态,无 论 S1、S2、S3 处于什么状态,电路输出都不会改变,灯泡始终都是; 亮的。

图中从左向右的末六位开关依次对应的是 S6(G),S5(G2A), S4(G2B),S3(A),S2(B),S1(C),以下图片名称对应状态均 为从左到右

随便来两张图

任务 2:用 74LS138 译码器实现楼道灯控制器

1.创建工程并绘制原理图

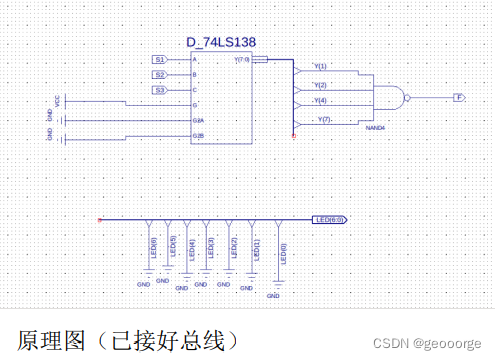

建 立 工 程 LampCtrl138 , 复 制 过 来 D_74LS138.sym 和 D_74LS138.sch 文件,创建原理图文件 LampCtrl138,按原理图设计, 不过这里 G 直接在内部用 VCC(1)连接,G2A 和 G2B 用 GND(0)连 接,是其处于使能状态。

参 考 实 验 4 的 真值表 可 以 知 道 应 该 接 的 线 是 Y(1),Y(2),Y(4),Y(7)

Check Design Rules 后,查看输入电路的硬件描述代码

2.原理图仿真

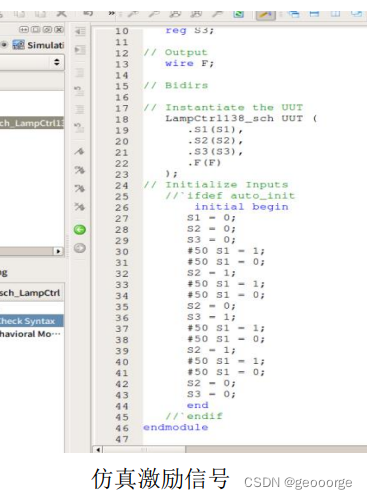

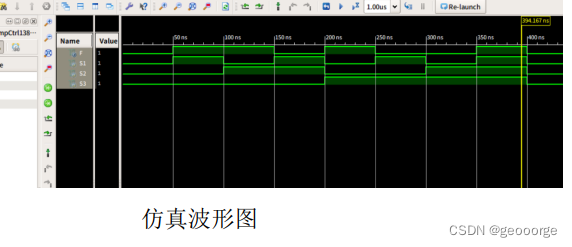

建立基准测试波形文件 LampCtrl_sim,输入仿真激励信号,在 Process 窗口中选择 Simulate Behavioral Model,可以得到模拟出 的波形图

:

:

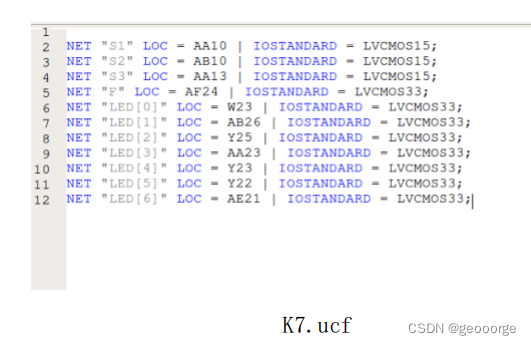

3.分配引脚

建立引脚约束文件 K7.ucf,输入代码,为原理图的每个输入输出 端口分配引脚。

4. 下载验证

具体的功能应该和实验 4 的第一个任务一样,有偶数个开关打开 时灯泡熄灭,奇数个灯泡打开时灯泡亮起(可从真值表中得到),从 左向右为 S3、S2、S1,图片名称依然表示从左到右的开关状态

4、实验结果

没什么新东西,过了

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?