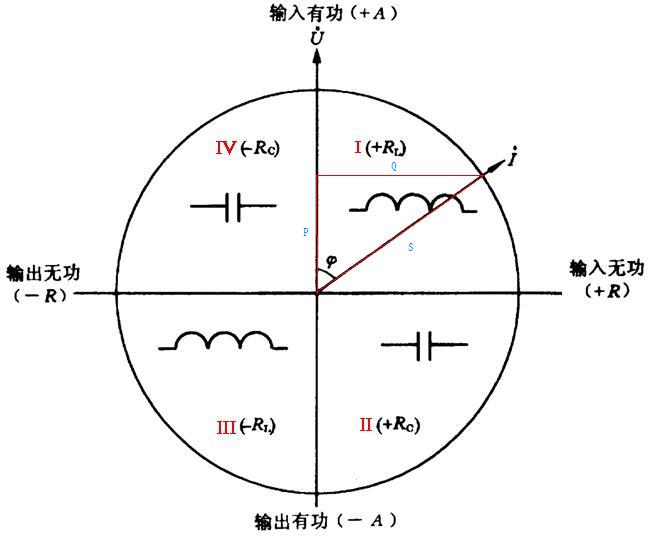

根据《多功能电能表通信协议》DL/T645-2007的规定,我们将一个平面坐标系的横轴定义为无功功率,纵轴定义为有功功率,二个轴将一个平面划分为四个区域,右上角的为「Ⅰ象限」,顺时针依次为「Ⅱ象限」、「Ⅲ象限」和「Ⅳ象限」;「Ⅰ象限」和「Ⅱ象限」无功定义为正向无功,「Ⅲ象限」和「Ⅳ象限」无功定义为反向无功;

注意:规定顺时针方向相角为正。与数学上的象限相反。

按下面的要求定义实际功率的方向:

正向有功功率:即输入有功功率,是电网向用户送电,是用户用电功率;

反向有功功率:即输出有功功率,是用户向电网送电,是用户发电功率;

正向无功功率:即输入无功功率,是电网向用户送无功,是用户用无功功率;

反向无功功率:即输出无功功率,是用户向电网送无功,是用户发无功功率;

Ⅰ象限无功:输入有功功率,输入无功功率,用户为感性(电流滞后电压)负载;

Ⅱ象限无功:输出有功功率,输入无功功率,用户负荷相当于一台欠励磁发电机;

Ⅲ象限无功:输出有功功率,输出无功功率,用户负荷相当于一台过励磁发电机;

Ⅳ象限无功:输入有功功率,输出无功功率,用户为容性(电流超前电压)负载;

Ⅰ象限:消耗有功功率,消耗感性无功功率。

Ⅱ象限:输出有功功率,输出容性无功功率。

Ⅲ象限:输出有功功率,输出感性无功功率。

Ⅳ象限:消耗有功功率,消耗容性无功功率。

9842

9842

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?