目录

1. 时钟

STM32的时钟就是周期性的脉冲,50%占空比的方波、正弦波或三角波都可作为STM32的时钟信号。

2. STM3时钟源(哪些可以作为时钟信号)

| 时钟源 | 时钟范围 | 主要用途 | |

| HSE | 高速外部时钟 |

4~16MMHz

| 1. 系统时钟 2. 128分频后输入RTC时钟 |

| HSI | 高速内部时钟 | 8MHz | 1. 备用时钟源 2. 2分频后作为PLL输入 |

| LSE | 低速外部时钟 | 32.768kHz | RTC实时时钟 |

| LSI | 低速内部时钟 | 40kHz | 1. 待机/停机模式下时钟 2.RTC、IDWG、AWU时钟 |

2.1 HSE时钟

2.1.1 高速外部时钟信号(HSE)来源

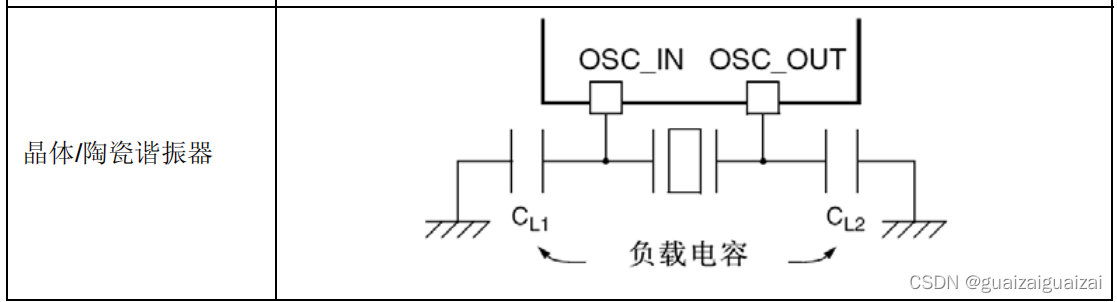

- HSE外部晶体/陶瓷谐振器(通常使用这种)

- HSE用户外部时钟

2.1.2 HSE外部晶体电路配置

注:1.时钟控制寄存器(RCC_CR)中HSERDY位被置位,表示高速外部振荡器稳定2.时钟控制寄存器(RCC_CR)中HSEON位表示开启或关闭HSE高速外部时钟

2.2 HSI时钟

| 来源 | 内部8MHz |

| 振荡器 | RC振荡器 |

| 作用 | 1. 直接作为系统时钟 2.2分频后作为PLL输入 3.如果HSE失效,HSI时钟会被作为备用时钟源 |

| 优点 | 1. 不需要额外的外部器件,成本较低 2.启动时间比HSE短 |

| 缺点 | 1.校准后时钟频率精度仍然较差 2.RC振荡器精度受电压和环境影响 |

| 时钟控制寄存器RCC_CR | 1. HSIRDY位置位,表示HSI时钟稳定 2.HSION位开启或者关闭HSI时钟 |

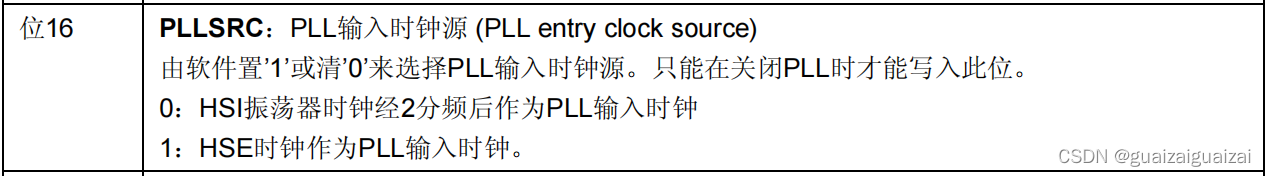

2.3 PLL时钟

PLL锁相环是一种控制系统,之所以叫PLL时钟,是因为,PLL通过调整输入信号(HSE、HSI)的频率和相位,以满足系统对不同频率的要求。

| 输入 | 1. HSI 2分频后输入 2.HSE |

| 使用 | 1. 输入时钟源稳定后才能使能PLL(RCC_CR的HSIRDY或者HSERDY置位) 2.使能PLL前需要完成PLL配置(选择时钟源、预分频系数、倍频系数) |

时钟配置寄存器(RCC_CFGR):

为何要用倍频器,而不是选择一个高频率的晶振?

对于稳定运行的电路来说,时钟频率越高,指令执行越快,单位时间内处理的功能也就越多。但是时钟源的时钟频率最高也就16MHz,达不到STM32系统时钟72MHz的要求,因此需要倍频器将外部时钟频率进行倍频,在输入给系统时钟。

倍频涉及到时钟配置寄存器(RCC_CFGR):

2.4 LSE时钟

| 来源(输入) | 外部32.768KHz |

| 振荡器 | 外部晶体 |

| 作用 | 1. 驱动RTC实时时钟 2. 备份域控制寄存器(RCC_BDCR)LSERDY置位表示晶体振荡器稳定,LSEON表示开启或关闭该时钟 |

| 优点 | 1. 低功耗 2. 精确 |

2.5 LSI时钟

| 来源 | 内部40kHzRC震荡时钟 |

| 作用 | 1. 在停机模式/待机模式下保持运行 2. 独立看门狗(IDWG)时钟、自动唤醒单元(AWU)时钟 3.控制 /状态寄存器(RCC_CSR)里的LSIRDY置位表示震荡稳定,LSION位控制开启或关闭该时钟 |

3. STM32时钟(哪些系统使用时钟)

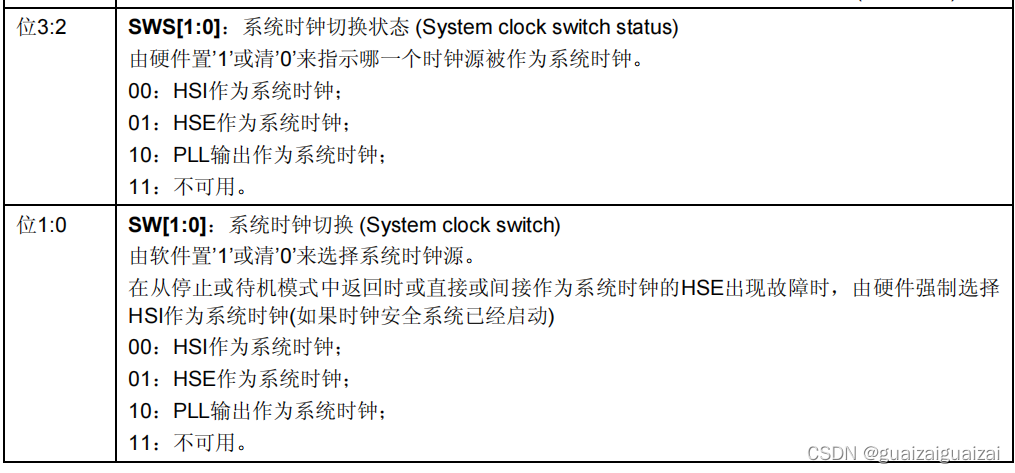

3.1 系统(SYSCLK)时钟

SYSCLK为整个芯片提供时钟信号,其来源主要有3种:

1. HSE作为系统时钟

2. HSI作为系统时钟

3.PLL作为系统时钟(又叫做HSE间接作为系统时钟)

可在时钟控制寄存器(RCC_CR)中状态指示位查看当前系统时钟的时钟来源。

另外,当系统时钟的时钟源要进行切换时,只有目标时钟源准备就绪后,时钟源的切换才会发生,涉及时钟配置寄存器RCC_CFGR:

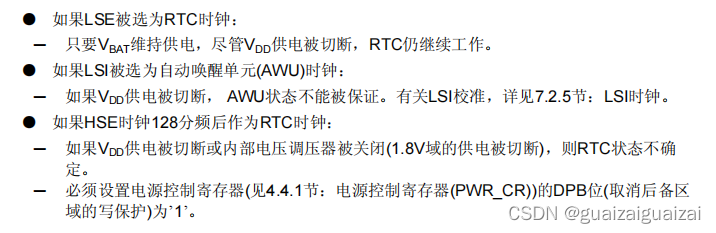

3.2 RTC时钟

三个输入:LSE、LSI、HSE128分频

3.3 看门狗时钟

LSI提供40kHz时钟。如果看门狗被启动,则LSI会被强制启动,待振荡器稳定后,输入给看门狗。

3.4 时钟输出MOC

4. STM32时钟树

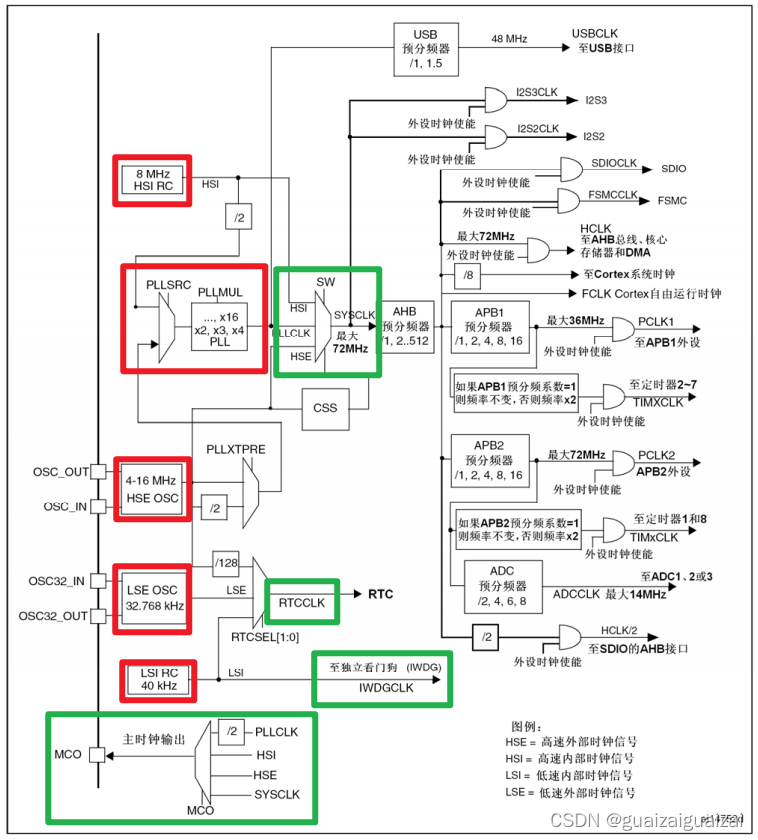

图中标红色方框的为时钟源,可以看到包括之前介绍的HSE、LSE、PLL、HSI、LSI。

图中标绿色方框的为使用时钟(MCO为输出时钟),包括SYSCLK、RTC、IWDG、MOC。

除此之外,时钟树右侧部分,即SYSCLK输出,主要包括外设和和AHB。

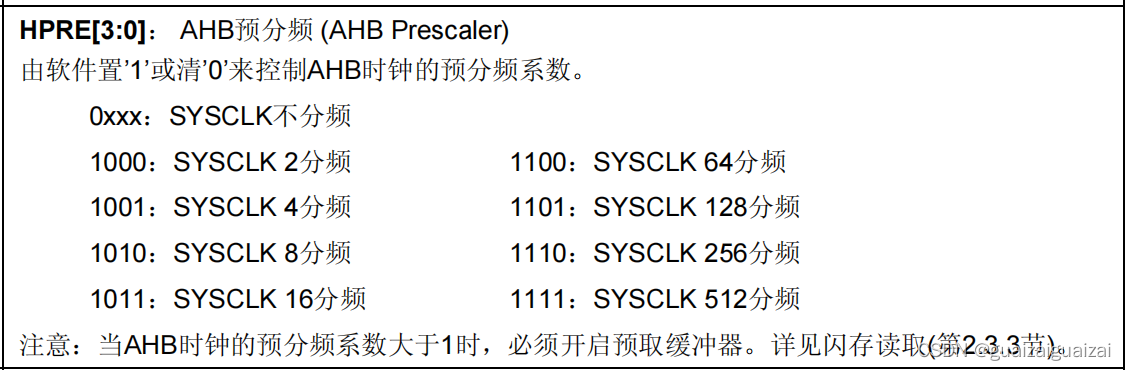

4.1 AHB预分频器

预分频器,可通过配置分频系数,调整输出时钟的频率。分频允许系统中不同部分以不同的频率运行,以满足不同模块的工作需求。【主时钟(SYSCLK)、APB1时钟、APB2时钟】

AHB预分频器的分频系数可以选择为1(不分频)、2、4、6、8、16、64、128、256、512。

涉及寄存器为时钟配置寄存器RCC_CFGR:

AHB输出到APB1总线和APB2总线,其中APB1总线最大时钟频率为36MHz,为低速时钟,片上挂载低速外设,例如看门狗定时器,USART2\3\4\5,SPI2\3等。APB2总线最大时钟频率为72MHz,其上通常为各种外设的1号选手,例如USART1、ADC1、SPI1等。

5. STM32时钟配置

看一下STM32是怎么配置系统时钟的。

此处以STM32F10xx系列为例,下载STM32固件库后,找到system_stm32f10x.c和system_stm32f10x.h两个文件,这两个文件是STM32用来配置系统时钟的。它提供了两个函数、一个变量和一些宏定义来进行时钟配置。

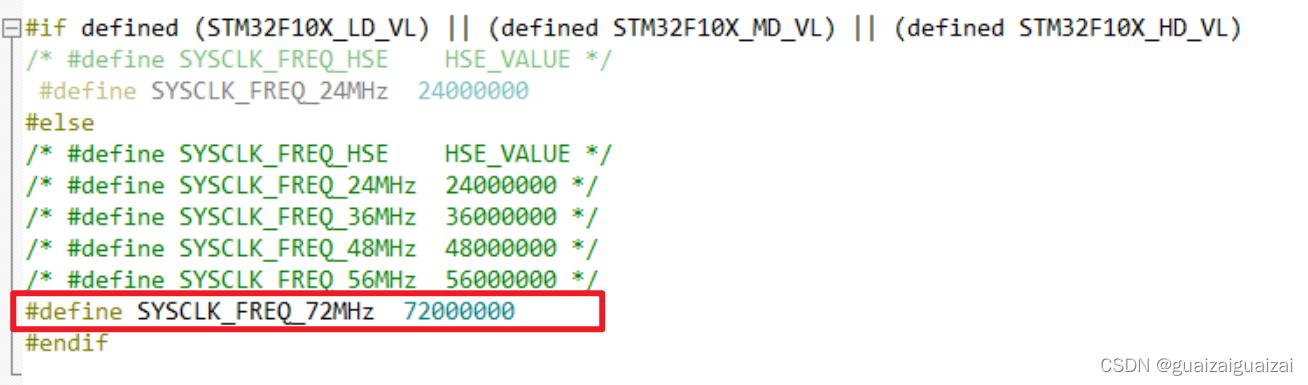

可以看到,通过SystemInit()函数,最终调用SetSSysclockTo72(),使用高速外部时钟源,最终在PLL锁相环9倍频,赋值给系统时钟。AHB、APB1、APB2经过分频系数分频,分别得到72MHz、36MHz、72MHz时钟频率。

观察SetSysClock(),通过宏定义最终调用所选择的主频率,如果为了降低功耗,或者需要修改STM的主频,可直接修改SYSCLK_FREQ_xxMHz宏定义来修改系统的主频,同样可以在system_stm32f10x.c文件中修改。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?