体系结构

- IA

Intel Architecture,intel对自己CPU架构的简称,属复杂指令集(CISC-Complex Instruction Set Computer),区别ARM的精简指令集(RISC-Reduced Instruction Set Computer),或者其它。 - IA-32

Intel Architecture 32 bit,Intel的32 bit CPU架构。 - Intel 64

Intel的64 bit CPU架构。 - X86-64

Intel的64 bit CPU架构,同上,因为祖宗都是8086架构,所以加一个X86在前面。 - AMD64

Intel的64 bit CPU架构,同上,现代的64 bit CPU并非纯粹的64 bit,它是IA-32基础上的新增64 bit寄存器及其它以兼容32 bit CPU架构和更早的16 bit架构,实现此架构最早的是AMD公司,因此命名AMD64。 - IA-32e mode

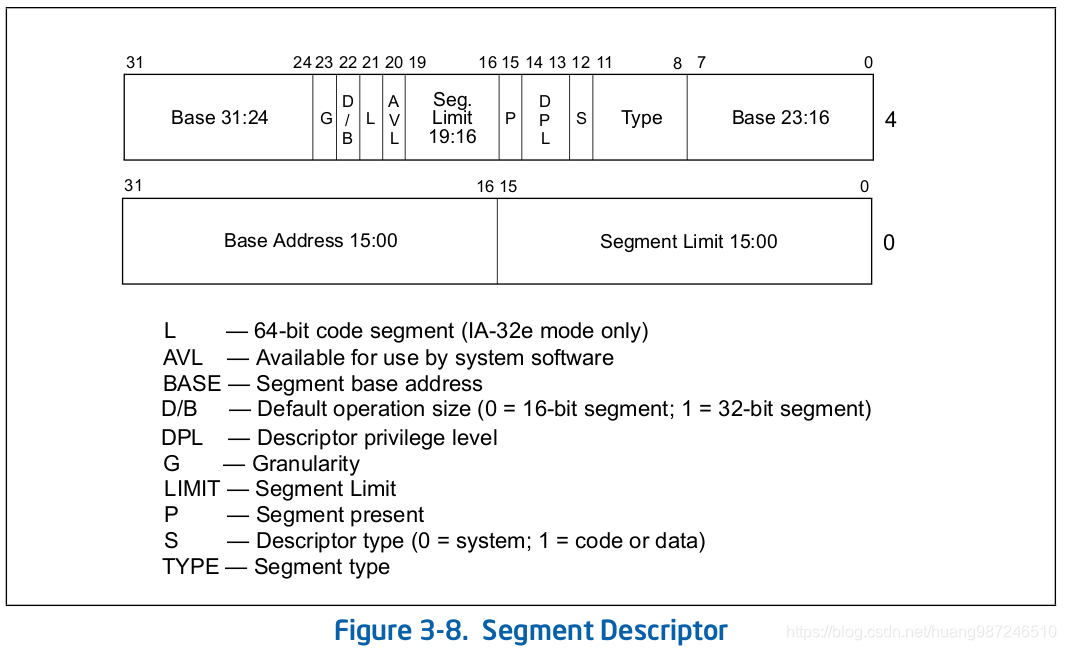

Intel 64架构新增操作模式,操作模式决定CPU的哪些指令和特性可用。比如段描述符(Segment Sescriptor)属性中的L位。在IA-32e mode模式下定义才生效,在非IA-32e mode下留做保留位,必须是0(bit 21 is reserved and should always be set to 0)。

IA-32e mode包括两个子模式(64-bit mode,compatibility mode),由上面说的L位决定。

L=1:64-bit mode

L=0:compatibility mode

- UP(Uni-Processor),单核CPU系统

- SMP(Symmetric Multi-Processors),多核CPU系统

中断

- posted-interrupt notication vector

posted-interrupt通知中断向量,当KVM要注入一个PI中断时,首先填写在posted-interrupt descriptor写入要注册的中断,然后发送核间中断到目标CPU,核间中断的向量就是posted-interrupt notication vector。posted-interrupt notication vector记录在VMCS中 - posted-interrupt descriptor

posted-interrupt描述符,该描述符中包含PIR和通知标志位。posted-interrupt descriptor也记录在VMCS中 - PIR(posted-interrupt requests)

有256bit,每个bit对应一个中断向量,位于posted-interrupt descripto中。KVM将要注入的中断在描述符对应位置1,逻辑处理器在响应该中断时将其同步到vIRR,实现PI中断的投递。 - PIT(Programmable Interval Timer)

一个产生定时中断的可编程芯片,通常用来做硬件上的系统时钟,也称为System Clock

PCI

- RC(Root-Complex)

图像

- DRM(Direct Rendering Manager)

内核的一种设备驱动框架,GPU的驱动常常使用DRM驱动框架 - GEM(Graphics Execution Manager)

DRM中管理内存的模块 - GFX(short for ‘graphics’)

一种用户描述3D动画模式的文件格式

本文介绍了Intel Architecture (IA) 的发展历程,从IA-32 到 Intel64 和 X86-64,并讨论了AMD64架构的重要性。此外,还深入探讨了IA-32emode的操作模式以及中断机制,包括posted-interrupts的工作原理。

本文介绍了Intel Architecture (IA) 的发展历程,从IA-32 到 Intel64 和 X86-64,并讨论了AMD64架构的重要性。此外,还深入探讨了IA-32emode的操作模式以及中断机制,包括posted-interrupts的工作原理。

9353

9353

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?