芯片架构和功耗

芯片设计除了要满足功能和规格需求外,功耗也是必不可少的一项重要指标。芯片架构设计由一系列设计决策构成,包括软硬件划分,IP选型,核型配置,核数确定,时钟频率确定,内存规划等,每一项设计决策都会对功耗产生影响,本篇主要分析上述几个对功耗影响较大的决策项,并由此得出相应的降低功耗的方法。

1 时钟频率

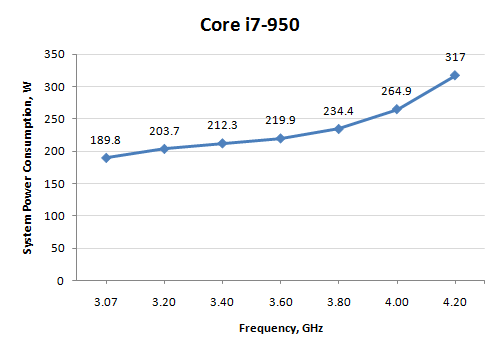

图1 显示了在intel的一款CPU(Core i7-950)上所作的功耗测试结果[1]。从图中可以看出,功耗和时钟频率的变化并不是线性关系,随着时钟频率的上升,功耗的增加速度越来越快。以3.2GHZ 和 4.2GHZ 两个频率点为例,频率增加了31%,而功耗则上升了56%,也就是说多出来的功耗并未对处理能力有所贡献;如果保持频率不变而只增加核数,那么处理能力和功耗的上升速率是基本匹配的。换言之,在其他参数不变的情况下,多个低频核的功耗少于单个高频核,这也是越来越多的芯片采用多核架构的原因之一。需要注意的是,图1中的曲线只在一定频率范围内成立,在芯片设计阶段能够模拟出该曲线(或者根据经验数据估计)并找到最合适的频点,对于功耗和规格优化都具有重要意义。

图1

2 同构核与异构核

各核按功能划分可以分为同构核和异构核。对于异构核,不同的核负责业务的不同部分,需要多核同时运行才能实现完成的业务处理流程;而同构核则是单个核完成所有业务功能&#

本文探讨了嵌入式系统中降低功耗的有效方法,包括调整时钟频率以减少无效功耗,利用同构核与异构核的特性,优化软硬件交互机制,设计低功耗内存方案以及资源虚拟化以提高多核利用率。通过对时钟门控、功能迁移、基础HAC单元配置及内存结构规划,实现了功耗与性能的平衡。

本文探讨了嵌入式系统中降低功耗的有效方法,包括调整时钟频率以减少无效功耗,利用同构核与异构核的特性,优化软硬件交互机制,设计低功耗内存方案以及资源虚拟化以提高多核利用率。通过对时钟门控、功能迁移、基础HAC单元配置及内存结构规划,实现了功耗与性能的平衡。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

437

437

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?