实验要求

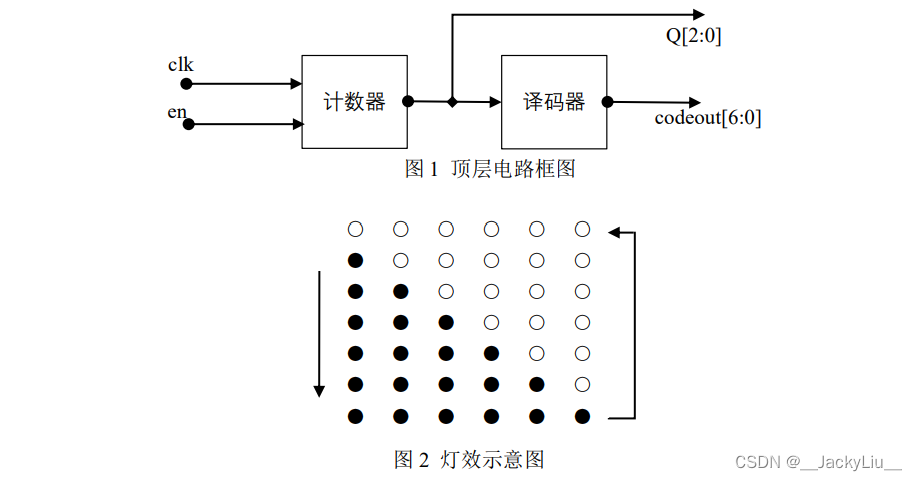

一、 实验目的 1、巩固组合逻辑电路设计、仿真方法。 2、学习 Verilog HDL 层次化文件设计。 二、 实验内容 1. 用 Verilog HDL 以层次化的设计方法,结合实验1(需修改部分代码),使用下文计数器模块代码“Code-1 7 进制计数器”,将计数器输出Q与译码器输入 x 相连,译码器输出 codeout 锁定到实验箱的 LED 上,设计一个彩灯控制器。LED 在控制电路的驱动下,按图 2 所示规律点亮/熄灭(●表示亮灯,○表示灭灯)。对整体电路进行仿真,应当能够看到 en 为高电平时计数器的输出值自动增加,相应地译码器的输出依次变化,并循环。

模块代码

module ljq_2344_3_1 (

clk,en,Q,codeout,segout,SEG

);

input clk, en; // 定义输入变量

output [2:0] Q;

output [5:0] codeout; // 定义输出变量

output [6:0] segout; // 定义输出变量

output reg [7:0] SEG; // 定义输出变量

always @(*) begin

SEG = 8'b0000_0001;

end

ljq_2344_3_1_a counter(clk, en, Q); // 定义子模块

ljq_2344_3_1_b decoder(Q, codeout); // 定义子模块

ljq_2344_3_1_c code(Q, segout);

endmodulemodule ljq_2344_3_1_a(clk,en,Q);//计数器

input clk,en; //输入时钟和使能

output reg[2:0] Q; //计数器输出

always@(posedge clk) //时钟上升沿执行

begin

if(en == 1'b1) //使能端处于高电平自加

begin

if(Q < 3'd6) // Q = 0, 1, 2 ,3, 4, 5,6控制点亮灯数

Q = Q + 1'b1;

else

Q = 3'b000; // Q退回0

end

else

;

end

endmodulemodule ljq_2344_3_1_b(Q,codeout); //译码器

input [2:0]Q; //译码器输入接收计数器输出

output reg[5:0]codeout; //译码器输出

always@(Q)

begin

case(Q)

3'd1:codeout = 6'b00_0001; //Q为1 点亮1个灯

3'd2:codeout = 6'b00_0011; //Q为2 点亮2个灯

3'd3:codeout = 6'b00_0111; //Q为3 点亮3个灯

3'd4:codeout = 6'b00_1111; //Q为4 点亮4个灯

3'd5:codeout = 6'b01_1111; //Q为5 点亮5个灯

3'd6:codeout = 6'b11_1111; //Q为6 点亮6个灯

default:codeout =6'b00_0000; // Q为0(默认) 不点亮

endcase

end

endmodulemodule ljq_2344_3_1_c (

Q, segout

);

input [2:0] Q;

output [6:0] segout;

reg[6:0] segout;

reg [7:0] SEG = 8'b0000_0001;

always @(Q) begin

case (Q)

4'd0: segout=7'b111_1110;

4'd1: segout=7'b011_0000;

4'd2: segout=7'b110_1101;

4'd3: segout=7'b111_1001;

4'd4: segout=7'b011_0011;

4'd5: segout=7'b101_1011;

4'd6: segout=7'b101_1111;

4'd7: segout=7'b111_0000;

4'd8: segout=7'b111_1111;

4'd9: segout=7'b111_1011;

default

: segout=7'bx;

endcase

end

endmodule //lig_2344_3_1_c

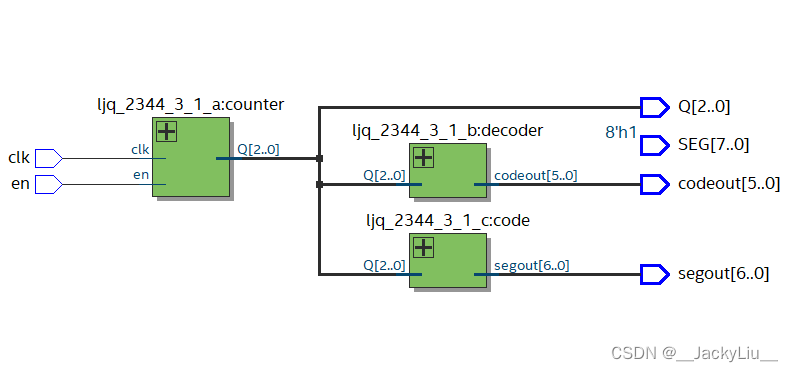

RTL电路图

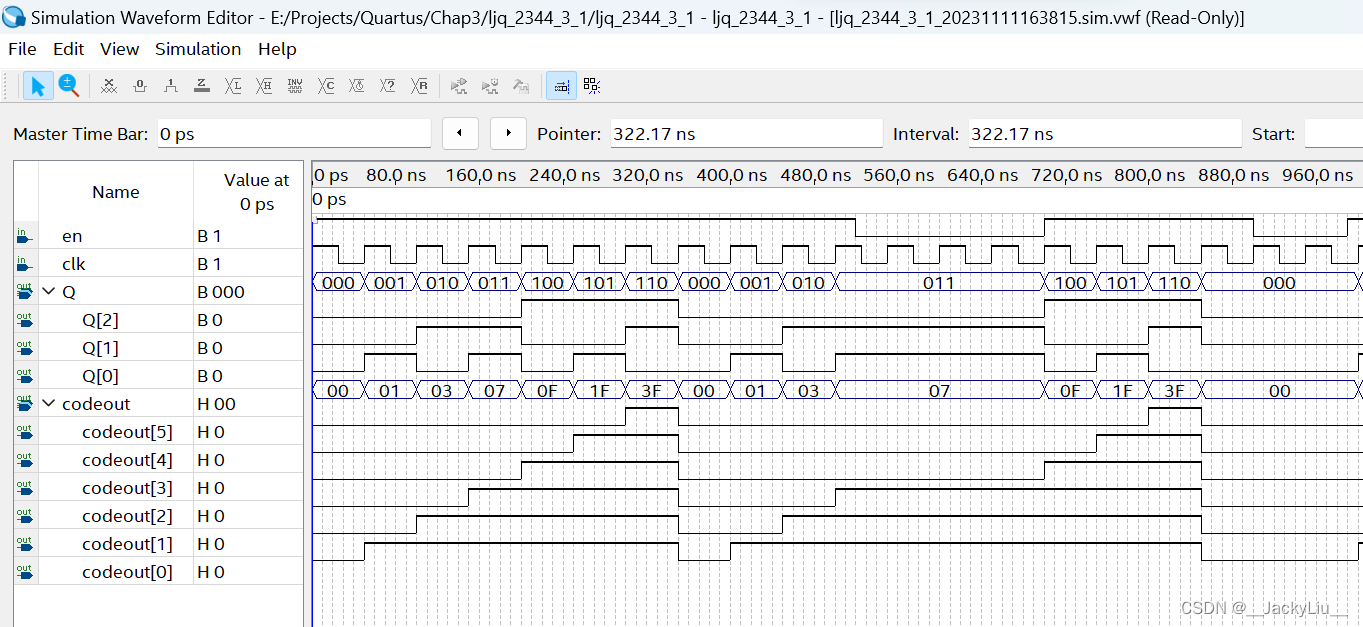

验收波形图

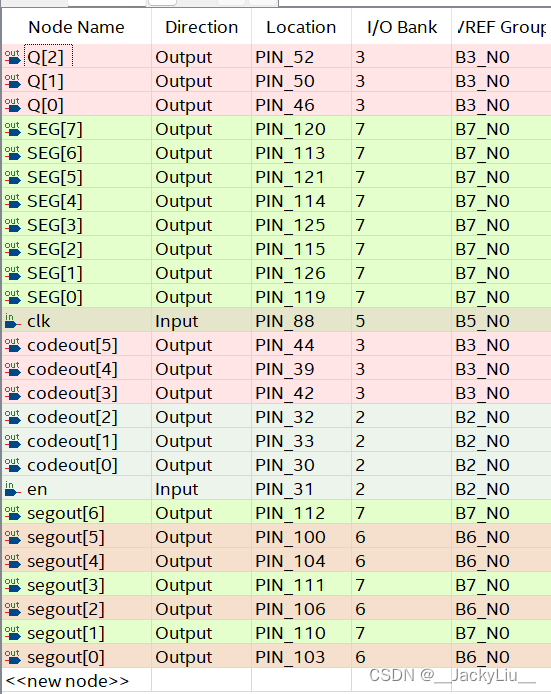

引脚分配表(EP4CE6E22C8)

标准参考:

本文介绍了使用VerilogHDL进行层次化设计,通过计数器和译码器实现一个彩灯控制器,LED按照特定规律亮灭。实验要求学生修改代码并观察电路仿真,验证电路功能。

本文介绍了使用VerilogHDL进行层次化设计,通过计数器和译码器实现一个彩灯控制器,LED按照特定规律亮灭。实验要求学生修改代码并观察电路仿真,验证电路功能。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?