题目 基本指令系统的设计与实现

主要内容、基本要求、主要参考资料等:

主要内容:

独立设计一套包含输入输出类、数据传递类、算数运算类、控制转移类的简单指令系统,设计相应的微指令系统对指令系统中的指令进行解析,用指令编写一个有一定实际意义的程序,并在组成原理实验箱上验证设计内容。

基本要求:

1.完成设计方案,充分论证设计方案的可行性,设计方案应该包括指令格式说明、微指令流程图、微指令编码表、程序清单。

2. 有详细的实验步骤和具体的接线图。

3. 认真进行实验,验证设计方案的正确性。

4. 对实验过程和结果进行认真分析总结,写出课程设计报告。

1、基本模型机

1.1 模型机的结构

1.2 模型机的寻址方式

立即数寻址:参与运算的数据为指令的操作数。例如“SUB A,#10H”是从累加器A中减去立即数10H,结果存入累加器A。

寄存器寻址:参与运算的数据在R0-R3的寄存器中,例如“ADDA,R0”指令是将寄存器RO的值加上累加器A的值,再存入累加器A中。

寄存器间接寻址:参与运算的数据在存储器EM中,数据的地址在寄存器R0-R3中,如“MOV A,@R1"指令是将寄存器R1的值做为地址,把存储器EM中该地址的内容送入累加器A中。

存储器直接寻址:参与运算的数据在存储器EM中,数据的地址为指令的操作数。例

如“AND A, 40H”指令是将存储器EM中40H单元的数据与累加器A的值做逻辑与运算,结果存入累加器A。

1.3模型机指令集

汇编指令 | 机器码1 | 机器码2 | 注释 |

IN Ri A,N | 04H |

| 从IN 读入N存入Ri和A |

MOV Ri W, #N | 09H | N | 将直接数N存入Ri和A |

MOV Ri ST, #N | 0FH | N | 将直接数N存入Ri和ST |

JC A W,#N | 80H | N | A<W 则跳转到N地址 |

JZ A W,#N | A4H | N | A=W 则跳转到N地址 |

ZERO Ri | 12H |

| 将Ri置零 |

MOV A ,Ri | 15H |

| 将Ri中数送至A |

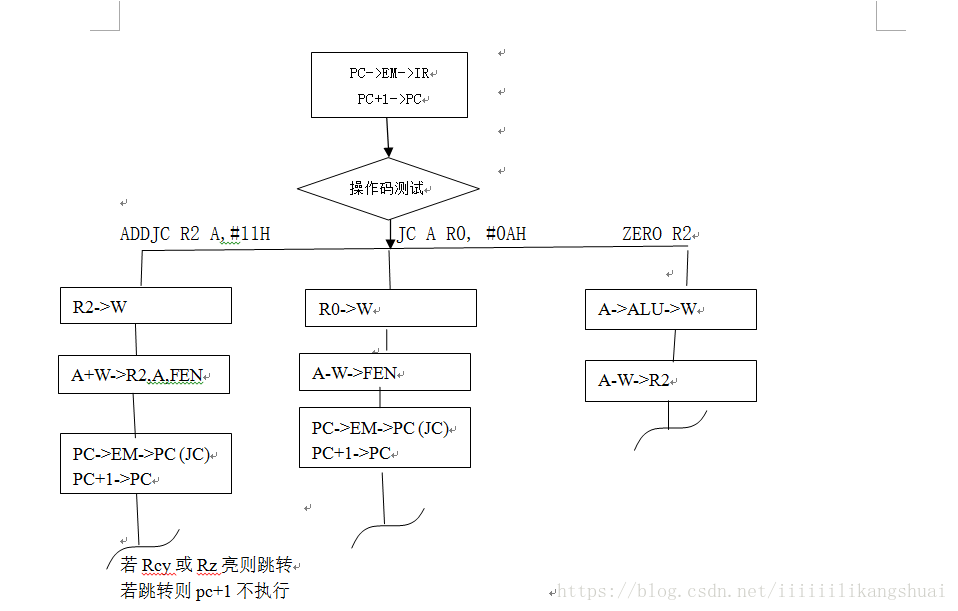

ADDJC Ri A,#N | C2H | N | 将Ri加上A再送回Ri和A, 溢出则跳转至N |

JC A Ri, #N | 90H | N | A<Ri ,则跳转至N地址 |

ADD Ri , ST | 1DH |

| Ri自增 ST ,并存入Ri和A |

OUT #N | 20H | N | 从OUT输出 N |

JMP #N | B8H | N | 无条件跳转到N地址 |

|

|

|

|

2、设计内容

2.1 源程序

程序功能描述: 从IN输入一个数(小于等于255),判断其是否是素数。

指令: (一下指令顺序执行)

汇编指令 | 机器码1 | 机器码2 | 指令说明 |

IN R0 A,N | 04H |

| 从IN 读入N存入R0和A |

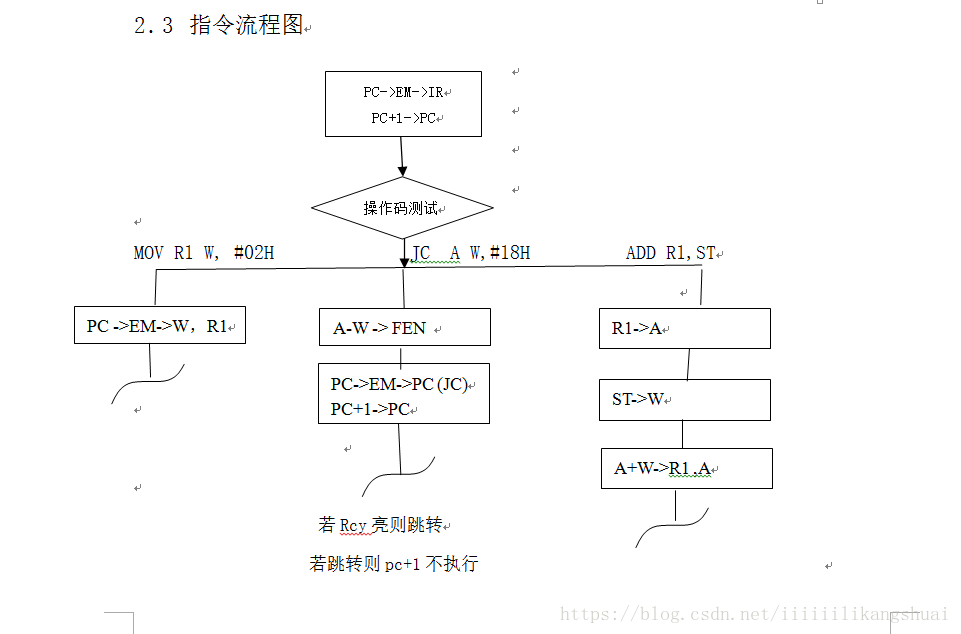

MOV R1 W, #02H | 09H | 02H | 将直接数02H存入R1和A |

MOV R3 ST, #01H | 0FH | 01H | 将直接数01H存入R3和ST |

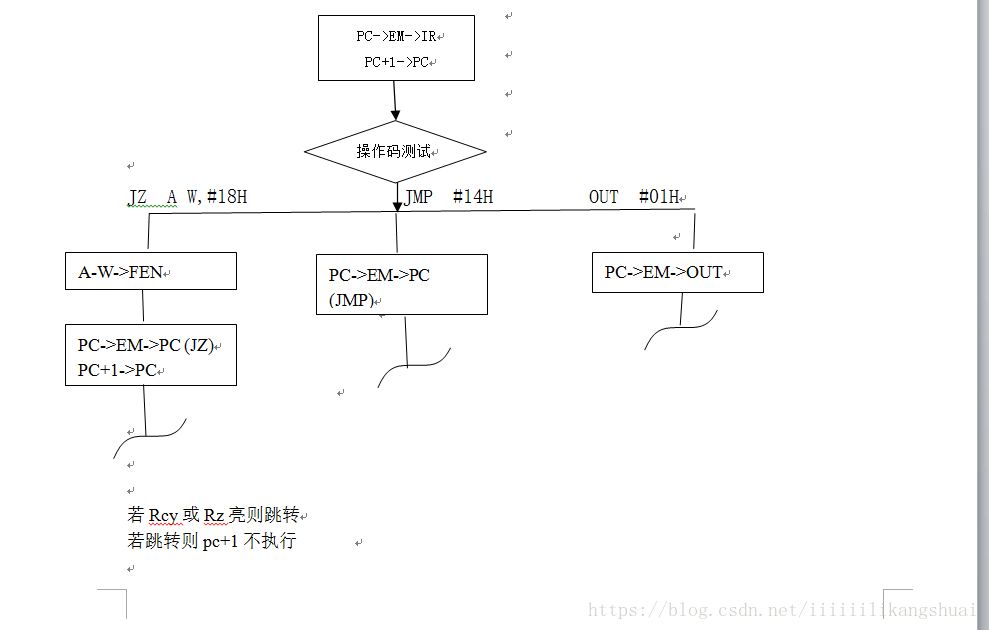

JC A W,#18H | 80H | 18H | A<W 则跳转到#18H地址 |

JZ A W,#14H | A4H | 14H | A=W 则跳转到#14H地址 |

ZERO R2 | 12H |

| 将R2置零 |

MOV A ,R1 | 15H |

| 将R1中数送至A |

ADDJC R2 A,#11H | C2H | 11H | 将R2加上A再送回R2和A, 溢出则跳转至11HS |

JC A R0, #0AH | 90H | 0AH | A<R0 ,则跳转至#0AH地址 |

JZ A W,#18H | A4H | 18H | A=W 则跳转到#18H地址 |

ADD R1,ST | 1DH |

| Ri自增 ST ,并存入R1和A |

JC A R0, #09H | 90H | 09H | A<R0 ,则跳转至#09H地址 |

OUT #01H | 20H | 01H | 从OUT输出 01H |

JMP #14H | B8H | 14H | 无条件跳转到14H地址 |

OUT #00H | 20H | 00H | 从OUT输出 00H |

JMP #18H | B8H | 18H | 无条件跳转到18H地址 |

2.2 内存数据

内存地址 | 数据 | 内存地址 | 数据 |

00H | 04H | 0EH | 0AH |

01H | 09H | 0FH | A4H |

02H | 02H | 10H | 18H |

03H | 0FH | 11H | 1DH |

04H | 01H | 12H | 90H |

05H | 80H | 13H | 09H |

06H | 18H | 14H | 20H |

07H | A4H | 15H | 01H |

08H | 14H | 16H | B8H |

09H | 12H | 17H | 14H |

0AH | 15H | 18H | 20H |

0BH | C2H | 19H | 00H |

0CH | 11H | 1AH | B8H |

0DH | 90H | 1BH | 18H |

2.5 微指令表

微指令表参见表2

3、设计结果

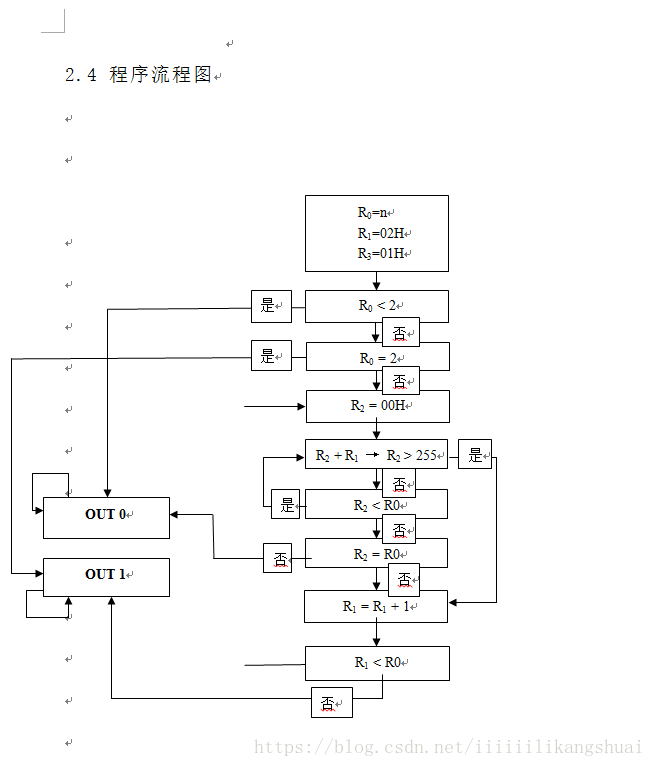

1.变量含义:

R0输入数据,判断R0是否是素数。

R1 循环变量,从02H开始自增。R0循环除以R1.

R2 R1的累加和,中间变量,和R0比较大小。

R3 常数01H

ST 常数01H

2.首先执行寄存器的初始化,对经常使用的几个变量进行初始化

3.主体程序:

特殊值:R0小于2,输出00H。R0等于2,输出01H.

判断是否能除尽:将R2循环加上R1,若大于或则等于R0则跳出循环,此时再判断R2是否等于R0,若等于说明R0除以R1能除尽,否则不能除尽。R2循环加R1时,若出现溢出也说明不能除尽直接执行,R1=R1+1.

判定素数:输入R0除以R1,除不尽,则R1自增,通过跳转重复执行以上步骤到 R1=R0(此时R0没有除以R1).则顺序执行输出 01H(是素数)。若判断是否能除尽时出现R0=R2,则说明R0不是素数,跳转输出00H.

4. 验证:

R0 = 00H OUT = 00H 否

R0 = 01H OUT = 00H 否

R0 = 02H OUT = 01H 是

R0 = 07H OUT = 01H 是

R0 = 06H OUT = 00H 否

R0 = FEH OUT = 00H 否

R0 = FFH OUT = 00H 否

以上数据都通过测试。

表2 微指令表

助记符 | 微地址 | 微程序 | X R D | E M W R | E M R D | P C O E | E M E N | I R E N | E I N T | E L P | M A R E N | M A R O E | O U T E N | S T E N | R R D | R W R | C N | F E N | X2 | X1 | X0 | W E N | A E N | S2 | S1 | S0 | 后续 微地址 | 操作说明 |

取指 | 00 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

IN R0 A,N | 04 | FFFB17 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | +1 | N->IN->R0,A |

| 05 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

MOV R1 W,#02H | 08 | C7FBEF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | +1 | PC->EM->R1,W |

| 09 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

MOV R3 ST,#01H | 0C | C7EBFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->R3,ST |

| 0D | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

JC A W,#18H | 80 | FFFEF9 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | +1 | A-W -> FEN |

| 81 | C6FFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->PC (JC),PC+1 |

| 82 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

JZ A W,#14H | A4 | FFFEF9 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | +1 | A-W -> FEN |

| A5 | C6FFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->PC (JZ),PC+1 |

| A6 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

ZERO R2 | 10 | FFFF8F | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | +1 | A->ALU->W |

| 11 | FFFB99 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | +1 | A-W->D->R |

| 12 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

MOV A,R1 | 14 | FFF7F7 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | +1 | R1->A |

| 15 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

ADD JC R2 ,#11H | C0 | FFF7EF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | +1 | R2->W |

| C1 | FFFA90 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | +1 | A+W->R2,A |

| C2 | C6FFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->PC (JC),PC+1 |

| C3 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

JC A R0,#0AH | 90 | FFF7EF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | +1 | R0->W |

| 91 | FFFEF9 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | +1 | A-W->FEN |

| 92 | C6FFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->PC (JC),PC+1 |

| 93 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

JZ A W,#18H | A4 | FFFE99 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | +1 | A-W->JZ |

| A5 | C6FFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->PC (JC),PC+1 |

| A6 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

ADD R1,ST | 1C | FFF7EF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | +1 | R1->A |

| 1D | FFFF4F | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | +1 | ST->W |

| 1E | FFFB90 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | +1 | A+W->R1,A |

| 1F | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

JC A R0,#09H | 90 | FFF7EF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | +1 | R0->W |

| 91 | FFFEF9 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | +1 | A-W->FEN |

| 92 | C6FFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->PC (JC),PC+1 |

| 93 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

OUT #01H | 20 | C7DFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->OUT |

| 21 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

JMP #14H | B8 | C6FFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->PC (JC),PC+1 |

| B9 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

OUT #00H | 20 | C7DFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->OUT |

| 21 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

JMP #18H | B8 | C6FFFF | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | +1 | PC->EM->PC (JC),PC+1 |

| B9 | CBFFFF | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P1 | PC->EM->IR,PC+1 |

2462

2462

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?