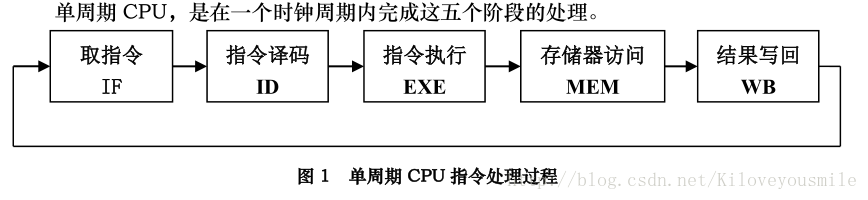

一、实验内容

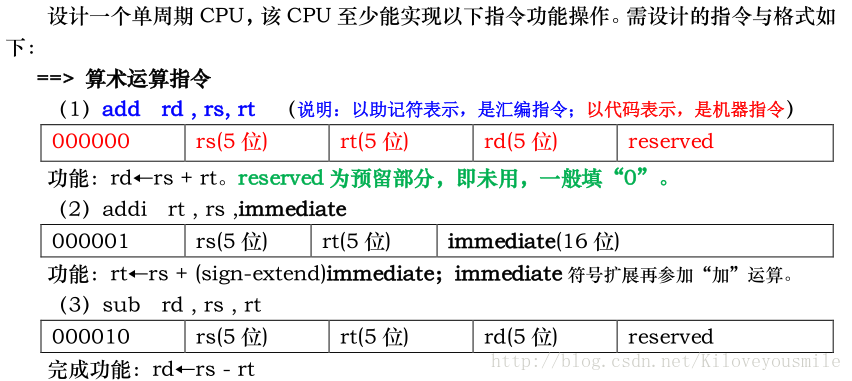

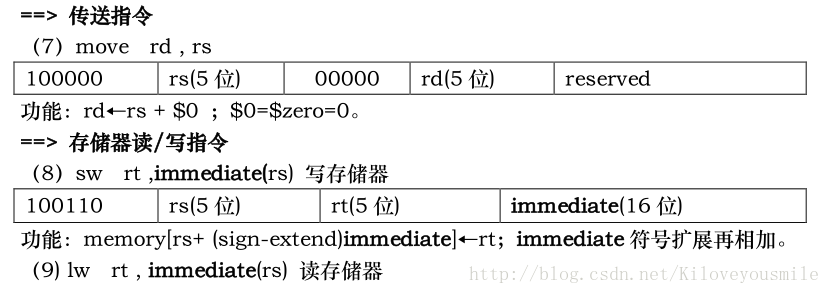

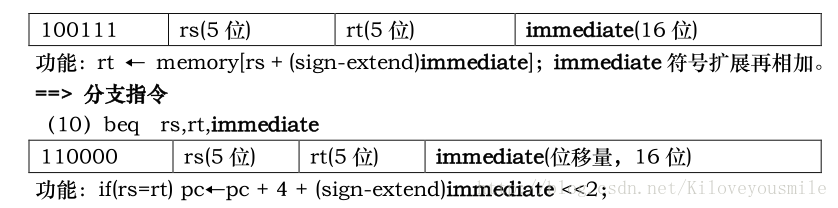

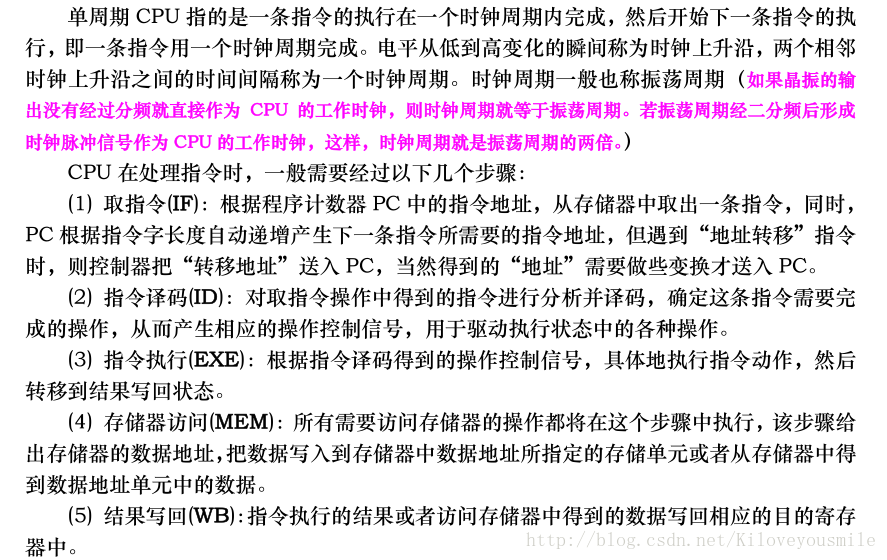

一、实验原理

三、分析

▶学会读数据通路图

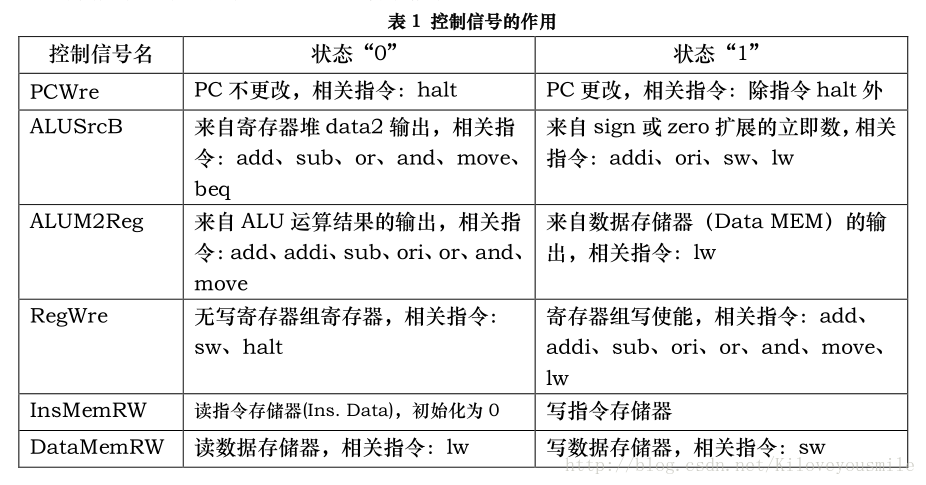

首先,我们了解各个信号的作用。上面的表格中已经给出了详细的作用,这里我再解释清楚一些。

☞ PCWre:控制PC的跳转。只有当PCWre = 1 时,PC才会跳转到下一条指令的地址,即+1(实验中为+4)。

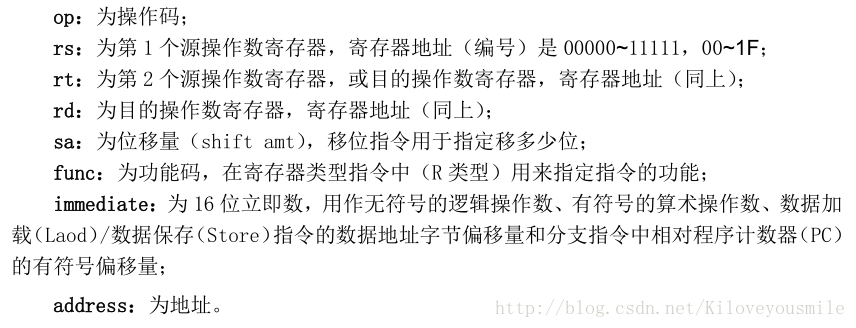

☞ ALUSrcB:是选用immediate作为第二个源操作数,还是从寄存器总读取第二个源操作数。当ALUSrcB = 1时,选去immediate作为第二个源操作数。

☞ ALUM2Reg:跟据上面的资料可知,每条指令的运算结果都要写入寄存器(当然,sw、halt除外)。需要经过ALU计算的指令,自然没有问题;但是,lw也要执行写入寄存器的步骤,但是它没有经过ALU单元的运算。为了统一,所以增加了一个二选一的数据选择器,以ALUM2Reg作为选择信号,ALUM2Reg = 1时,则选择数据存储器中的数据写入寄存器。

☞ RegWre:显而易见,RegWre是否执行写入寄存的信号。只有sw、halt指令不需要执行。

☞ InsMemRW:这个实验用不到把指令写入指令存储器的功能,默认为0即可。

☞ DataMemRW:数据存储器的读写功能。实际上,只有lw和sw需要使用到数据存储的读写功能;当DataMemRW = 1时,写入,DataMemRW = 0时,读取。为了统一,所以可以默认除了lw指令外,其他指令都需要数据存储器的写使能。

☞ ExtSel:immediate的扩展方式信号,当ExtSel = 0时,做零扩展;ExtSel = 1时,做符号位扩展。其实很简单,需要符号位扩展的一般是负数,扩展位都为1即可。

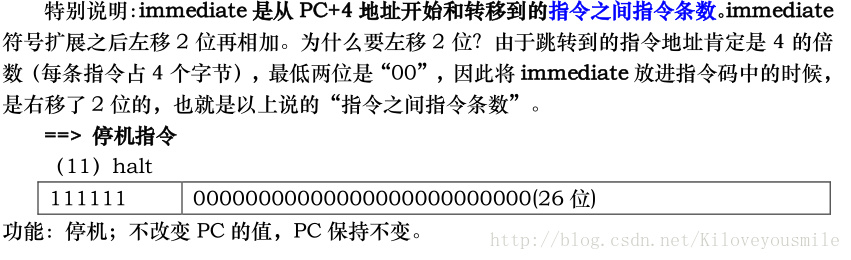

☞ PCSrc:又一个PC指令信号。只有beq指令执行时有作用,即PCSrc = 1时,PC = PC + 4 + 4 *(扩展后)immediate。

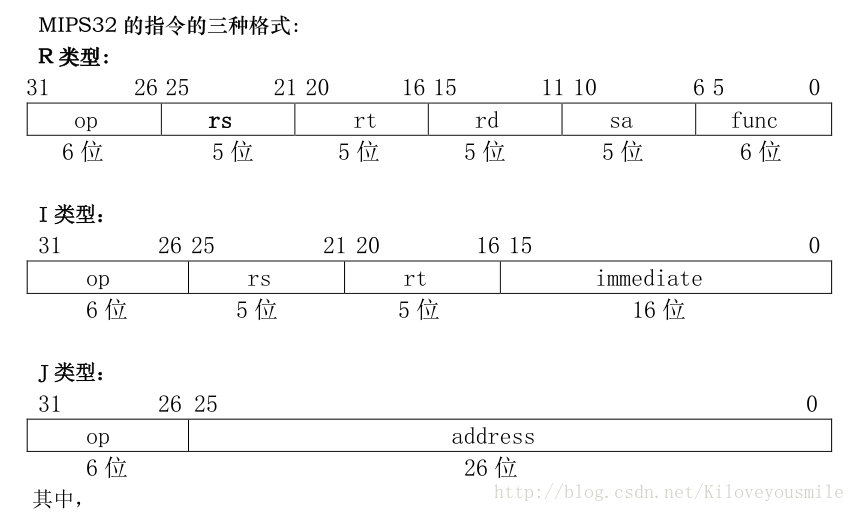

☞ RegOut:确定把结果写入那种寄存器。一共有rs, rt, rd三种寄存器,其中addi、ori、lw的运算结果要写入rt寄存器(需要写入rt寄存器的运算相关的指令,一般是rd寄存器不可用,属于I类型MIPS指令);其他的则写入rd段寄存器。

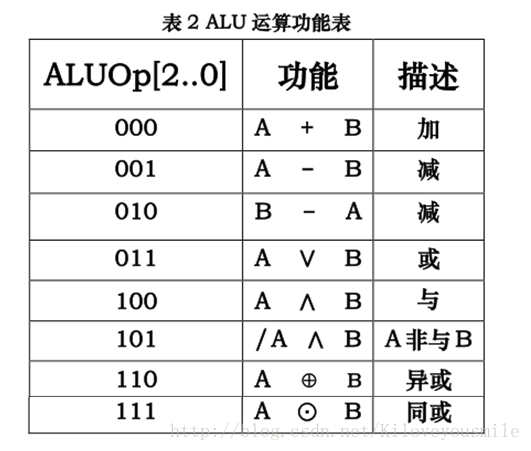

☞ ALUOp[2..0]:把opcode(6bit长度)转为ALU可识别的运算符,即AULOp(3bit长度)。

☞ zero:这个有什么用呢?主要是用来判断结果是否为零。实际上,用处不大,只是beq指令执行时才会起作用。通过ALU计算,若两个寄存器的值相减为零(即他们相等),则zero = 1, 这时候,PCSrc才能等于1,而PC才会执行跳转指令。即zero = 1 且 指令 = beq —> PCSrc = 1 —> PC = PC + 4 + 4 *(扩展后)immediate。

理解了这些,就有助于我们分析数据通路图了。我们分析一个简单的例子,如执行add指令。实现部分先执行,从PC开始,虚线部分后执行:

其他部分,也可以做类似的理解。

理解了图上部分,那么我们就可以开始着手实现CPU了。首先,需要安装好Linxise软件;安装好后,学习使用它,具体见下面的文档。

文档下载地址:http://download.csdn.net/detail/kiloveyousmile/9829135

代码实现时,要注意使用模块化思想。为了充分阐释,我们先实现一个模块。注意,输入数据为input端口,输出数据为output端口;input类型只能为wire类型,output则没有要求;若不声明数据类型,默认为wire类型。

以下是zero/sign extend模块的实现:

`timescale 1ns / 1ps

//

// Module Name: signZeroExtend

// Function: extend the immediate to 32 bits.

//

module signZeroExtend(

input wire[15:0] immediate,

input wire ExtSel,

output wire[31:0] out

);

assign out[15:0] = immediate;

/**

*ExtSel = 1 做符号位扩展;如果符号位为1,则扩展位为1,如果符号位为0,则扩展位为0

*ExtSel = 0 做0扩展

**/

assign out[31:16] = ExtSel? (immediate[15]? 16'hffff : 16'h0000) : 16'h0000;

endmodule根据数据通路图,可知其输入为immediate和ExtSel信号,输出为一个扩展数out。所以,书写方式如上图。

接下来,皆可以仿照这个,去实现各个模块了。具体,将在下一篇中说明。

9226

9226

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?