使用施密特触发器的电路设计以提高可靠性

1. 引言

电子器件的尺寸正接近原子级别,这要求制定新的设计准则以应对亚22 nm设计中的挑战。随着芯片制造工艺深入纳米尺度,工艺变异性抑制和抗辐射能力成为关键的可靠性要求。受工艺变异性影响的集成电路可能无法满足某些性能或功耗指标,导致参数良率损失,并需要多次重新设计步骤[1]。传统上,软错误(SE)源于来自空间或地面辐射的高能粒子与硅之间的相互作用[2]。然而,技术缩放引入了电荷共享现象和脉冲淬灭[3]。此外,工艺变化可能改变线性能量传递(LET),从而引发软错误。其后果是导致临时性的数据丢失,甚至在地面环境下也可能引发电路系统行为的严重故障。

工业界和学术界都在探索新型材料、结构、器件和设计策略,以将其应用于主流电路中,满足这些需求并避免不良影响。关于哪种方法是最佳途径的争论仍在继续,但有必要指出潜在的替代方案并进行深入研究。尽管与制造工艺变更相关的技术非常有效,但其成本高昂且复杂度高。在此背景下,本文探讨了施密特触发器电路,以确保FinFET逻辑单元的更高可靠性,并全面分析采用该技术的优缺点。此外,本文还将对另外三种电路级技术——晶体管重排序、去耦单元和睡眠晶体管[4–7]进行比较。

2. 评估方法论

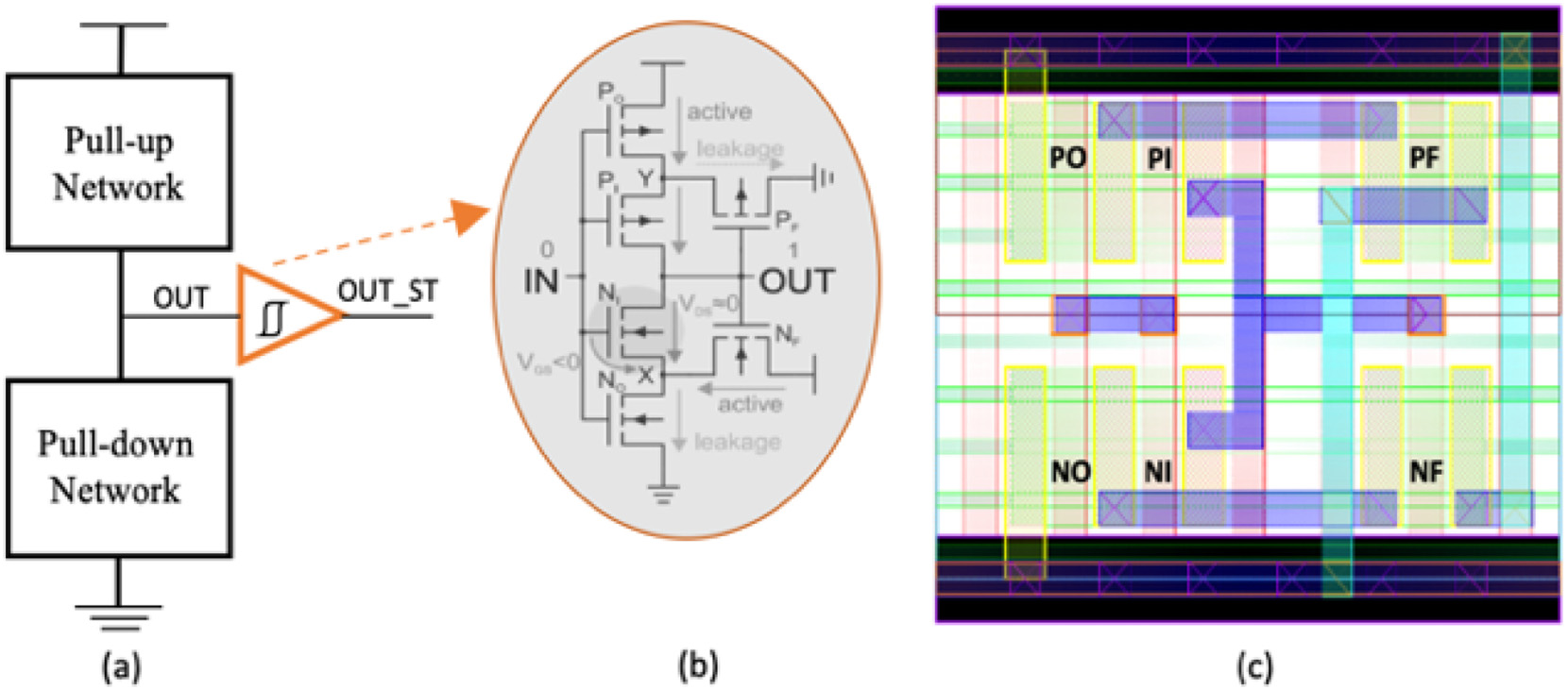

缓解策略是在单元输出端连接一个施密特触发器,如图1(a)所示,采用[8]提出的拓扑结构。施密特触发器具有固有的迟滞特性,可用于增强信号稳定性与抗噪声能力。PF和NF器件提供一种反馈方案,增大ION到IOFF的比值,从而最小化输出退化。由于内部晶体管(NI和PI)的栅源电压对切换点具有强影响,因此使用施密特触发器可减小工艺变化引起的电压传输曲线偏移,如图1(b)所示。此外,施密特触发器电路增加了输出节点的电容,降低了产生单粒子效应所需的临界电荷。

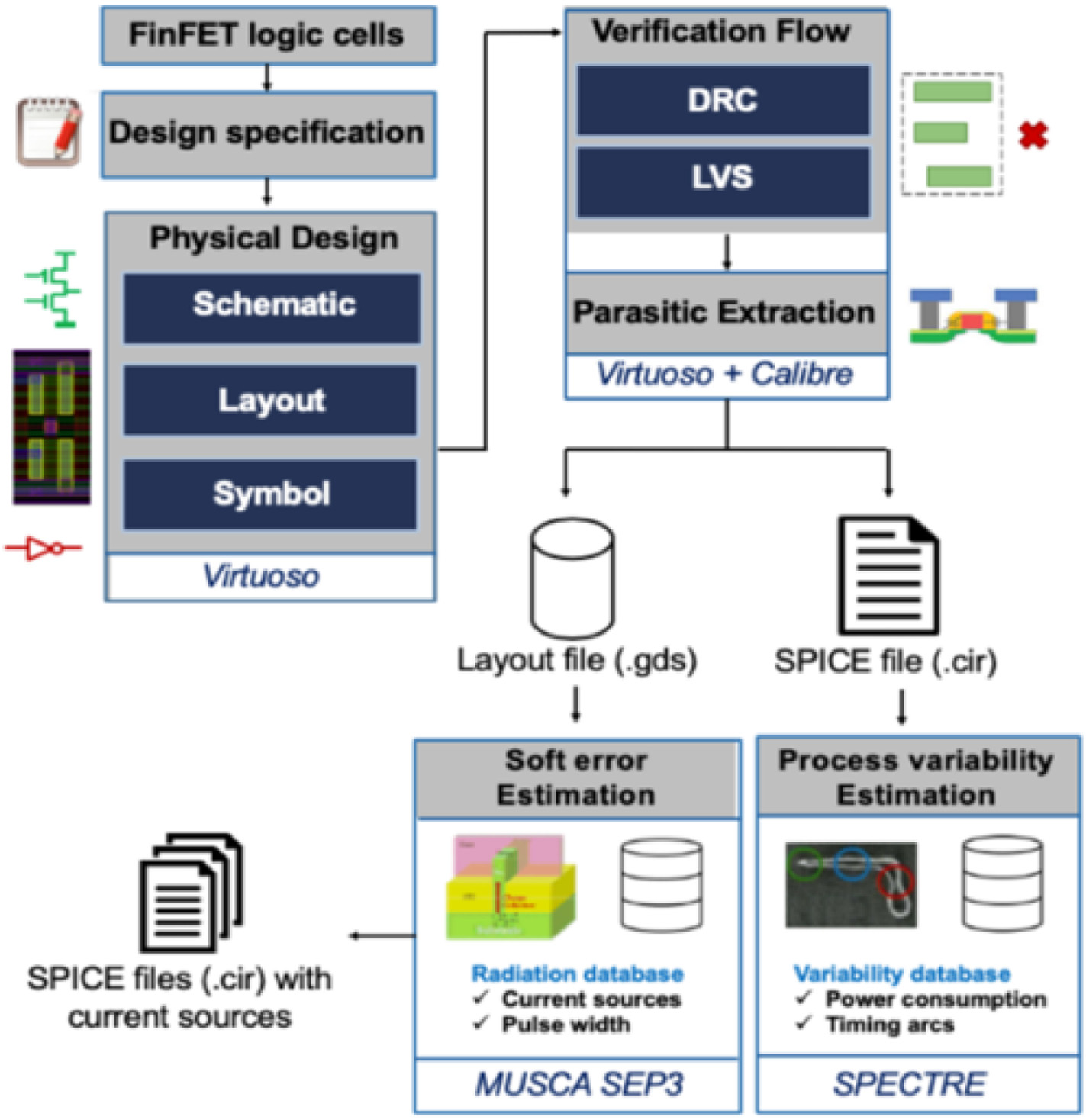

图2展示了本工作的所有步骤。首先,使用逻辑单元的传统版本执行整个设计流程。随后,将施密特触发器电路连接到每个FinFET逻辑单元中。本文采用由亚利桑那州立大学(ASU)与ARM有限公司合作开发的用于学术用途的7纳米FinFET工艺设计套件(PDK),称为ASAP7。ASAP7中的器件参数和版图层次概要见表1。所有版图均提交至验证流程,并进行寄生参数提取,施密特触发器的版图如图1(c)所示。实验中考虑了逻辑单元中所有晶体管相同的尺寸(三鳍片)。晶体管尺寸的影响仅在施密特触发器技术所引入的额外晶体管中进行探讨。

功函数波动(WFF) 导致 FinFET技术 中电路行为的主要偏差 [10]。工艺变异性通过2000次蒙特卡洛模拟引入[11],其中功函数(WF)参数被建模为具有 3σ偏差的高斯函数,这表示正态分布曲线的99.7%。由于工业界缺乏关于当前FinFET节点中这些值的信息,逻辑单元分别被施加了高(5%)、中(3%)和低(2%)水平的WF变化。归一化标准偏差(σ/μ)用于表示栅极对工艺变化的敏感性。由工艺偏差影响引起的功耗和延迟的偏差在本文中分别称为功耗和延迟变异性。

使用ONERA开发的MUSCA SEP3工具评估逻辑单元的单粒子敏感性[12]。MUSCA SEP3是一种辐射事件基于蒙特卡洛方法的生成器工具,该工具对高能粒子撞击物质直至产生瞬态脉冲的全过程进行建模。电流源包含内部和外部节点,并考虑逻辑单元中最易受影响的输入向量。每个晶体管的收集电荷通过逆向工程或利用来自GDSII文件的前端工艺(FEOL)报告计算得出。该工具还考虑了所有器件的电气特性。本研究在正常入射角和室温(27°C)条件下模拟重离子辐照。

FinFET器件的三维结构减少了暴露于电荷收集机制下的硅体积,从而降低了单粒子敏感性[13]。使用ASAP7 PDK时,FinFET器件在 0.7 V至0.5 V的电压区间内对软错误具有免疫能力。然而,技术缩放增加了由电池供电的便携式设备数量[14]。超低功耗应用的需求突显了采用电压缩放等方法来最小化功耗的必要性,但低电压使电路更容易受到辐射效应的影响。因此,本文评估了近阈值区域下的单粒子效应。逻辑单元在低线性能量传递(LET)条件下进行评估,即小于15 MeV·cm² · mg⁻¹,这对应于航空电子设备和地面应用中由质子或中子引发的代表性次级粒子。同时也在较高LET(30至58 MeV·cm² ·mg⁻¹)条件下研究了单粒子敏感性,以代表空间环境。本工作采用截面作为品质因数来估算 FinFET单元的单粒子敏感性。若受影响节点的电压幅度超过栅极阈值电压(VDD/2),则判定为发生故障。

3. 使用施密特触发器提高可靠性

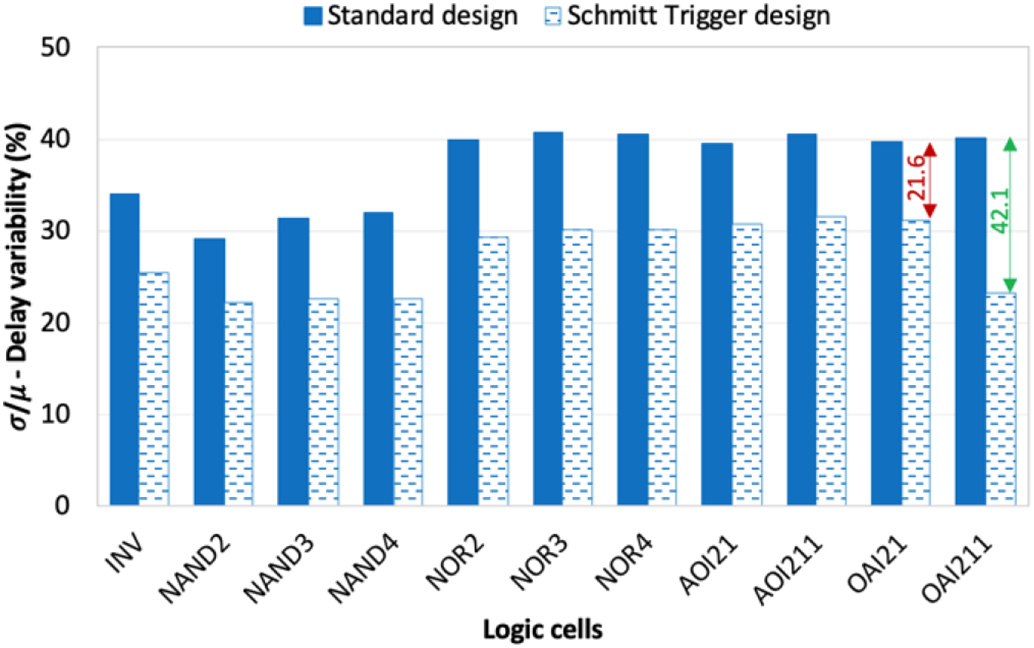

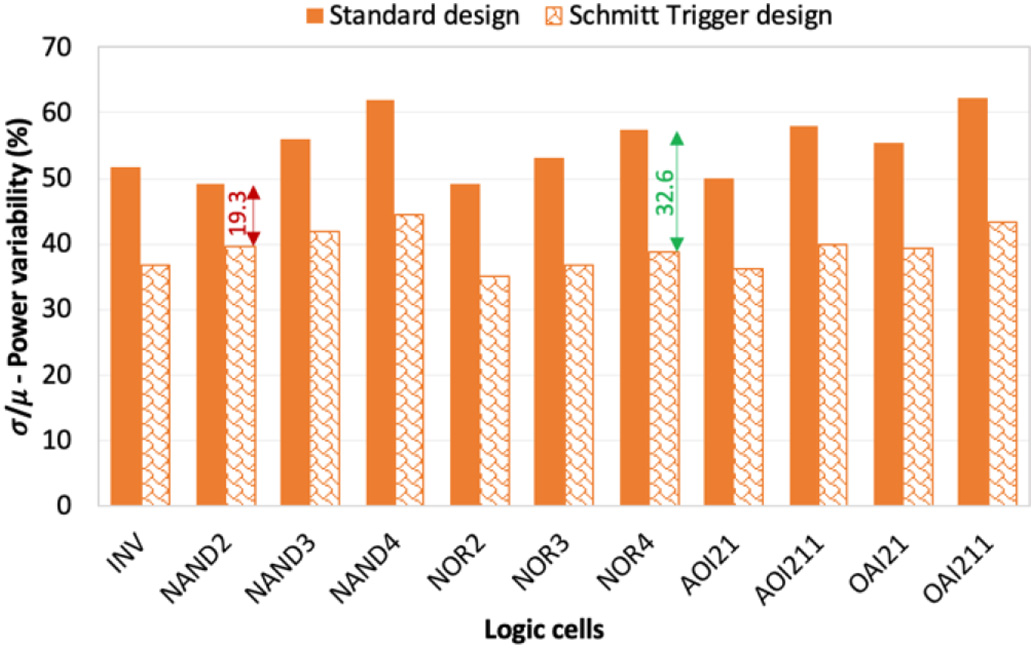

在设计中使用施密特触发器电路可最大程度地减小工艺变化对延迟和功耗的影响,如图3和图4所示,针对一组在标称条件下偏差为5%的 FinFET单元。对于OAI211逻辑单元,延迟改善可达42.1%。即使 OAI21是受益最少的使用施密特触发器设计,增益仍然显著,延迟影响降低了21.6%。另一方面,NAND2单元在采用施密特触发器设计时功耗改善最小。施密特触发器设计使工艺变化对功耗的影响减少了约19.3%。在工艺变化下最鲁棒的单元是或非门4,其在功耗上的增益达到了32.6%。

表2显示了当逻辑单元受到不同水平的工艺波动影响时,延迟可变性缓解的趋势。采用施密特触发器设计的逻辑单元在考虑2%、3%和5%的最坏情况工艺波动时,其延迟可变性的平均值(AVG)分别约为 9.17%、14.23%和27.17%。增量关系(Δ)指定了使用ST电路而非标准版本(std)设计逻辑单元时,对工艺变化敏感性的变化程度。除了反相器(INV)和与非门(NAND)单元(以灰色突出显示)外,随着最坏情况工艺波动水平的降低,ST设计的优势逐渐增加。例如,若 AOI21单元在2%、3%或5%的变化水平下采用ST设计,则与标准版本相比,其延迟影响分别减少了36.4%、31.6%和21.6%。对于反相器和与非门单元,在偏离标称条件3%的变化水平下实现了最佳的缓解效果。

所有研究的逻辑单元的功耗波动衰减趋势相同。随着最坏情况工艺波动水平的提高,施密特触发器的优势也随之增加。与标准设计相比,施密特触发器技术在2%、3%和5%的工艺波动水平下,分别使 NAND2单元的功耗波动降低了4.5%、11%和19.3%。NAND2和 NOR4仍然是逻辑单元

| 表1 来自ASAP7的器件参数和版图层次 | |

|---|---|

| 器件参数 | |

| 栅极长度 | 21 纳米 |

| 鳍片厚度 | 6.5 nm |

| 鳍片高度 | 32 nm |

| 氧化层厚度 | 2.1 nm |

| 沟道掺杂 | 1 × 10²² m⁻³ |

| 源漏掺杂 | 2 × 10²⁶ m⁻³ |

| 功函数 NFET | 4.3720 电子伏特 |

| PFET | 4.8108 电子伏特 |

| 布局层(纳米) | |

| 宽度 | 间距 |

| Fin | 6.5 |

| 有源区 | 54 |

| Gate | 21 |

| SDT/LISD | 25 |

| LIG | 16 |

| VIA0‐3 | 18 |

| M1–M3 | 18 |

| 表2 不同最坏情况工艺波动水平对延迟的影响。红色和绿色的数值分别对应使用施密特触发器技术的最小和最大改进程度。 | |||

|---|---|---|---|

| 逻辑单元 | 工艺波动 2% | 工艺波动 3% | 工艺波动 5% |

| std (%) | ST (%) | Δ (%) | |

| INV | 13.8 | 12.6 | -8.7 |

| NAND2 | 14.2 | 12.8 | -9.9 |

| NOR4 | 13.5 | 12.4 | -8.1 |

| AOI21 | 15.6 | 9.9 | -36.4 |

| OAI21 | 14.8 | 13.5 | -8.8 |

| OAI211 | 15.1 | 13.7 | -9.3 |

在分别考虑2%和3%的变异水平时,对功耗波动的抑制效果更小但增益更高。

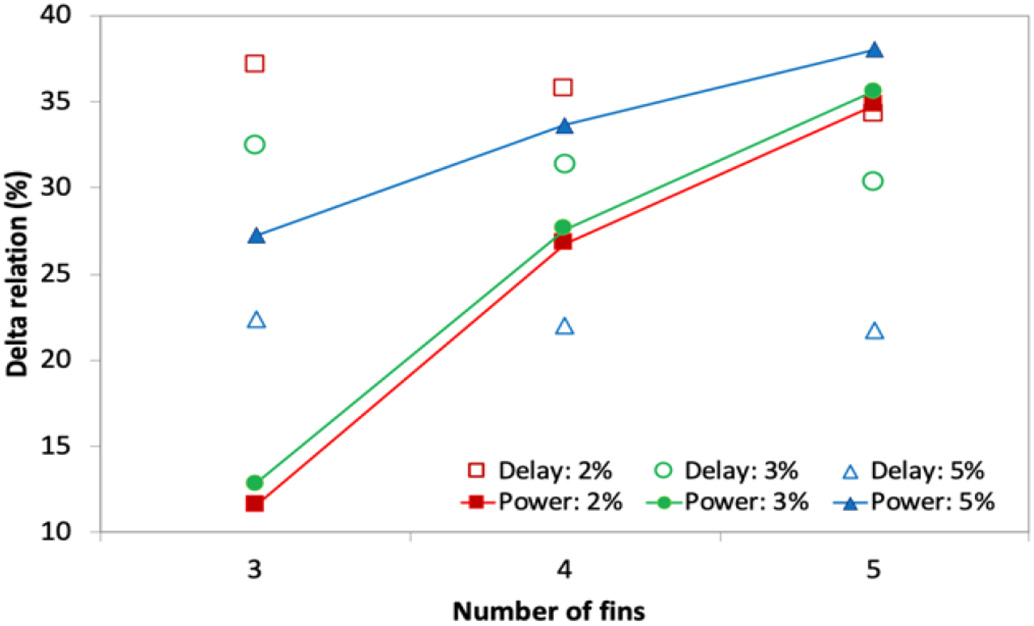

不同鳍片数量的施密特触发器设计对AOI21单元输出影响如图5所示。较大的施密特触发器显著降低了功耗波动的影响。例如,当工艺偏差为 2%、3%和5%时,与三鳍结构布局相比,采用五鳍结构的施密特触发器分别将功耗波动改善了23.2%、22.8%和10.8%。对于经受较低WFF水平的电路而言,增加鳍片数量更具优势。另一方面,无论WFF水平如何,较大的施密特触发器对延迟可变性缓解的贡献均不足3%。在所有其他被研究的逻辑单元中也观察到了相同的行为。

对NAND2、NOR2和AOI21单元在低和高LET(5至58 MeV·cm²· mg⁻¹)下的SE敏感性进行了分析。此外,测试了所有输入向量,并将核心电压调节至近阈值区域(0.3伏特)。结果表明,ST设计在软错误缓解方面非常有前景。ST技术使逻辑门几乎不受故障影响,且该效果独立于所应用的LET、输入向量或核心电压。

4. 与其他电路级技术的比较

据我们所知,目前仅有少数研究专注于采用电路级方法来提高鳍式场效应晶体管电路对软错误和工艺变异性的鲁棒性[15–19]。双互锁逻辑被证明即使在双节点击穿情况下也对瞬态脉冲效应(SET)影响具有抗性使用14纳米FinFET技术[15]。在16纳米FinFET节点下,于近阈值区域研究了三种冗余类型(空间冗余、时间冗余和混合冗余)以缓解单粒子瞬态,在[16]中进行了探讨。在7纳米FinFET技术下,研究了采用多级设计替代复杂单元作为一种缓解策略,在[17]中进行了分析。在 7纳米FinFET节点设计的鳍式场效应晶体管全加器中,用施密特触发器替代传统反相器显著降低了工艺变异性敏感性,在[18]中得到了验证。基于10纳米FinFET节点,文献[19],探讨了利用低通滤波器和冗余策略提升单粒子瞬态鲁棒性的方法。

我们之前的研究考虑了三种提高可靠性的方法:晶体管重排序[4], 、 去耦单元[5,6],和睡眠晶体管[7]。晶体管重排序是指在保持相同逻辑功能的前提下,将给定网络中的串联晶体管在电路图中放置于不同的位置。在电路输出端采用去耦单元是一种电容性方法,用于降低信号线上的噪声并增加输出节点的临界电荷。在下拉网络与地线之间使用睡眠晶体管是一种电源门控技术,其作用相当于供电电压调节器。

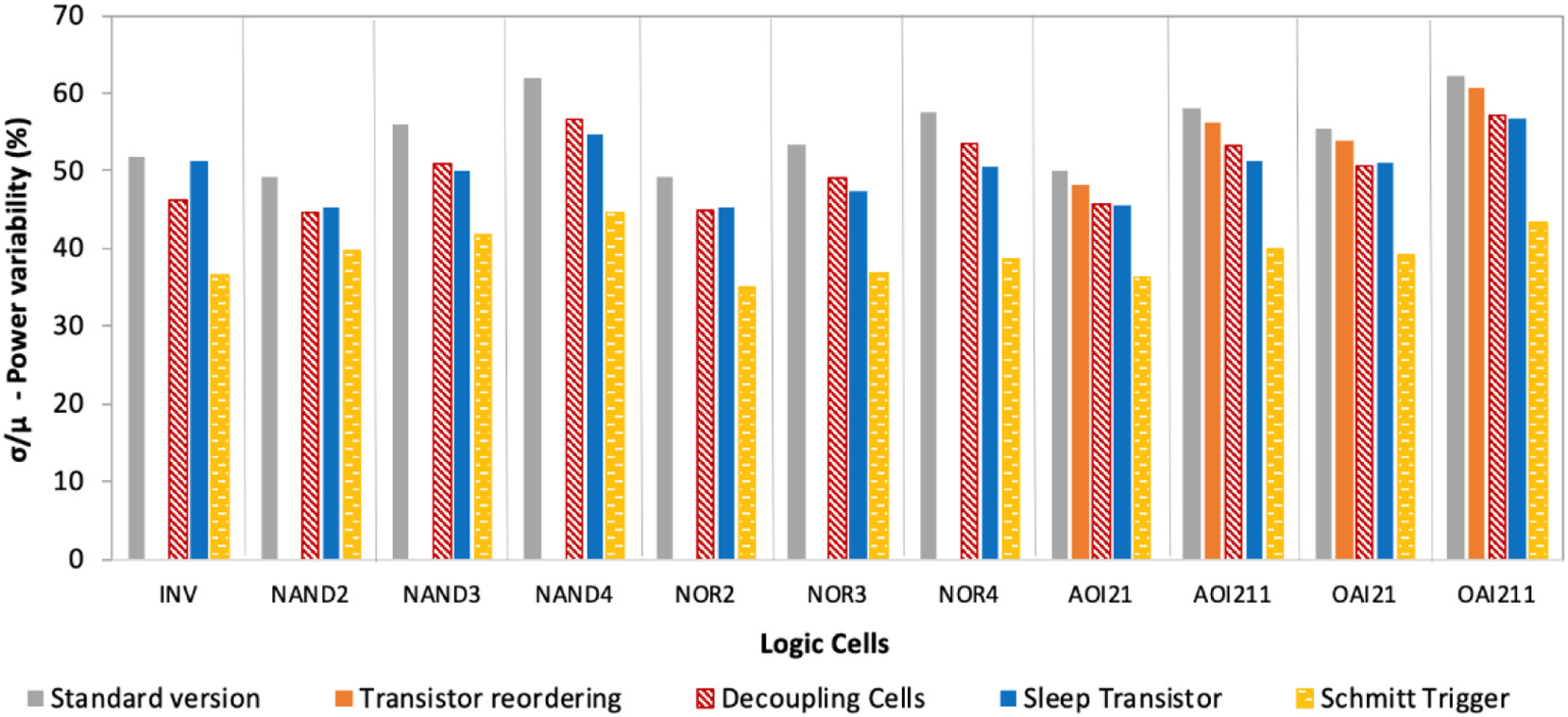

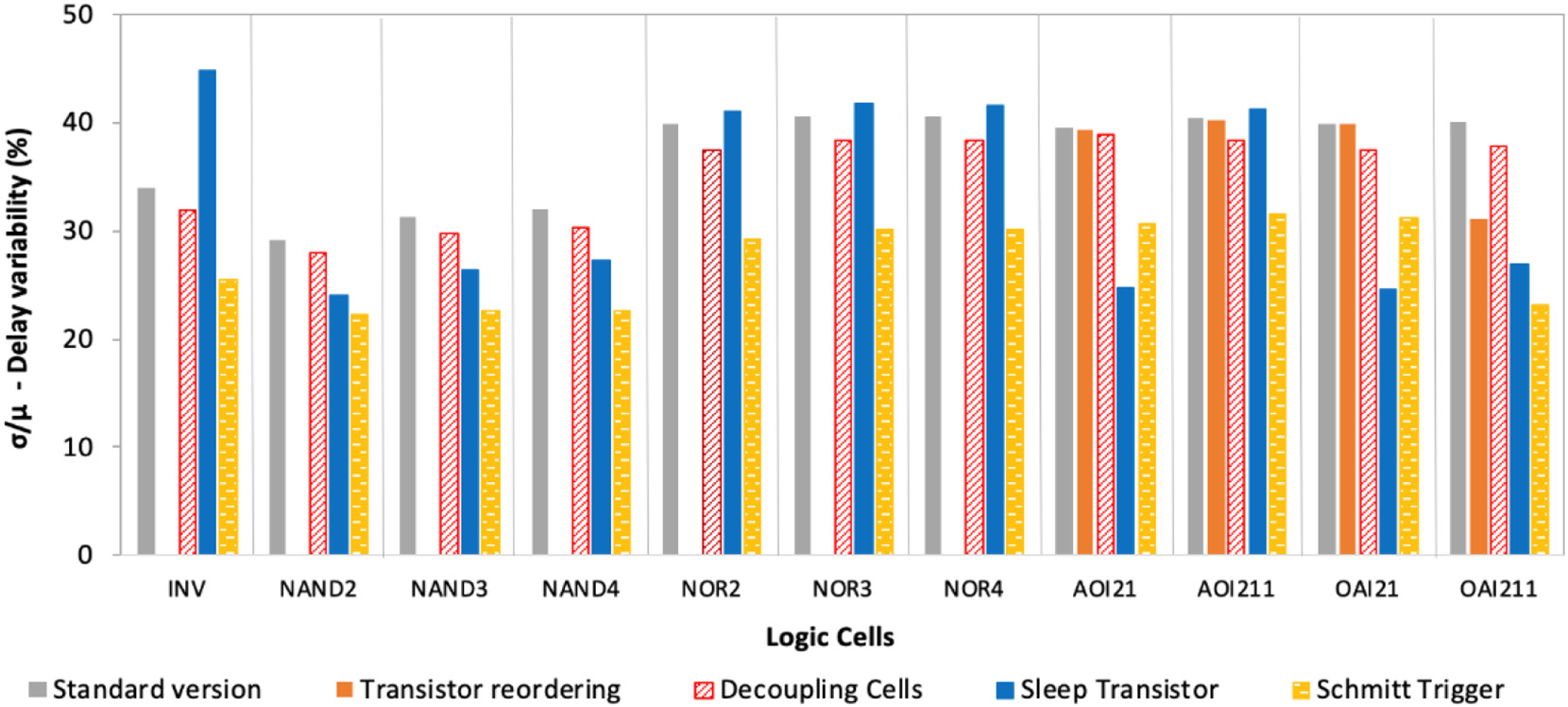

在考虑标准版本、施密特触发器设计以及三种其他电路级缓解方法的情况下,单元对5%最坏情况工艺波动的敏感性[4–7]分别在图6和图 7 中针对功耗和延迟变异性进行了比较。施密特触发器设计在减弱工艺偏差对功耗的影响方面,比其他三种方法至少高效4.9%。晶体管重排序仅应用于复杂门电路,对功耗波动的改善增益小于2%。

在延迟可变性缓解方面没有明显的规律。除了AOI21和OAI21单元外,ST设计是改善延迟波动的最佳方法。与睡眠晶体管和去耦单元设计相比,施密特触发器设计的最大增益分别约为19.4%和14.6%。对于 NAND和OAI211单元,使用睡眠晶体管的效果优于去耦单元,而在 INV、NOR和AOI211单元中情况相反。OAI211是唯一在晶体管重排序方法下表现出显著优势的逻辑单元。

| 表3 采用3鳍的电路级技术的面积影响。 | ||||

|---|---|---|---|---|

| 技术 | 额外设备 | 输入数量对应的面积(nm²) | ||

| 1 | 2 | 3 | ||

| 标准版本 | 0 | 50.9 | 67.8 | 84.8 |

| T. 重排序 | 0 | – | – | 84.8 |

| 施密特触发器 | 6 | 169.6 | 186.5 | 203.5 |

| 去耦单元 | 4 | 169.6 | 186.5 | 203.5 |

| 睡眠晶体管 | 1 | 67.8 | 84.8 | 101.7 a |

a 这些值会因 OAI 逻辑单元而改变。

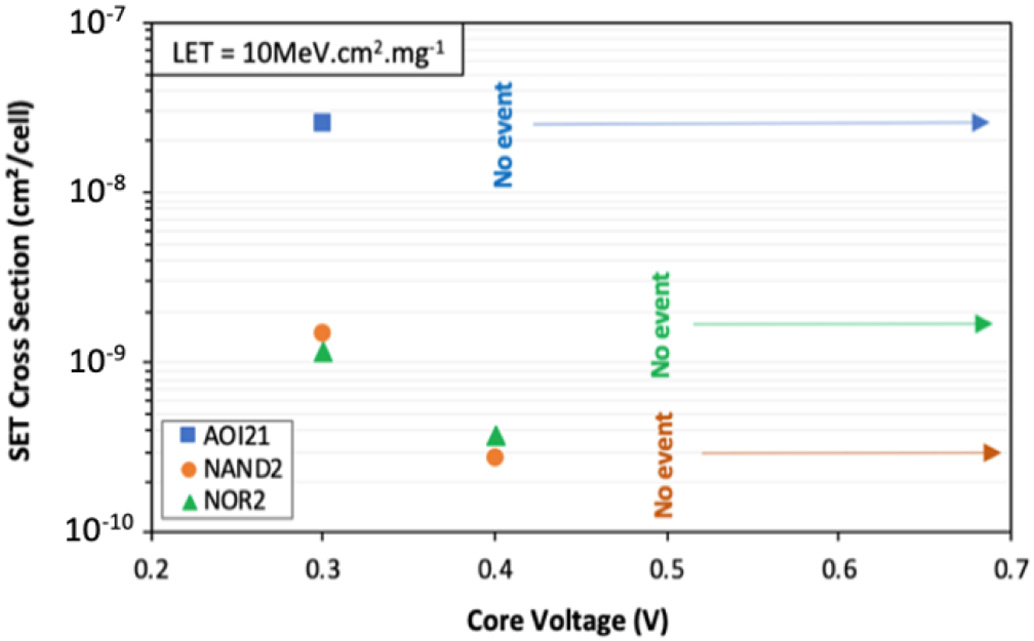

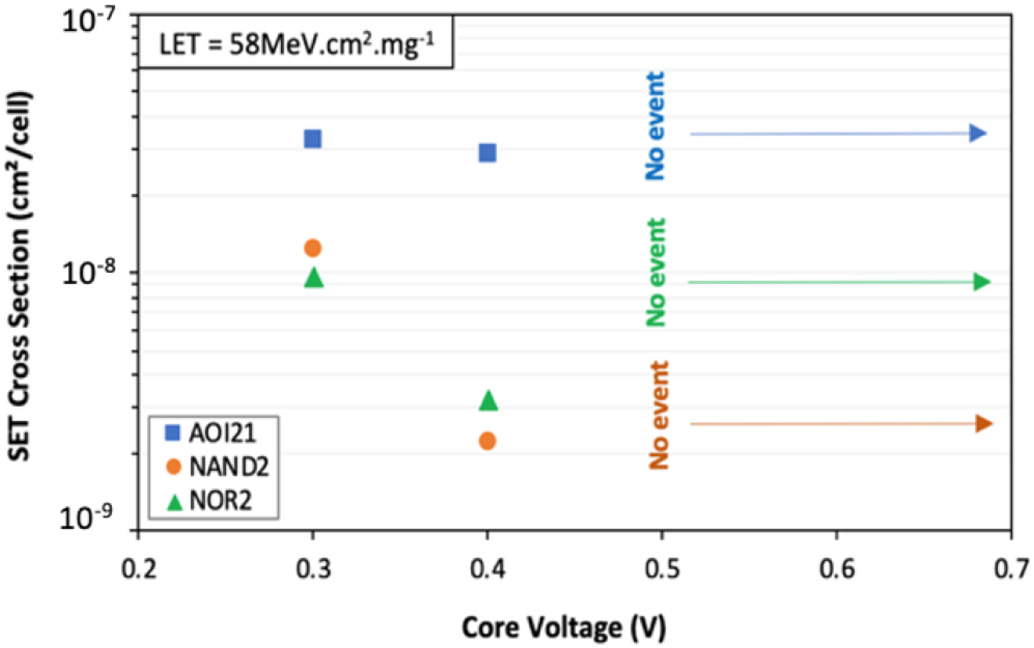

图8和图9比较了在LET为10 MeV·cm² ·mg⁻¹和58 MeV·cm² ·mg⁻¹时,AOI21、NAND2和NOR2单元在不同供电电压下的单粒子瞬态截面。由于FinFET器件的三维结构,所有门电路仅在低于0.4 V的电压下观察到效应。在10 MeV·cm² ·mg⁻¹条件下,AOI21单元是唯一在0.4 V时对软错误免疫的单元。在0.3 V时,NOR2单元对软错误影响的鲁棒性比 NAND2单元高约21%。然而,在0.4 V时情况相反,此时NAND2门对单粒子效应的敏感性降低。误差条定义为一个除以代表蒙特卡洛模拟引起的统计误差的单粒子瞬态数量的平方根。

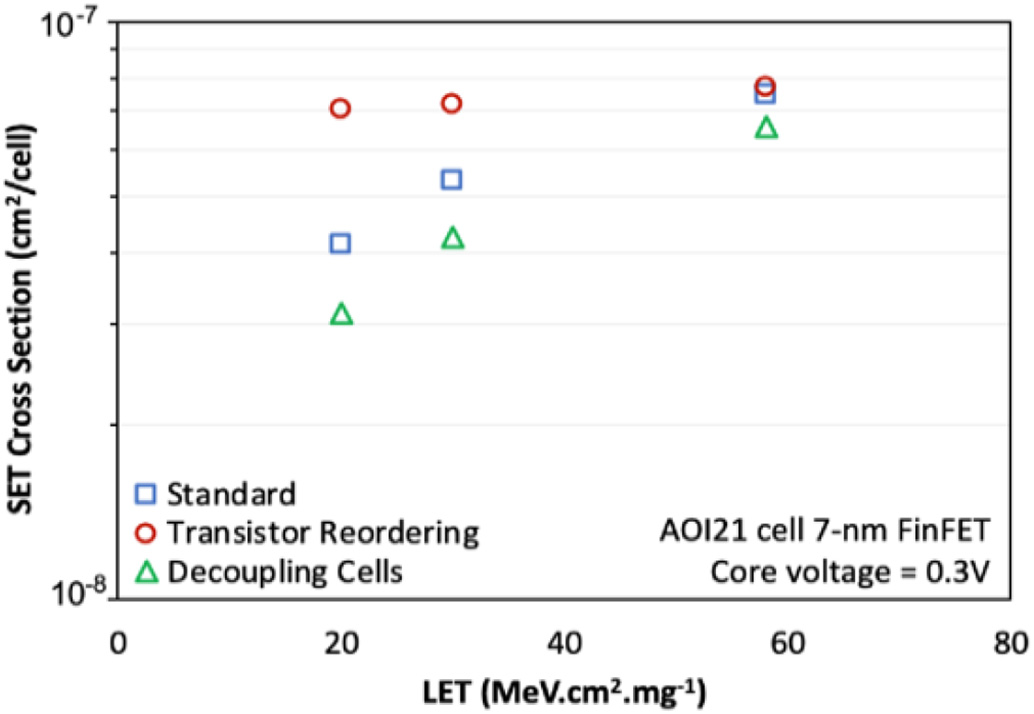

考虑到AOI21逻辑单元在近阈值电压(0.3伏特)下最容易受到单粒子效应影响,图10 展示了使用三种版图版本的单粒子瞬态截面。标准版图对应于传统设计,未采用缓解方法。晶体管重排序不利于软错误衰减,因为它增加了单粒子效应脆弱性。另一方面,去耦单元减少了当LET等于20、30和58 MeV·cm² ·mg⁻¹时,软错误敏感性分别约为23.7%、19.8%和11.4%。采用施密特触发器或睡眠晶体管的设计对单粒子效应免疫,因为在逻辑单元输出中未观察到任何事件。因此,结果未在图10中展示。

4.1. 技术缺点

施密特触发器设计是一种有趣的缓解工艺偏差和辐射引起的软错误的方法,如第3节所述。然而,这种方法会带来巨大的面积、延迟和功耗开销。表3展示了施密特触发器及其他方法的面积开销[4–7],以及晶体管上评估的单元的面积开销。

重排序技术具有三个或四个输入,本研究对于单输入和双输入函数的晶体管重排序技术在面积方面没有结果,因此在表3中用(–)表示。采用具有三个鳍式结构的施密特触发器的逻辑单元面积可增加2.2×至3.3×倍,具体取决于输入数量,如表3所示。施密特触发器设计每增加一个鳍片,面积增加17.2%。晶体管重排序是最佳技术,因为与标准电路相比,它没有面积开销。

在逻辑单元输出端插入去耦单元或施密特触发器会引入不同数量的额外晶体管,但两者的面积开销相同。这是由于ASAP7 PDK的限制,导致在交叉耦合模式下调整每个晶体管输入时需要占用更多空间。使用睡眠晶体管会使逻辑单元的面积略有增加,在大多数情况下,面积增加范围为1.2×到1.8×。扩散断开需要两个虚拟栅极,使得采用睡眠晶体管设计的OAI21和OAI211单元的预估面积分别增加约33%和28%。

这些技术与标准功耗和延迟预期行为相比对功耗和延迟的影响如图11所示,适用于所有逻辑单元,并考虑了5%的WFF偏差以及具有三个鳍的额外晶体管。晶体管重排序和去耦单元技术对功耗的影响最小。平均而言,晶体管重排序的影响约为11%,插入去耦单元的影响为15%。此外,这两种技术对电路逻辑和功耗增加的依赖性较小,其功耗结果集中在图11的同一区域。在延迟方面的最小平均影响也出现在使用去耦单元或晶体管重排序的情况下,分别达到21.2%和3.5%。

另一方面,睡眠晶体管和施密特触发器技术对电路功能表现出较大的依赖性,无论是在功耗还是延迟方面。睡眠晶体管设计为每个逻辑单元引入了约33%的功耗开销。即使去耦单元在设计中需要更多的晶体管,交叉耦合模式仍有利于降低功耗。施密特触发器设计在功耗方面受到更大的平均影响,约为45%。对于所有缓解方法,当WFF水平较低且尺寸更大时,功耗开销甚至进一步增加,其中睡眠晶体管设计在统计上受这两个因素的影响最小。然而,当采用睡眠晶体管而非施密特触发器时,延迟开销降低了约36%。

观察所评估技术的电路依赖性,如图12所示,基本反相器单元受所有技术的影响最大。图12 还清楚地表明了施密特触发器在功耗方面对所有被评估电路带来的显著劣势,以及对AOI211延迟的突出影响。在任何情况下,晶体管重排序或去耦单元技术对延迟或功耗的影响均超过20%。睡眠晶体管的开销与电路功能关系最为密切,其延迟影响范围可从极低水平(或非门功能为2.5%)到反相器门超过60%。此外,作为一种除了反相器单元的延迟影响大于功耗影响外,去耦单元技术在低水平 WFF下的延迟惩罚会减小。较大的睡眠晶体管可降低对延迟的影响,但如果在输出端连接了去耦单元或施密特触发器,则随着尺寸增大,延迟开销的影响也会增加。

5. 结论

本研究探讨了一种基于在设计中插入ST的电路级方法,以提高 FinFET单元对工艺偏差和辐射引起的软错误的鲁棒性。ST设计是一种有前景的方法,可在所有研究场景下获得更可靠的逻辑单元。除 NAND和INV单元外,该技术在较低WFF水平(2%)下对延迟变异性更具优势。随着WFF水平的升高,在大多数FinFET单元中,功耗波动的改善效果也更加显著。增大ST尺寸对延迟变异性并无益处,但对于功耗波动可能是一种可行策略,尤其是在较低WFF水平下。此外,ST设计对于所研究的所有LET和供电电压几乎对软错误免疫。

然而,根据设计要求的不同,使用其他方法可能更为合适,因为其在面积、延迟和功耗惩罚方面更具优势。因此,对于可靠性要求较高的设计,插入ST更为可取。对于有面积限制的设计,睡眠晶体管更适用于可靠性提升。而对于存在功耗或延迟限制的设计,则建议使用去耦单元。尽管晶体管重排序涉及的惩罚较小,但该技术在降低单粒子敏感性方面效率不高,且对工艺偏差的抑制效果在统计上并不显著。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?