本人设计了一款同步峰值电流模BUCK型DCDC芯片。输入范围6~28V,输出5V,负载电流0~3.5A。

测试时VIN=28V,VOUT=5V,Iload=0~3.5A。且测试是裸片金丝键合到PCB板进行的。

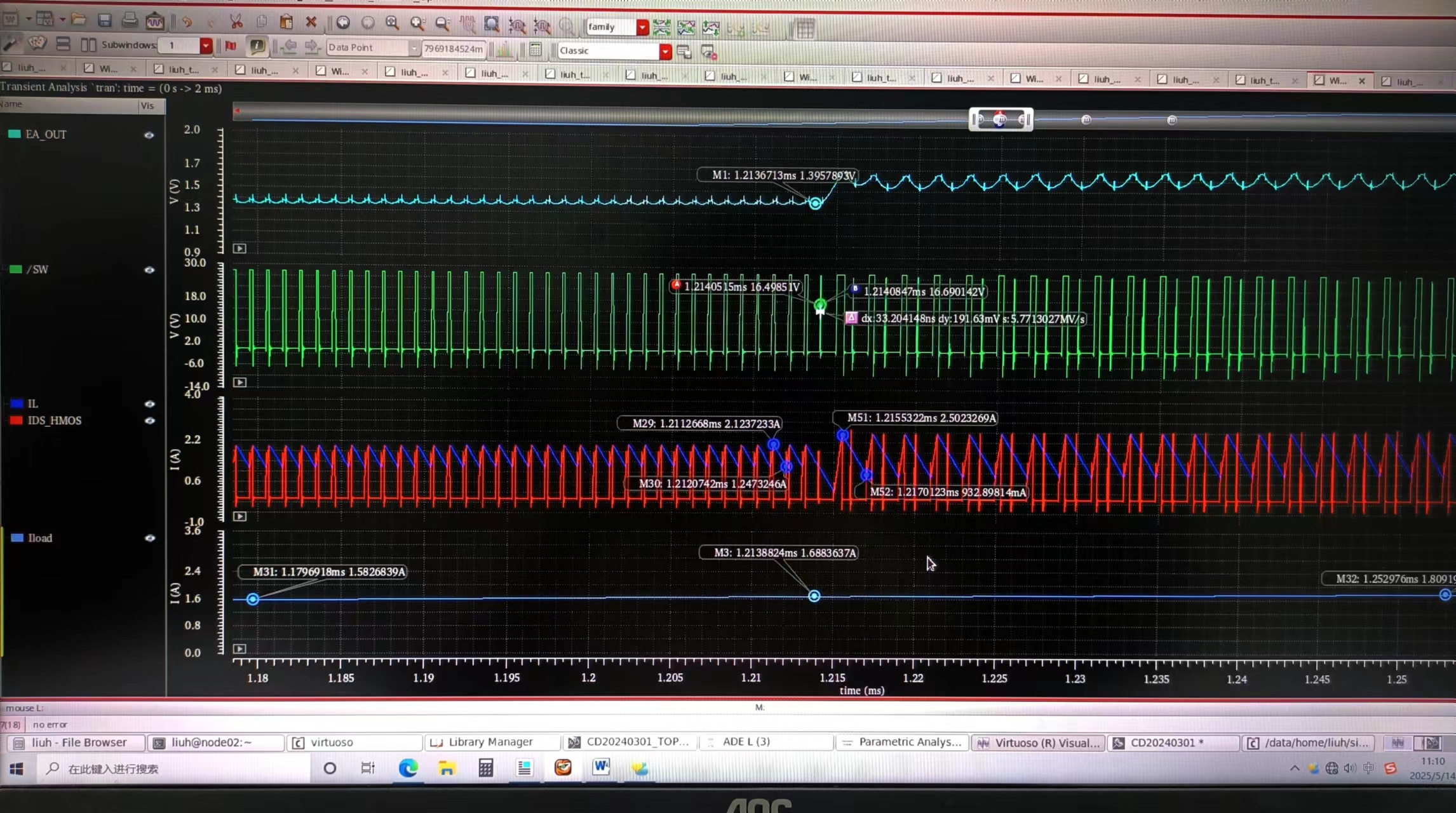

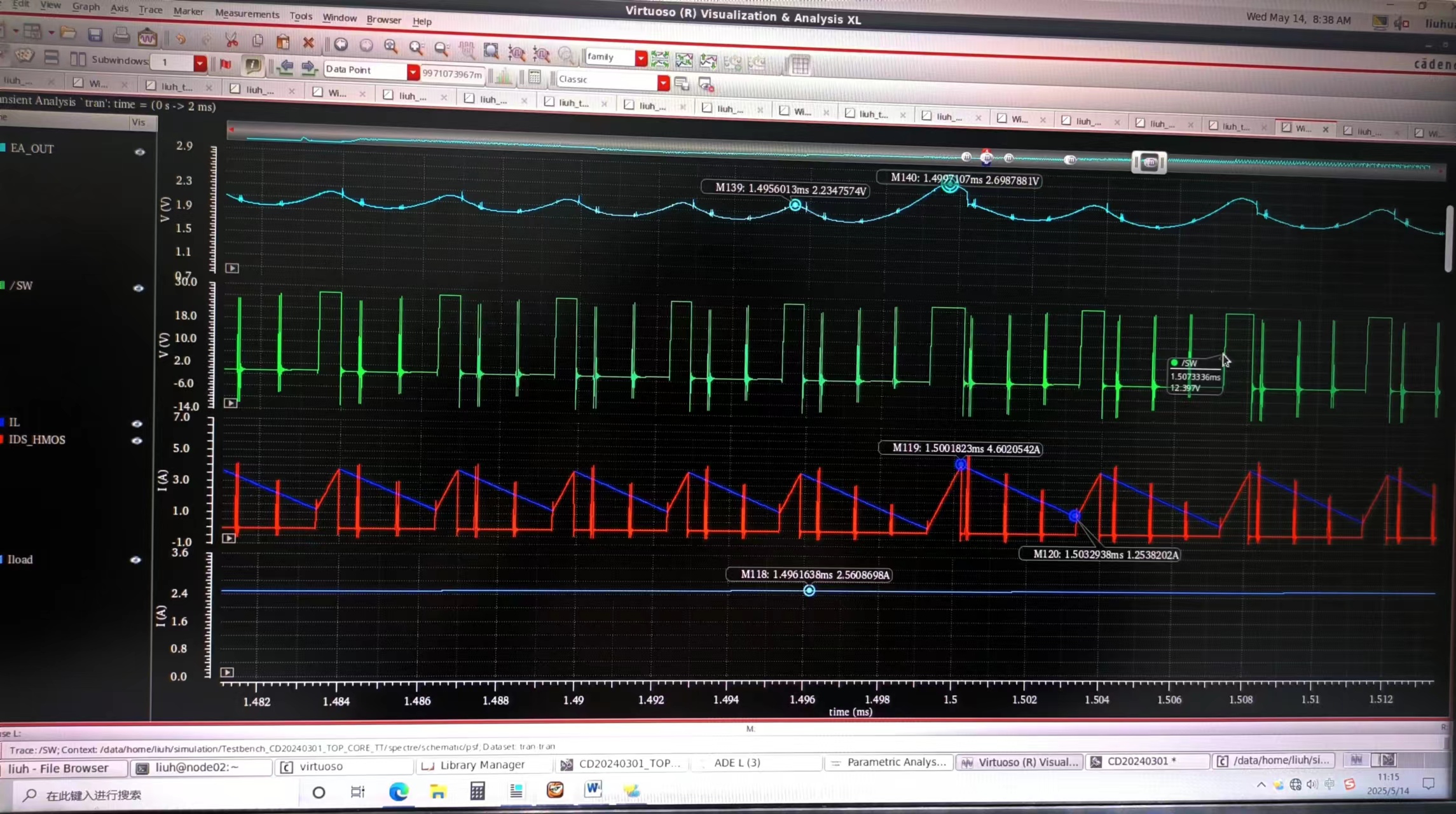

当负载电流较小时,测试一切正常,但当我不断增加负载电流时,一旦超过某一值就出现了异常降频的现象,如下图:(信号依次是:误差放大器输出电压、开关节点电压、功率电感电流、上功率MOS管的漏源电流、负载电流)。如图1,可以看到:

当Iload<1.68A时,系统工作正常,SW占空比一致且正常,工作频率为1MHz。

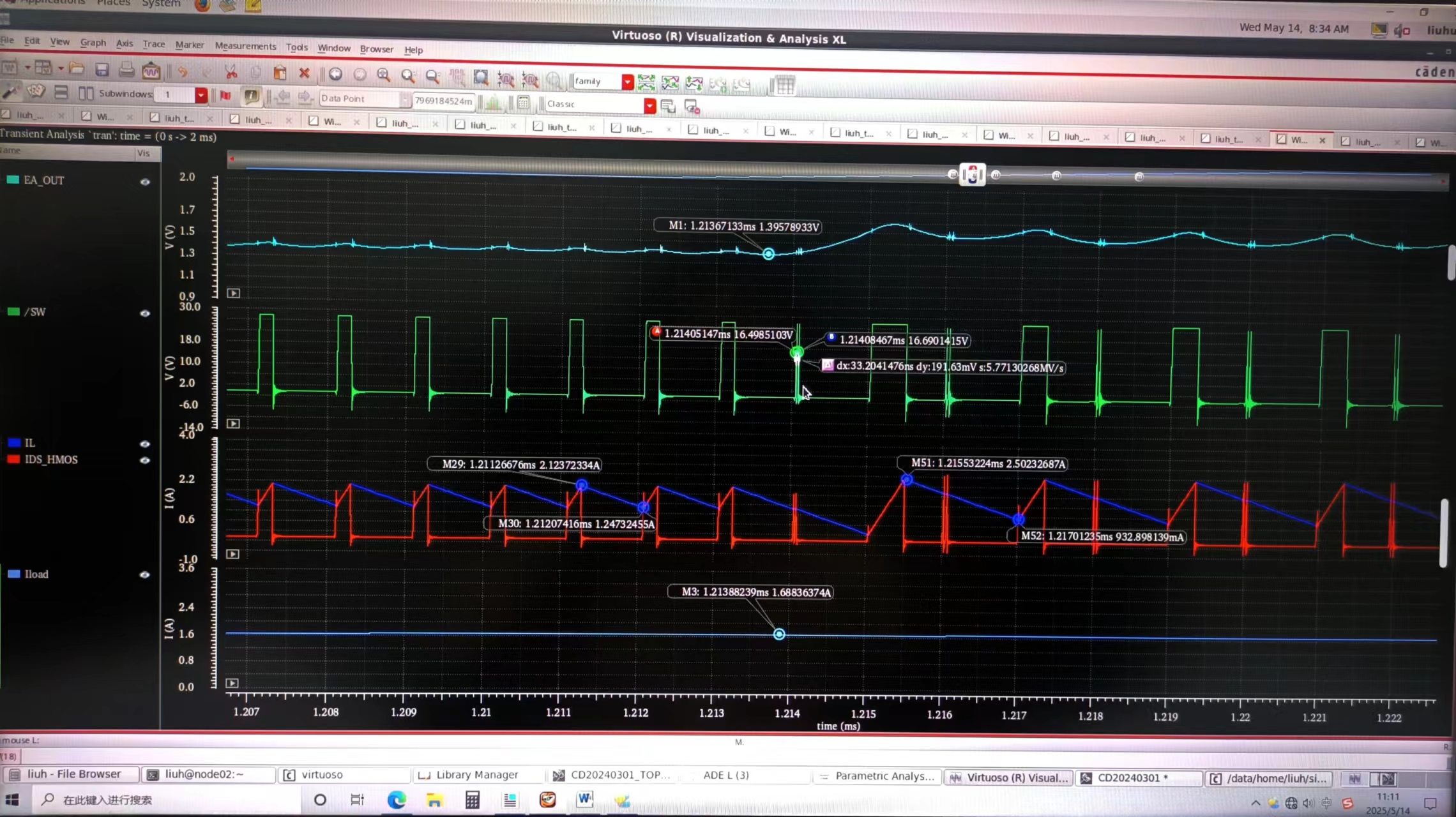

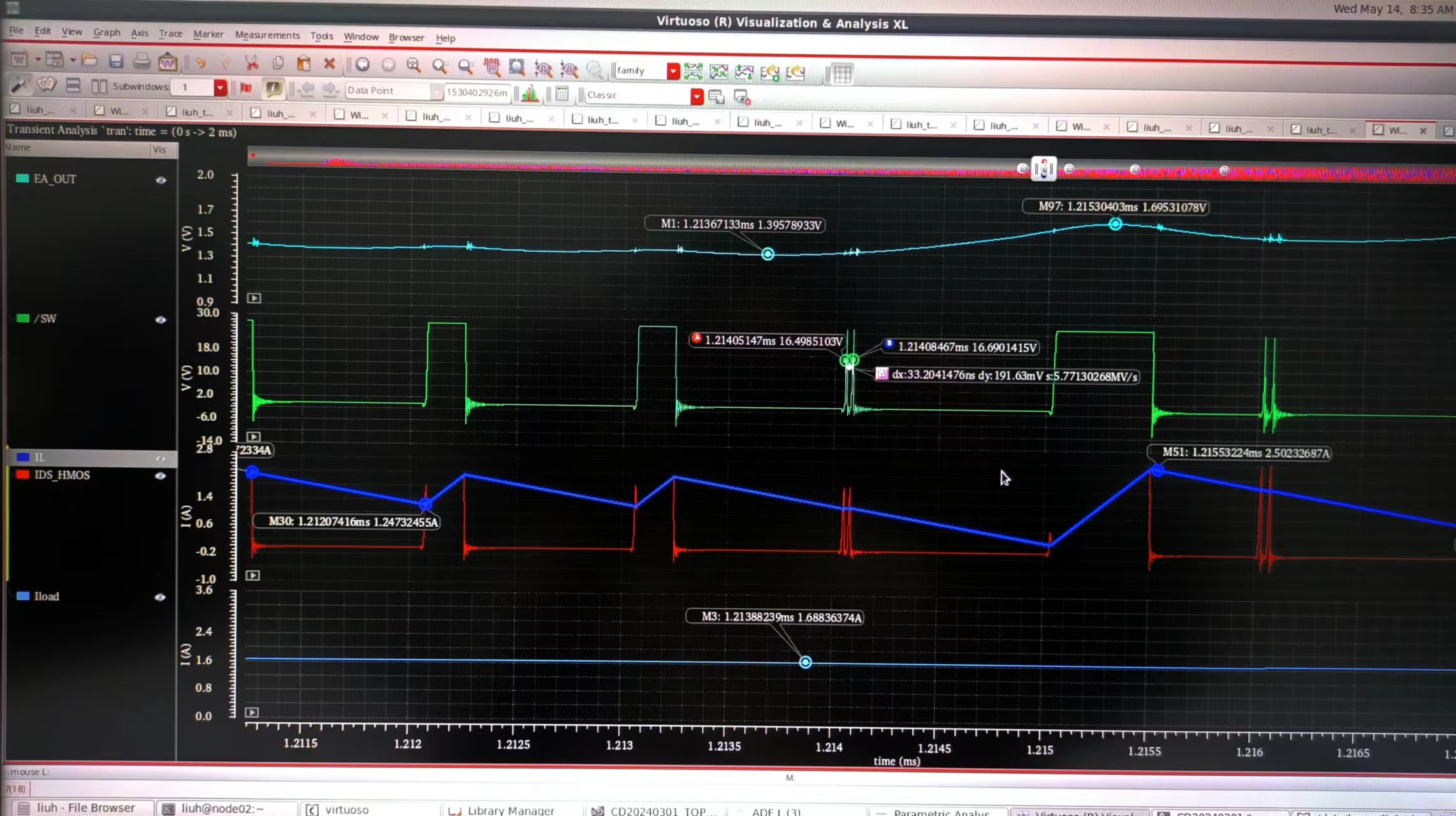

当Iload>1.68A时,SW信号突然出现了两个极短时间的脉冲波形,导致在该周期内占空比非常小,系统为了保持输出电压,不得不在第二个周期增大了占空比来保持整体的占空比不变。系统也因为第一个周期占空比太小,几乎整个周期都处于续流阶段,导致电感电流的纹波非常大。如此循环,形成了一个诡异的平衡。如图2、图3为图1的局部放大。输出电压虽然没有因此下降,但频率减半,纹波增大。

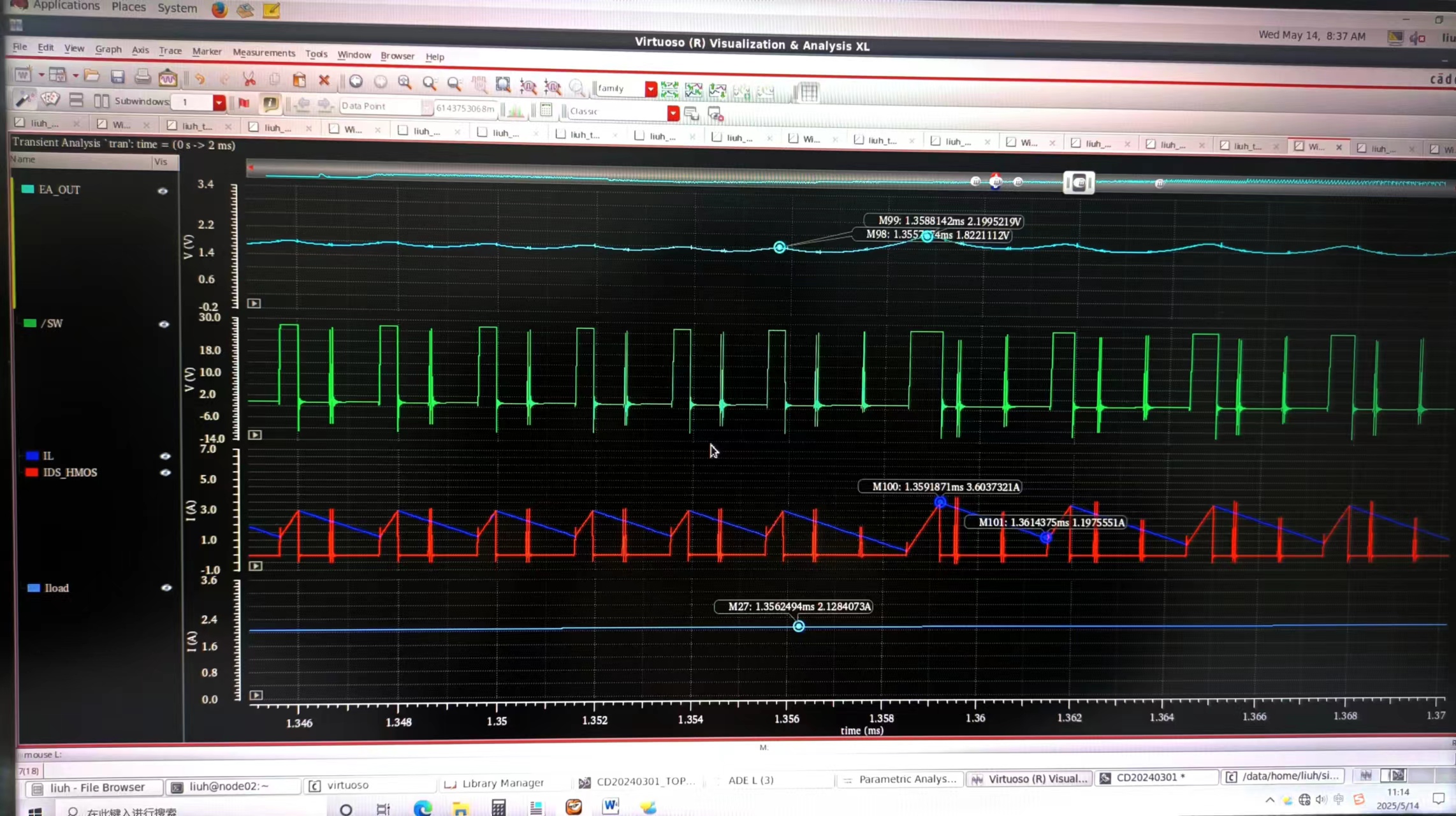

当Iload>2.12A时,SW信号出现连续两个周期上功率MOS管导通极短的情况,如图4,相应的频率进一步减小,纹波进一步增大。

当Iload>2.56A时,SW信号出现连续三个周期上功率MOS管导通极短的情况,如图5。

再继续增加电流到2.9A左右,系统输出就无法保持5V输出了。

当不同输入电压时,增大负载电流Iload,均会出现以上现象,但总体随着输入电压下降有所好转。如表1

| VIN | VOUT | 正常 | 一次降频(异常) | 二次降频(异常) | 三次降频(异常) | VOUT骤降(崩盘) |

| 6 | 5 | Iload<2.4A | 2.4<Iload<2.9A | × | × | Iload>2.9A |

| 12 | 5 | Iload<2.0A | 2.0<Iload<2.22A | × | × | Iload>2.22A |

| 18 | 5 | Iload<1.8A | 1.8<Iload<2.1A | 2.1<Iload<2.4A | × | Iload>2.4A |

| 24 | 5 | Iload<1.7A | 1.7<Iload<2.0A | 2.0<Iload<2.3A | 2.3<Iload<2.6A | Iload>2.6A |

| 28 | 5 | Iload<1.65A | 1.65<Iload<2.12A | 2.12<Iload<2.56A | 2.56<Iload<2.9A | Iload>2.5A |

表1

图1

图2

图3

图4

图5

问题:

1、为什么上功率MOS管会突然出现了两个极短导通时间的现象?我明明做了40nS最小导通时间的。

2、怎么解决这个问题呢?

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?