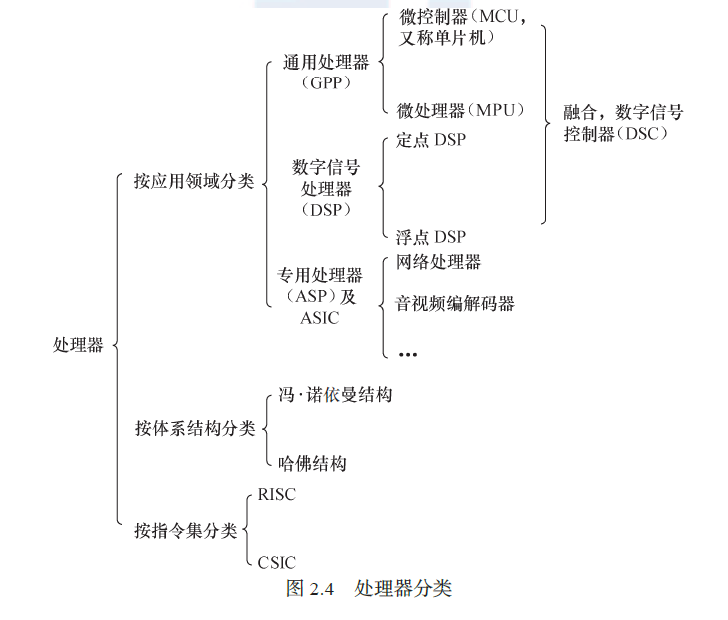

2.1 处理器

2.1.1 通用处理器——ARM

主流的通用处理器(GPP)多采用SoC(片上系统)的芯片设计方法,集成了各种功能模块,每一种功能都是有硬件描述语言设计程序,然后在SoC内由电流实现的。

中央处理器的体系结构可以分为两类:

1.冯诺依曼结构。

程序指令存储器和数据存储器合并在一起的存储器结构。程序指令存储地址和数据存储地址指向同一存储器的不同物理位置,因此程序指令和数据的宽度相同。

2.哈弗结构。

程序指令和数据分开存储,质量和数据可以有不同的数据宽度。此外,哈弗结构还采用了独立的程序总线和数据总线,分别作为CPU和每个存储器之间的专用通信路径,具有较高的执行效率。

3.改进的哈弗结构

两条总线有程序存储器和数据存储器分时共用。使用用共用数据总线来完成程序存储模块或数据存储模块与CPU之间的数据传输,共用地址总线来寻址程序和数据。

指令集角度来分,中央处理器有两类:

1. RISC——精简指令集计算机

尽量减少指令集、指令单周期执行,但是目标代码会更大。

2. CISC——复杂指令集计算机

增强指令的能力,减少目标代码的数量,但是指令复杂,指令周期长。

2.1.2 数字信号处理器——DSP

针对通信、图像、语音和视频处理等领域的算法而设计的。

分类:

1. 定点DSP

定点运算模拟浮点运算

2. 浮点DSP

硬件实现浮点运算,单周期完成。浮点运算处理程序高于定点DSP。

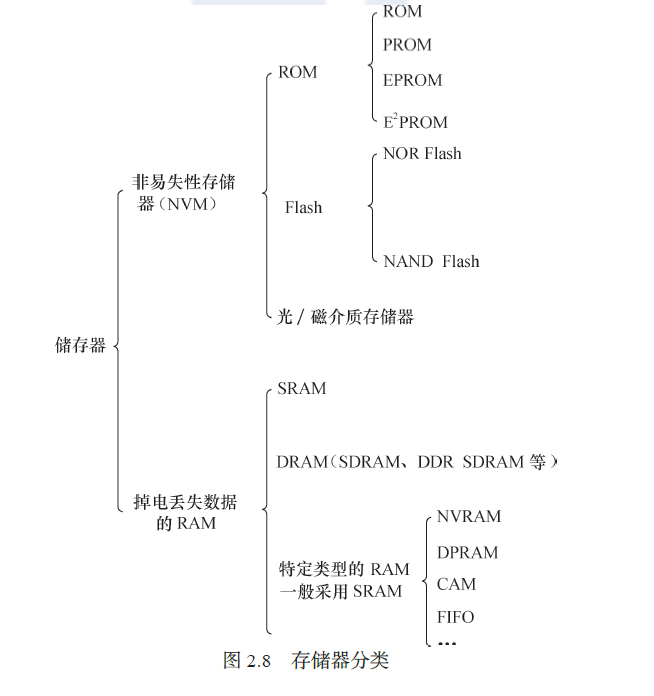

2.2 存储器

分类:

只读存储器(ROM)、闪存(Flash)、随机存取存储器(RAM)、光/磁介质存储器。

ROM:

ROM、可编程ROM(PROM)、可擦除可编程ROM(EPROM)和电可擦除可编程ROM(EEPROM)。

Flash:

NOR(或非)、NAND(与非)

NOR Flash和CPU的结构属于典型的类SRAM接口,不需要额外的控制电流。特点是可芯片内执行(eXecute In Place, XIP),程序可以在NOR内直接运行。

NAND Flash 和CPU的接口必须由相应的控制电路进行转换,也可以通过地址线或GPIO产生NAND Flash接口的信号。NAND Flash以块方式进行访问,不支持芯片内执行。

Flash的编程原理都是只能将1写成0,而不能将0写成1.因此在Flash编程之前,必须将对应的块擦除,擦除的过程就是把所有位写成1的过程。块内的所有字节变为0xFF。

RAM:

静态RAM(SRAM)、动态RAM(DRAM)。

2.3 接口与总线

2.3.1 串口

RS-232 、RS-422、RS-485都是串行数据接口标准。

2.3.2 iic

I2C(内置集成电路)总线是由Philips 公司开发的两线式串行总线

2.3.3 spi

SPI(Serial Peripheral Interface,串行外设接口)总线系统是一种同步串行外设接口,它可以使CPU 与各种外围设备以串行方式进行通信以交换信息。

2.3.4 usb

USB(通用串行总线)是Intel、Microsoft 等厂商为解决计算机外设种类的日益增加与有限的主板插槽和端口之间的矛盾而于1995 年提出的,它具有数据传输率高、易扩展、支持即插即用和热插拔的优点,目前已得到广泛应用。

2.3.5 以太网接口

以太网接口由MAC(以太网媒体接入控制器)和PHY(物理接口收发器)组成。MAC 和PHY 之间采用MII(媒体独立接口)连接。

2.3.6 pci和pci-e

PCI(外围部件互连)是由Intel 于1991 年推出的一种局部总线,作为一种通用的总线接口标准,它在目前的计算机系统中得到了非常广泛应用。

2.3.7 sd和sdio

SD(Secure Digital)是一种关于Flash 存储卡的标准,也就是一般常见的SD 记忆卡,在设计上与MMC(Multi-Media Card)保持了兼容。SDHC(SD High Capacity)是大容量SD 卡,支持的最大容量为32GB。2009 年发布的SDXC(SD eXtended Capacity)则支持最大2TB 大

小的容量。

SDIO(Secure Digital Input and Output Card,安全数字输入输出卡)在SD 标准的基础上,定义了除存储卡以外的外设接口。

eMMC(Embedded Multi Media Card)是当前移动设备本地存储的主流解决方案,目的在于简化手机存储器的设计。eMMC 就是NAND Flash、闪存控制芯片和标准接口封装的集合,

它把NAND 和控制芯片直接封装在一起成为一个多芯片封装(Multi-Chip Package,MCP)芯片。

2.4 CPLD和FPGA

CPLD(复杂可编程逻辑器件)由完全可编程的与或门阵列以及宏单元构成。

对于驱动工程师而言,我们只需要这样看待CPLD 和FPGA :如果它完成的是特定的接口和控制功能,我们就直接把它当成由很多逻辑门(与、非、或、D 触发器)组成的可完成

一系列时序逻辑和组合逻辑的ASIC ;如果它完成的是CPU 的功能,我们就直接把它当成CPU。

2.5 原理图分析

2.6硬件时序分析

2.7 芯片手册的阅读方法

2.8仪器仪表的使用

万用表、示波器、逻辑分析仪

6244

6244

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?