将陆续上传本人写的新书《自己动手写处理器》(尚未出版),今天是第七篇,我尽量每周四篇

2.6 Verilog HDL行为语句

2.6.1 过程语句

Verilog定义的模块一般包括有过程语句,过程语句有两种:initial、always。其中initial常用于仿真中的初始化,其中的语句只执行一次,而always中语句则是不断重复执行的。此外,always过程语句是可综合的,initial过程语句是不可综合的。

1、always过程语句

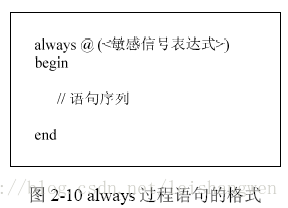

always过程语句的格式如图2-10所示。

always过程语句通常是带有触发条件的,触发条件写在敏感信号表达式中,敏感信号表达式又称为事件表达式或敏感信号列表,当该表达式中变量的值改变时,就会引发其中语句序列的执行。因此,敏感信号表达式中应列出影响块内取值的所有信号。

(1)敏感信号表达式的格式

如果有两个或两个以上的敏感信号时,它们之间使用“or”连接,此处还是以32位加法器为例,2.4节是使用assign直接赋值的,其实也可以使用always过程语句实现,如下。只要被加数in1、加数in2中的任何一个改变,都会触发always过程语句,在其中进行加法运算。这里有两个敏感信号in1、in2,使用“or”连接。

module add32(input wire[31:0] in1,

input wire[31:0] in2,

output reg[31:0] out);

always @ (in1 or in2) //使用always过程语句实现加法

begin

out = in1 + in2;

end

endmodule

敏感信号列表中的多个信号也可以使用逗号隔开,上面的32位加法器可以修改为如下形式。

module add32(input wire[31:0] in1,

input wire[31:0] in2,

output reg[31:0] out);

always @ (in1, in2) //多个敏感信号使用逗号分隔

begin

out = in1 + in2;

end

endmodule

敏感信号列表也可以使用通配符“*”,表示在该过程语句中的所有输入信号变量,上面的32位加法器可以修改为如下形式。

module add32(input wire[31:0] in1,

input wire[31:0] in2,

output reg[31:0] out);

always @ (*) //使用通配符表示过程语句中的所有输入信号变量

begin

out = in1 + in2;

end

endmodule

(2)组合电路与时序电路

敏感信号可以分为两种类型:一种为电平敏感型,一种为边沿敏感型。前一种一般对应组合电路,如上面给出的加法器的例子,后一种一般对应时序电路。对于时序电路,敏感信号通常是时钟信号,Verilog HDL提供了posedge、negedge两个关键字来描述时钟信号。posedge表示以时钟信号的上升沿作为触发条件,negedge表示以时钟信号的下降沿作为触发条件。还是以32位加法器为例,可以为其添加一个时钟同步信号,如下。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?