最近要用到W5500,终于有机会使用SPI模块了,把相关资料看了遍,各种速成教程还是没有数据手册靠谱。于是直接翻译一遍。

SPI模块的硬件驱动部分已经写好。http://blog.csdn.net/lin_strong/article/details/79361503

如果翻译中发现了什么问题欢迎联系我指正。

第21章 串行外设接口(S12SPIV5)

译者注:译者博客(http://blog.csdn.net/lin_strong),转载请保留这条。此为 MC9S12XEP100RMV1芯片手册的第21章内容,仅供学习交流使用,请勿用于商业用途。

介绍

SPI模块实现了MCU与外设设备间的双工同步串行通信。软件可以通过轮询标志位或者异步中断通知的方式来与SPI模块交互。

术语缩写

| 缩写 | 全称(英) | 全称(中) |

|---|---|---|

| SPI | Serial Peripheral Interface | 串行外设接口 |

| Slave Select | 从机选定 |

| SCK | Serial Clock | 串行时钟 |

| MOSI | Master Output, Slave Input | 主(机)(输)出从(机)(输)入 |

| MISO | Master Input, Slave Output | 主入从出 |

| MOMI | Master Output, Master Input | 主入主出 |

| SISO | Slave Input, Slave Output | 从入从出 |

特性

SPI模块包含以下特性:

- 可以设置为主节点或从节点

- 可选传输数据宽度为8或16位

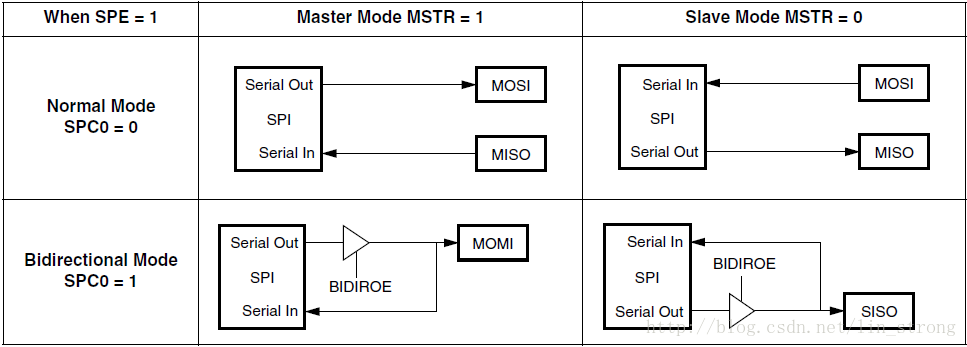

- 单线双向(Bidirectional,译者注:直译为“双向”,但意思上看应该是指单线双向,因为SPI本身就是双向的,所以后面译为“单线双向”)模式

- 从机选定信号输出

- 带有中断功能的模式故障错误标志位

- 双缓冲数据寄存器

- 可通过编程更改极性和相位的串行时钟

- 控制SPI在等待模式下运作

运行模式

SPI模块可以在三种模式下运行:run、wait和stop。

- Run模式

这是基本的运行模式 - Wait模式

在wait模式中运行的SPI是一个可配置的低能耗模式,由SPICR2寄存器内的SPISWAI位控制。在wait模式下,如果SPISWAI位为0,SPI就会如在run模式下一样运行。如果SPISWAI位为1,SPI会进入低能耗状态,SPI时钟生成会被关闭。如果SPI被配置为主机,任何进行中的传输都会停止,但是会在CPU进入run模式后恢复。如果SPI被配置为从机,数据的接收和传输会继续,这样从机就能与主机保持同步。 - Stop模式

为了节能,SPI在stop模式下是不活跃的。如果SPI被配置为主机,任何进行中的传输都会停止,但是会在CPU进入run模式后恢复。如果SPI被配置为从机,数据的接收和传输会继续,这样从机就能与主机保持同步。

想了解细节的话,请参阅4.7“低能耗模式选项”。

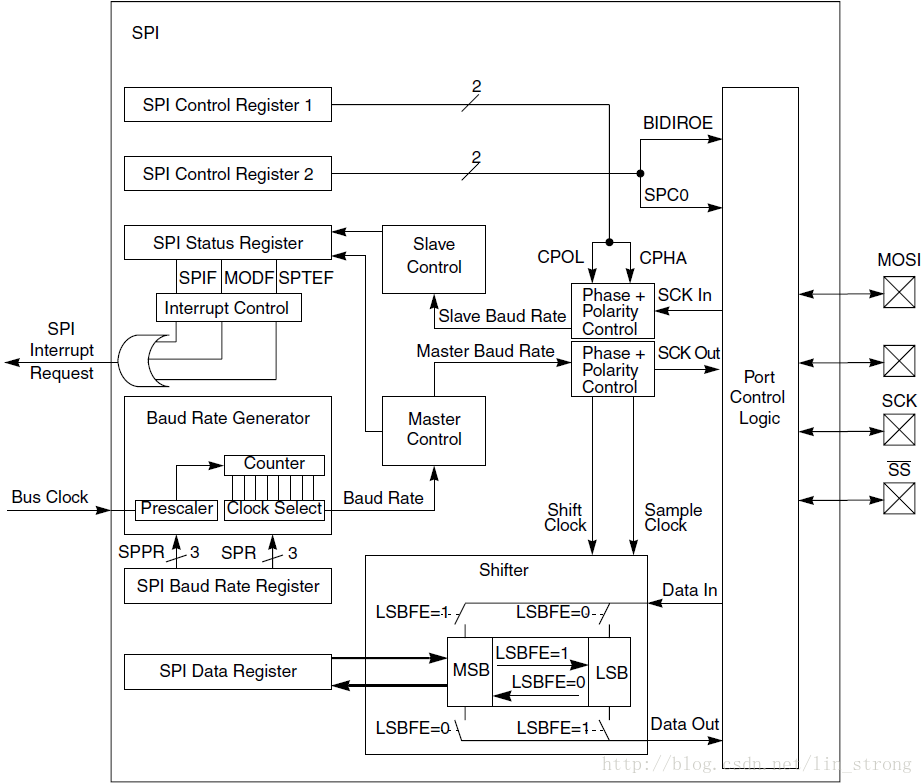

框图

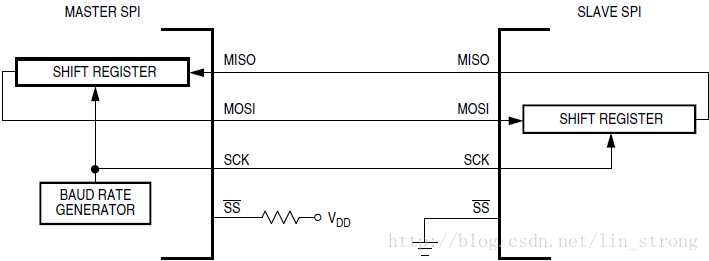

下图给出了SPI架构的综览。SPI模块主要由状态、控制和数据寄存器、移位逻辑、波特率生成器、主/从控制逻辑和端口控制逻辑构成。

图 1.SPI框图

引脚描述

这个部分列出了所有可能会与外部芯片连接的端口。SPI模块总共有4个外部引脚。

MOSI — 主出/从入引脚

当配置为主机时,这个引脚用于把数据传出SPI模块;当配置为从机时,用于接收数据。

MISO — 主入/从出引脚

当配置为从机时,这个引脚用于把数据传出SPI模块;当配置为主机时,用于接收数据。

— 从机选定引脚

— 从机选定引脚

当配置为主机时,这个引脚用于从SPI模块输出选定信号到要接收数据的外设;当配置为从机时,用于接收从机选定信号。

SCK — 串行时钟引脚

在主机模式下,这是同步时钟输出引脚;在从机模式下,这是同步时钟接收引脚。

内存映射与寄存器定义

这个部分提供了SPI模块的地址空间与寄存器的细节描述。

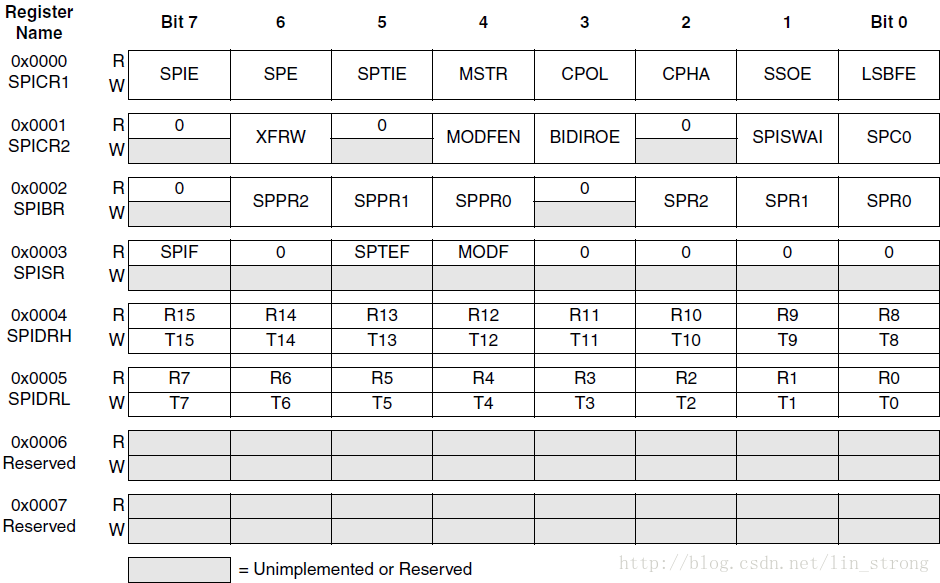

模块内存映射

图2给出了SPI模块的内存映射。每个寄存器前列出的地址指的是偏移量。基地址定义在SoC等级,地址偏移定义在模块等级。读保留位会返回0,写保留位没有任何用处。

图 2.SPI寄存器总结

寄存器描述

这个部分按照地址顺序描述了每个寄存器。每个描述都包含带有相关数字的标准寄存器图。然后紧跟着寄存器位和字段功能的描述,按照位顺序。

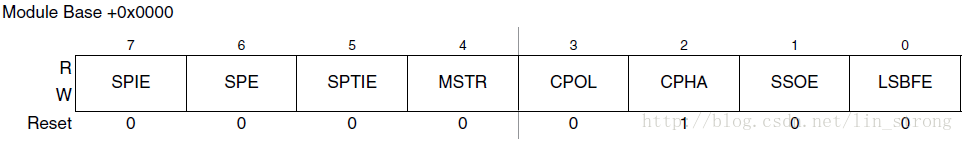

SPI控制寄存器1(SPICR1)

图 3. SPI控制寄存器1

读:随时

写:随时

表 2. SPICR1字段描述

| 字段 | 描述 |

|---|---|

| 7 SPIE | SPI 中断使能位 — 如果SPIF或者MODF状态标志位被置位,这个位会使能SPI中断请求。 0 禁用SPI中断。 1 使能SPI中断 |

| 6 SPE | SPI 系统使能位 — 这个位会使能SPI系统并把SPI端口引脚赋予SPI系统使用。如果SPE被清零,SPI就会被禁用并强制进入空闲状态,SPISR寄存器内的状态位会被重置。 0 禁用SPI(低能耗)。 1 使能SPI,端口引脚赋予SPI模块使用。 |

| 5 SPTIE | SPI 传输中断使能 — 如果SPTEF标志位被置位,这个位会使能SPI中断请求。 0 禁用SPTEF中断。 1 使能SPTEF中断 |

| 4 MSTR | SPI 主/从模式选择位 — 这个位用于选择SPI是主机还是从机。将SPI从主机切换为从机或反之会强迫SPI系统进入空闲状态。 0 SPI从机模式。 1 SPI主机模式 |

| 3 CPOL | SPI 时钟极性位 — 这个位用于选择SPI时钟是否反相。想要在SPI模块间传输数据的话,SPI模块必须使用相同的CPOL值。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 0 使用高有效时钟。在空闲状态下SCK是低电平。 1 使用低有效时钟。在空闲状态下SCK是高电平。 |

| 2 CPHA | SPI 时钟相位位 — 这个位用于选择SPI时钟格式。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 0 在奇数边沿进行数据采样。 1 在偶数边沿进行数据采样。 |

| 1 SSOE | 从机选定输出信号使能 — SS输出特性与这个位以及MODFEN位有关,详见表3。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 |

| 0 LSBFE | 使能LSB-First — 这个位不影响数据寄存器内的字节序。读写数据寄存器时总是在最高bit放MSB。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 0 最高有效位优先传输。 1 最低有效位优先传输。 |

表3.

| MODFEN | SSOE | 主机模式 | 从机模式 |

|---|---|---|---|

| 0 | 0 |  不被SPI使用 不被SPI使用 |  为输入 为输入 |

| 0 | 1 |  不被SPI使用 不被SPI使用 |  为输入 为输入 |

| 1 | 0 | 有MODF特性的 输入 输入 |  为输入 为输入 |

| 1 | 1 |  是从机选择输出 是从机选择输出 |  为输入 为输入 |

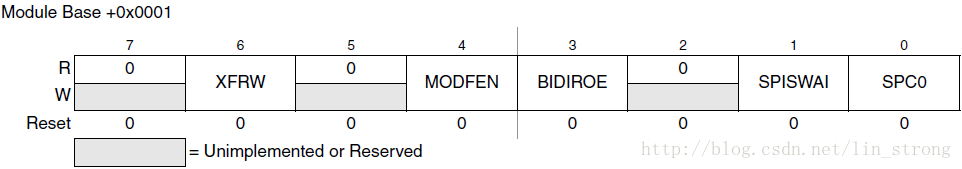

SPI控制寄存器2(SPICR2)

图 4.SPI控制寄存器2(SPICR2)

读:随时

写:随时;写保留的位没有任何用。

表 4. SPICR2 字段描述

| 字段 | 描述 |

|---|---|

| 6 XFRW | 传输宽度 — 这个位用于选择传输数据的宽度。如果选择了8位传输宽度,SPIDRL就是专门的数据寄存器,SPIDRH无用。如果选择了16位传输宽度,SPIDRH和SPIDRL就形成了一个16位数据寄存器。参阅3.2.4 “SPI状态寄存器(SPISR)”了解更多关于传输/接收数据处理以及中断标志位清零机制的信息。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 0 8位传输数据宽度(n=8)1。 1 16位传输数据宽度(n=16)1。 |

| 4 MODFEN | 模式故障使能位 — 这个位会使能MODF故障探测。如果SPI处于主机模式并且MODFEN被清零了,那么 引脚就不受SPI模块控制。在从机模式下,不管MODFEN的值是什么, 引脚就不受SPI模块控制。在从机模式下,不管MODFEN的值是什么, 都是输入引脚。参阅表3获得MODFEN对 都是输入引脚。参阅表3获得MODFEN对 的作用的综述。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 的作用的综述。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 0  端口引脚不被SPI模块使用。 端口引脚不被SPI模块使用。1 带MODF特性的  端口引脚。 端口引脚。 |

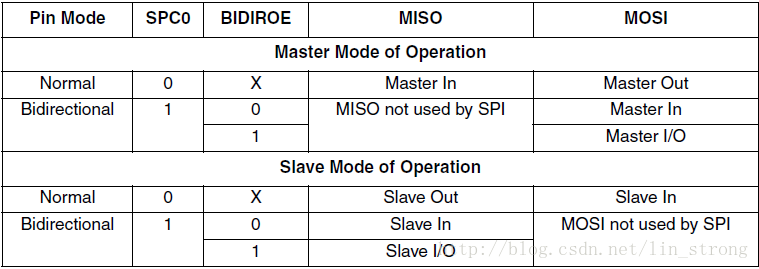

| 3 BIDIROE | 单线双向模式下输出使能 — 在单线双向运行模式下(SPC0=1),这个位用于控制MOSI和MISO输出缓存。在主机模式下,这个位控制MOSI端口的输出缓存,在从机模式下,它控制MISO端口的输出缓存。在主机模式下,SPC0从0变为1会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 0 禁用输出缓存。 1 使能输出缓存。 |

| 1 SPISWAI | Wait模式下SPI模块停止 — 这个位用于在wait模式下节能 0 SPI时钟在wait模式下正常运行。 1 在wait模式下停止SPI时钟生成。 |

| 0 SPC0 | 串行引脚控制位0 — 这个位用于使能单线双向引脚配置,详见表5。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 |

1. n在后面用作选择的传输宽度的占位符

表 5. 单线双向引脚配置

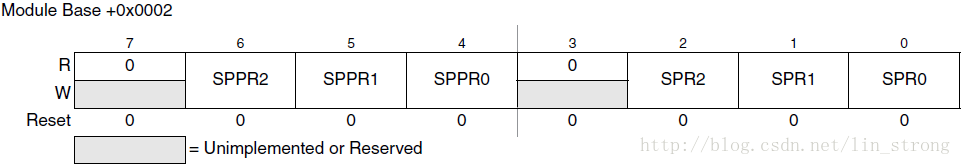

SPI波特率寄存器(SPIBR)

图 5.SPI波特率寄存器(SPIBR)

读:随时

写:随时;写入保留的位没有任何作用。

表 6.SPIBR字段描述

| 字段 | 描述 |

|---|---|

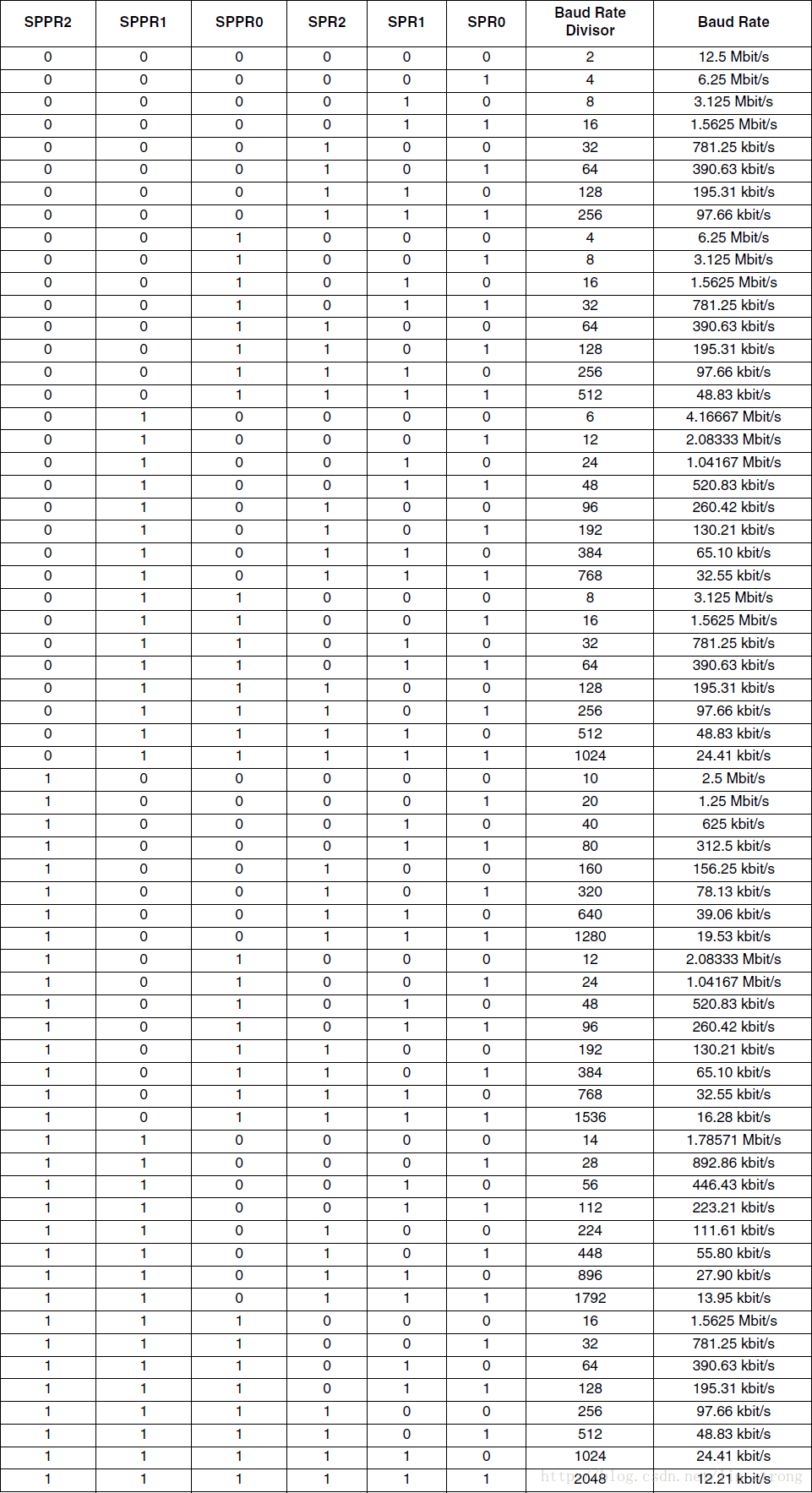

| 6-4 SPPR[2:0] | SPI波特率预选位 — 这几位如表7中那样决定了SPI波特率。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 |

| 2-0 SPR[2:0] | SPI波特率选择位 — 这几位如表7中那样决定了SPI波特率。在主机模式下,改变这个位会导致进行中的传输被抛弃并强制SPI系统进入空闲状态。 |

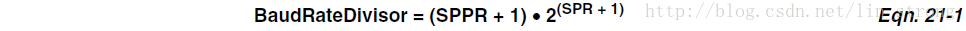

波特率分频系数表达式如下:

然后如下计算出波特率:

-

注意:

- 请查阅这个数据手册的电气章节的SPI电气规范来了解允许的最小波特率。

表 7.SPI波特率选择示例(25MHz总线时钟)

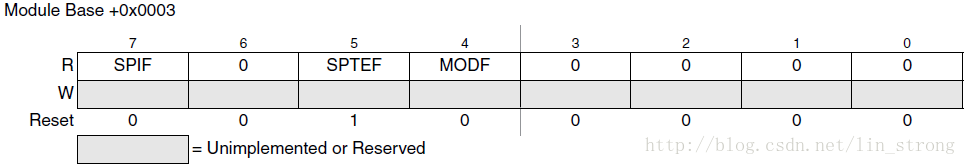

SPI状态寄存器(SPISR)

图 6.SPI状态寄存器(SPISR)

读:随时

写:没有作用

表 8.SPISR字段描述

| 字段 | 描述 |

|---|---|

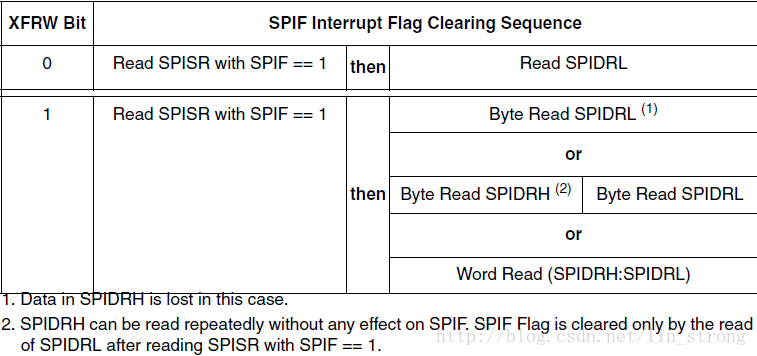

| 7 SPIF | SPIF 中断标志位 — 在数据被传输入SPI数据寄存器后这个位被置位。参阅表9了解如何清零SPIF标志位。 0 传输未完成。 1 新数据已被拷贝进SPIDR。 |

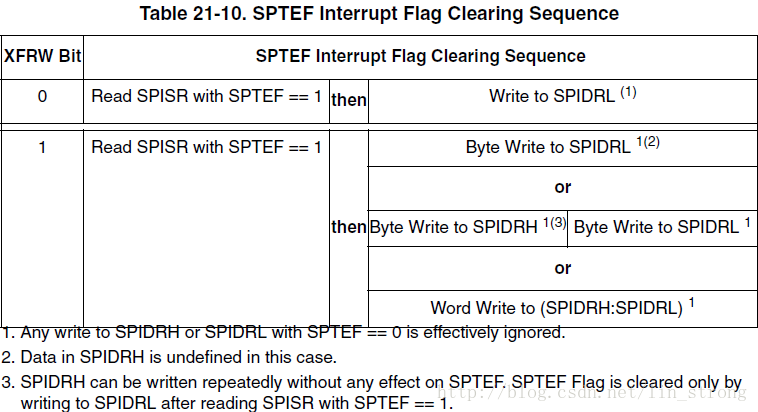

| 5 SPTEF | SPI发送器空中断标志位 — 如果被置位,说明数据发送寄存器已经空了。参阅表9了解如何清零这个位并放置数据进数据发送寄存器。 0 SPI数据寄存器非空。 1 SPI数据寄存器空。 |

| 4 MODF | 模式故障标志位 — 当SPI被配置为主机并且SPICR2寄存器的MODFEN位被置位即启用了模式故障探测后,如果探测到SS引脚被拉低,这个位被置位。详情请参阅3.2.2 “SPI控制寄存器2(SPICR2)”的MODFEN位描述。通过(当MODF=1时)读取一次SPI状态寄存器然后写入SPI控制寄存器1,这个标志位就会自动清零。 0 没有发生模式故障。 1 发生了模式故障。 |

表 9.SPIF中断标志位清零序列

表 10.SPTEF中断标志位清零序列

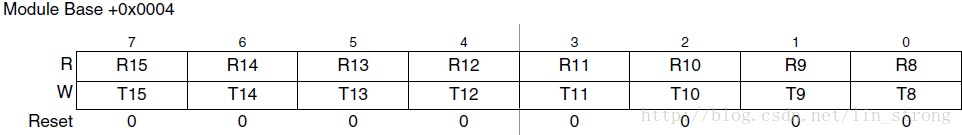

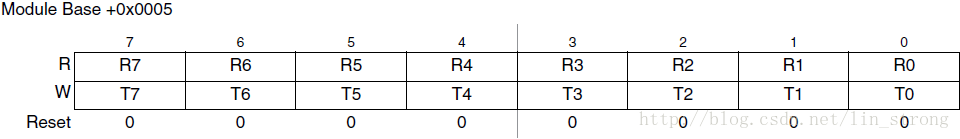

SPI数据寄存器(SPIDR = SPIDRH:SPIDRL)

图 7.SPI高位数据寄存器

图 8.SPI低位数据寄存器

读:随时;只有在SPIF被置位时读的数据才有效

写:随时

SPI数据寄存器同时作为SPI数据的输入和输出寄存器。写入这个寄存器会让数据按序传输。对于配置为主机的SPI,数据序列会在前一个传输完成后立刻开始传输。SPI发送器将SPISR寄存器内的SPTEF标志位清零说明SPI数据寄存器已经准备好接受新数据了。当SPIF被置位了,说明SPIDR里接收的数据有效。

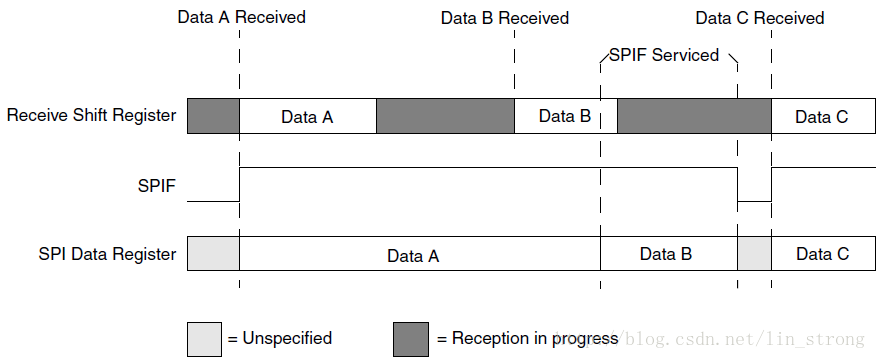

如果SPIF为0并且收到了数据,收到的数据就会从接受移位寄存器传输到SPIDR中,然后置位SPIF。

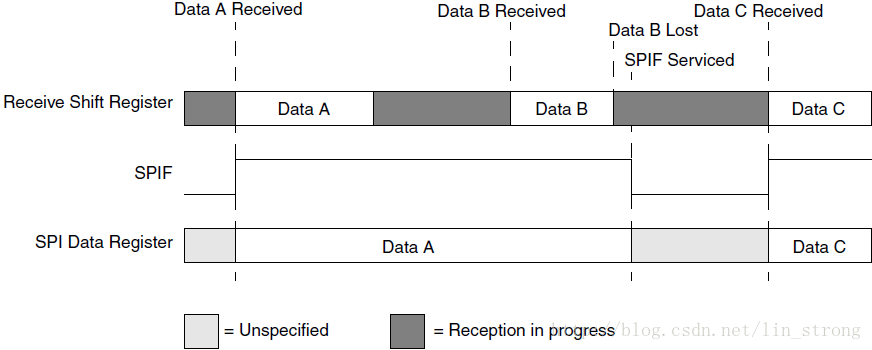

如果SPIF为1时收到了第二个数据值,新收到的数据会作为有效值先存在接收移位寄存器内直到开始下一次传输。SPIDR内的数据不会变化。

如果SPIF为1,新数据还在接收移位寄存器内,而在第三次传输开始之前取出了数据,则接收移位寄存器内的数据就会传输进SPIDR中,SPIF会保留置位(见图9)。

如果SPIF为1,新数据还在接收移位寄存器内,而在第三次传输之后才取出数据,则接收移位寄存器内的数据已经无效了,不会被传入SPIDR中(见图10)。

图 9.及时取出数据的情况

图 10.未及时取出数据的情况

功能描述

SPI模块实现了MCU与外设设备间的双工同步串行通信。软件可以通过轮询标志位或者异步中断通知的方式来与SPI模块交互。

通过置位SPI控制寄存器1中的SPI使能位(SPE)来使能SPI系统。当SPE被置位了,四个相关引脚就赋予SPI功能来使用了:

- 从机选定(

)

- 串行时钟(SCK)

- 主出/从入(MOSI)

- 主入/从出(MISO)

SPI系统的核心是SPI数据寄存器。主机以及从机中的n位数据寄存器通过MOSI和MISO引脚链接起来形成了一个分布式2n位寄存器。当执行了一个数据传输操作,这个2n位寄存器根据主机的S时钟串行地移位n位,这样数据就在主机和从机间进行了交换。写入主机SPI数据寄存器的数据会输出到从机,而从主机SPI数据寄存器中读出的数据是来自从机的。

当SPTEF=1时读取SPISR然后写入SPIDR就把数据放入了数据发送寄存器。当传输完成并且SPIF为0时,收到的数据会移入数据接收寄存器。这个数据寄存器在读取的时候表现为SPI数据接收寄存器而在写入时表现为SPI数据发送寄存器。读数据缓存与写数据发送寄存器使用共享的SPI数据寄存器地址。

SPI控制寄存器1(SPICR1)中的时钟相位控制位(CPHA)和时钟极性控制位(CPOL)指定SPI系统使用四种可能的格式中的哪一个。CPOL位简单地指定时钟是否反相。CPHA位则通过指定在奇数SCK边沿还是偶数SCK边沿采样来适应两种不同的基础协议(见4.3“传输格式”)。

可以配置SPI为主机或者从机。当SPI控制寄存器1中的MSTR位被置位,就选择了主机模式,否则为从机模式。

-

注意:

- 当接收移位寄存器内存在挂起的字节时,如果改变CPOL或者MSTR位会导致挂起的字节丢失,要避免这种情况发生。

主机模式

当MSTR位被置位,则SPI运行在主机模式。只有一个主机SPI模块可以发起传输。传输是由写入主SPI数据寄存器开始的。如果移位寄存器空了,数据就会立刻传输到移位寄存器。数据会在串行时钟的控制下从MOSI引脚移位输出。

- 串行时钟

SPI波特率寄存器中的SPR2、SPR1和SPR0波特率选择位联合SPPR2、SPPR1和SPPR0波特率预选位一起控制着波特率生成器并决定传输的速率。SCK引脚是SPI的时钟输出。通过SCK引脚,主机的波特率生成器控制着从机外设的移位寄存器。 - MOSI、MISO引脚

在主机模式下,串行数据数据输出引脚(MOSI)和串行数据输入引脚(MISO)的功能是由SPC0和BIDIROE控制位决定的。 引脚

如果MODFEN和SSOE被置位了,引脚就被配置为从机选定输出。

输出信号会在每次传输期间变低而在空闲状态下变高。

如果MODFEN被置位而SSOE为0,引脚就被配置为输入以探测模式故障错误。如果

输入信号被拉低,说明发生了模式故障,有另一个主机试图驱动MOSI和SCK线。这种情况下,SPI会通过清零MSTR位并禁用从机输出缓存MISO(或在单向双向模式下的SISO)立刻切换到从机模式。所以最后所有的输出都被禁用,SCK、MOSI和MISO变为了输入。如果在传输过程中发生了模式故障时,传输就会被抛弃,SPI被强制进入空闲状态。

这次模式故障错误还会置位SPI状态寄存器(SPISR)中的模式故障标志位(MODF)。如果当MODF标志位被置位时SPI中断使能位(SPIE)为1,那么就会发出SPI中断序列请求。

当主机模式下写入了SPI数据寄存器,会有半个SCK周期的延迟。延迟之后主机内的SCK就启动了。剩下的传输过程有轻微的不同,取决于SPI控制寄存器内的SPI时钟相位位CPHA确定的时钟格式(见4.3“传输格式”)。

-

注意:

- 在主机模式下改变CPOL、CPHA、SSOE、LSBFE、XFRW、MODFEN、SPC0、BIDIROE(当SPC0=1)、SPPR2-SPPR0 和 SPR2-SPR0位会导致进行中的传输被抛弃并强迫SPI进入空闲状态。异地的从机无法探测到这个状况,因此主机必须确保异地从机回到空闲状态。

从机模式

当SPI控制寄存器内的MSTR位为0时,SPI就运行在从机模式下。

- 串行时钟

在从机模式下,SCK是来自主机的SPI时钟输入。 - MISO、MOSI引脚

在从机模式下,串行数据数据输出引脚(MISO)和串行数据输入引脚(MOSI)的功能是由SPI控制寄存器2中的SPC0和BIDIROE控制位决定的。 引脚

引脚是从机选定输入。在数据传输开始前,从机SPI的

引脚必须为低电平而且要一直保持到传输完成。如果

变为高电平,SPI就强制进入空闲状态。

输入信号还控制着串行数据输出引脚,如果

为高电平(未被选择),串行数据输出引脚就是高阻抗的,反之,由SPI数据寄存器的第一个位来驱动串行数据输出引脚。同样的,如果从机未被选择(

为高电平),那SCK输入信号就会被忽略,SPI移位寄存器内不会发生内部移位。

SPI也有单线双向的功能,一些SPI外设只能够以从机模式接收SPI数据。对于这些简单的设备,没有串行数据输出引脚。

-

注意:

- 当使用了有单线双向功能的外设,注意不要同时启用两个串行输出驱动同一系统从属的串行数据输出线的接收器。

只要不超过一个从机设备驱动系统从机的串行数据输出线,就可以使多个从机同时收到相同的主机的传输来的数据,尽管主机不会收到所有从机的返回信息。

如果SPI控制寄存器1中的CPHA位为0,SCK上的奇数次边沿会导致串行数据输入引脚上的数据被锁存。偶数次边沿导致之前从串行数据输入引脚上锁存的数据在SPI移位寄存器内进行移位,移位方向取决于LSBFE位。

如果CPHA位为1,SCK上的偶数次边沿会导致串行数据输入引脚上的数据被锁存。奇数次边沿导致之前从串行数据输入引脚上锁存的数据在SPI移位寄存器内进行移位,移位方向取决于LSBFE位。

当CPHA位为1,第一个边沿被用于把第一个数据位输出到串行数据输出引脚。当CPHA为0并且

-

注意:

- 在从机模式下改变CPOL、CPHA、SSOE、LSBFE、MODFEN、SPC0、BIDIROE(当SPC0=1)会导致进行中的传输失败,必须避免。

传输格式

在SPI传输期间,数据是被同时传送(串行移位出)和接收(串行移位进)的。串行时钟(SCK)驱动两条串行数据线上的信息的移位和采样的同步。从机选定线允许选择单个从机SPI设备;未被选定的从机设备会忽略SPI总线活动。你可以选择使用从机选定线来实现多主机总线争夺机制。

图 11.主/从传输框图

时钟相位和极性控制

应用软件可以使用SPI控制寄存器1中的两个位来选择四种串行时钟相位和极性的组合之一。

CPOL时钟相位控制位指定高有效或低有效时钟,对于传输格式没有重要影响。

CPHA时钟相位控制位指定两种基本传输格式之一。

主机和对应从机的时钟相位和极性控制应该完全一致。在某些情况下,相位和极性会根据通信对象而改变,这样一个主机就可以与不同传输格式的外设从机进行通信了。

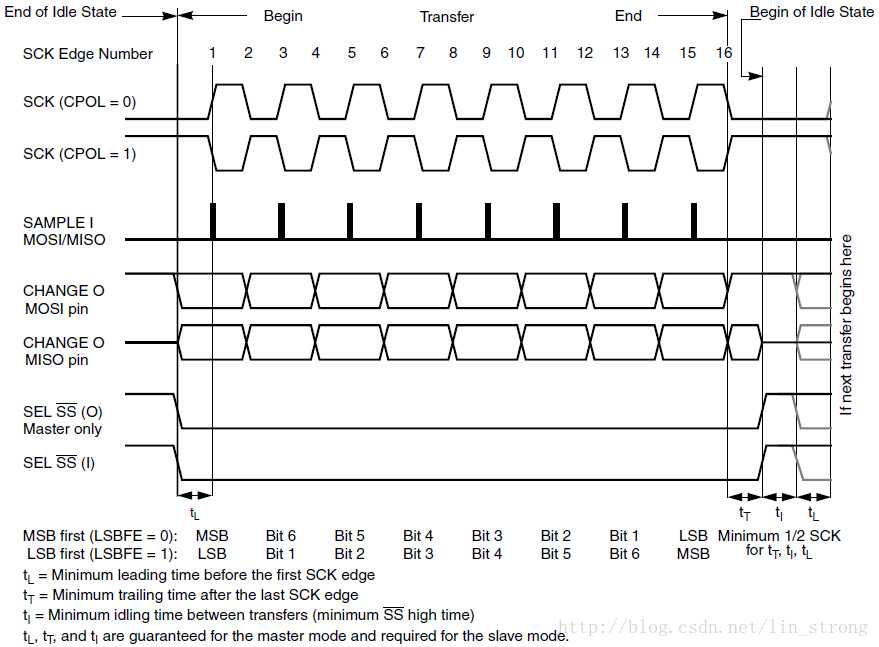

CPHA=0传输格式

SCK线的首个边沿用于锁存从机的首个数据位给主机以及锁存主机的首个数据位给从机。对于一些外设,从机一被选定就可以从从机的数据输出引脚得到从机数据的首个数据位。这种格式下,首个SCK边沿需要在

半个SCK周期后,SCK线上出现第二个边沿。当出现这第二个边沿时,之前从串行数据输入引脚上锁存的值被移位入SPI移位寄存器,移位方向取决于LSBFE位。

在这第二个边沿后,SPI主机数据的下一个位被传送到主机的串行输出引脚即从机的串行输入引脚。这个过程会重复2n次SCK线的边沿,每个奇数次边沿锁存数据,偶数次边沿移位数据。

数据接收是双缓冲的。在传输中,数据被串行地移位进SPI移位寄存器;在最后一个位传输完成后,数据被传输进并行SPI数据寄存器。

在2n次SCK边沿后:

- 之前在主机SPI数据寄存器中的数据现在应该在从机的数据寄存器中,反之亦然。

- SPI状态寄存器中的SPIF标志位被置位,表明传输过程已经完成。

图12是当CPHA=0时SPI传输的一张时序图。同时给出了当CPOL=0和1时的SCK波形。图表既是主机的时序图也是从机的,因为主机和从机的SCK、MISO和MOSI引脚是直接连在一起的。MISO信号线是从机的输出,MOSI信号线是主机的输出。主机的

图 12.SPI时钟格式0(CPHA=0),8位数据传输宽度(XFRW = 0)

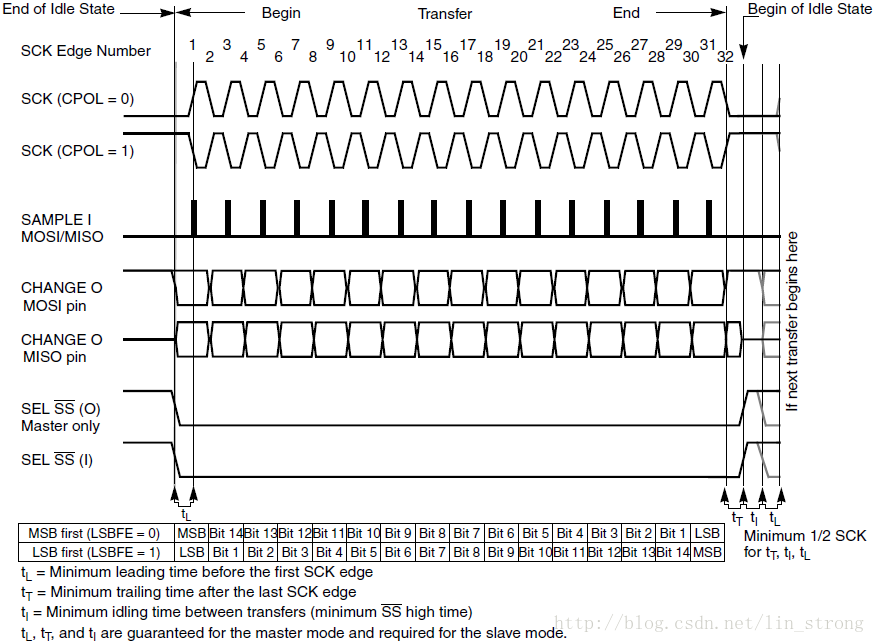

图 13.SPI时钟格式0(CPHA=0),16位数据传输宽度(XFRW = 1)

在从机模式下,如果在相继的传输间没有将

在主机模式下,只要使能了从机选定输出,

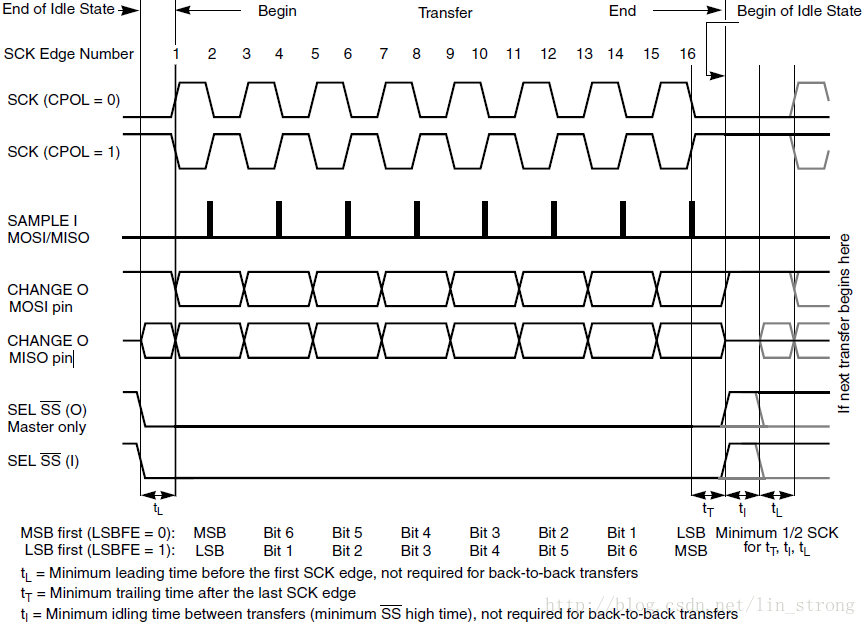

CPHA=1传输格式

一些外设要求要先有一个SCK边沿使得首个数据位在数据输出引脚上有效,然后在第二个边沿将数据锁存进系统。在这种格式下,首个SCK边沿是通过在n周期传输的开始设置CPHA位来发起的。

首个SCK边沿会在半个SCK时钟周期同步延迟后立即出现。这首个边沿会命令从机传输它的首个数据位到主机的串行数据输入引脚上。

半个SCK周期后,SCK引脚上出现第二个边沿。这是主机和从机的锁存边沿。

当第三个边沿出现时,之前从串行数据输入引脚上锁存的值被移位入SPI移位寄存器,移位方向取决于LSBFE位。这个边沿之后,主机会把其数据的下一个数据位输出到从机的串行输入引脚上。

这个过程会在SCK线上重复2n次边沿,每个偶数次边沿锁存数据,奇数次边沿移位数据。

数据接收是双缓冲的。在传输中,数据被串行地移位进SPI移位寄存器;在最后一个位传输完成后,数据被传输进并行SPI数据寄存器。

在2n次SCK边沿后:

- 之前在主机SPI数据寄存器中的数据现在应该在从机的数据寄存器中,反之亦然。

- SPISR中的SPIF标志位被置位,表明传输过程已经完成。

图14展示了当CPHA=1时两个时钟的变化。图表既是主机的时序图也是从机的,因为主机和从机的SCK、MISO和MOSI引脚是直接连在一起的。MISO信号线是从机的输出,MOSI信号线是主机的输出。

图 14.SPI时钟格式1(CPHA=1),8位数据传输宽度(XFRW = 0)

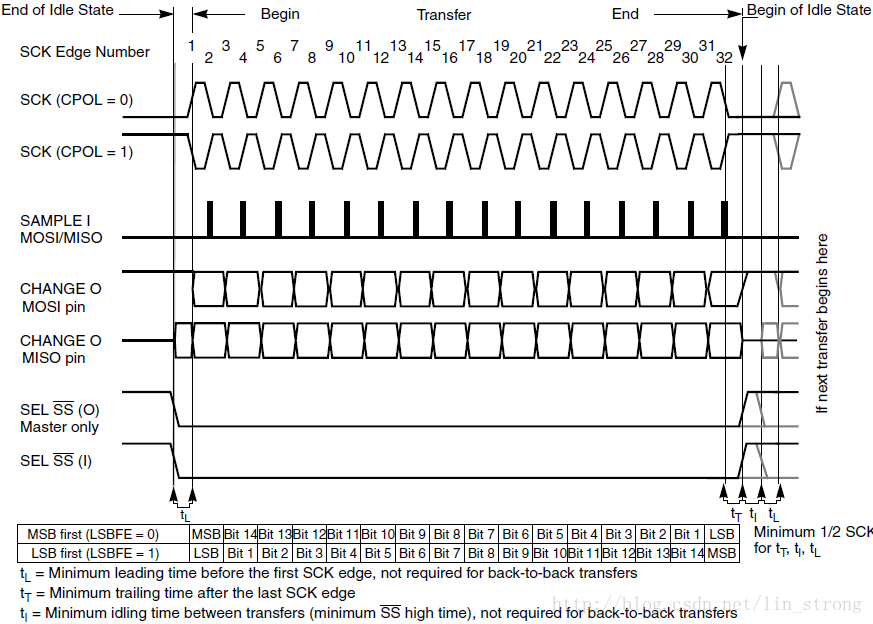

图 15.SPI时钟格式1(CPHA=1),16位数据传输宽度(XFRW = 1)

在相继的传输间,

- 主机模式下的背靠背传输

在主机模式下,如果一个传输已经完成并且新的数据进入了SPI数据寄存器,这个数据就会立刻发送出去,不用附加最小空闲时间。

SPI中断请求标志位(SPIF)对主机和从机模式是一致的。SPIF会在最后一个SCK边沿之后半个SCK周期被置位。

SPI波特率生成

波特率的生成包含一系列分频步骤。SPI波特率寄存器中的6个位(SPPR2、SPPR1、SPPR0、SPR2、SPR1和SPR0)决定了SPI模块时钟的分频系数,分频系数直接决定了SPI的波特率。

SPI时钟率由波特率预选位(SPPR2-SPPR0)和波特率选择位(SPR2-SPR0)的值确定。SPI模块时钟分频系数的公式如下:

比如:当所有位都是0(默认),SPI模块时钟直接除以2。当选择位(SPR2-SPR0)是001,预选位(SPPR2-SPPR0)是000,模块时钟分频系数变为4。当选择位为010,模块时钟分频系数变为8。

比如:当预选位为001,由选择位确定的分频系数乘了2倍。当预分频位为010,分频系数乘了3。表 7给出了在25MHz总线时钟下所有的可能性。这两个系数使得时钟能够不按2的幂数来分频,实现了其他波特率,比如除以6,除以10等。

只有SPI在主机模式下并且发生了串行传输时才会激活波特率生成器。在其他情况下,分频器会被禁用以降低 IDD 电流。

-

注意:

- 参阅这个数据手册的电气章节的SPI电气规范来得知允许的最小波特率。

特殊特性

输出

输出

当启用了

-

注意:

-

当在多主机系统中使用

输出特性时要特别小心,因为模式故障特性无法用于探测主机间的系统错误。

单线双向模式(MOMI或SISO)

当置位了SPI控制寄存器2中的SPC0位时就选择了单线双向模式(见表11)。在这种模式下,SPI只使用一条串行数据引脚与外部设备连接。MSTR位决定了使用哪一条引脚。对于主机模式,MOSI引脚成为了串行数据I/O(MOMI)引脚;对于从机模式,MISO引脚成为了串行数据I/O(SISO)引脚。SPI系统在主机模式下不使用MISO引脚,在从机模式下不使用MOSI引脚。

表 11.普通模式与单线双向模式

每个串行I/O引脚的方向取决于BIDIROE位。如果引脚被配置为输出,来自移位寄存器的串行数据就会驱动引脚。这个引脚同时也是移位寄存器的串行输入。

- SCK是主机模式的输出以及从机模式的输入。

是主机模式的输出或输入,但却总是从机模式的输入。

- 单线双向模式不会影响SCK和

的功能。

-

注意:

- 在单线双向主机模式下,当启用了模式故障,MISO和MOSI引脚都可能被SPI占用,尽管在这个模式下通常使用MOSI来传输而不使用MISO。如果发生了模式故障,SPI会自动地切换到从机模式。这样,MISO就被SPI使用,而MOSI就不用了。如果MISO引脚用于其他目的,一定要考虑这个。

错误状况

SPI有一种错误状况:

- 模式故障错误

模式故障错误

当SPI被配置为主机,如果

在SPI是主机模式而MODFEN位为0的特殊情况下,

如果发生了模式故障错误,SPI会切换到从机模式,除非从机输出缓存被禁用。这样SCK、MISO和MOSI引脚会强迫为高阻抗输入以避免与另一个输出设备发生冲突。在进行中的传输会被抛弃,SPI强制进入空闲状态。

如果配置为主机模式的SPI系统在单线双向模式下发生模式故障错误,MOMI(单线双向模式下的MOSI)的输出使能如果是1的话会被清零。配置为从机模式的SPI系统在单线双向模式下不会发生模式故障错误。

模式故障标志位可以通过读取SPI状态寄存器(MODF为1)然后写入SPI控制寄存器1来自动地清零。如果模式故障标志位被清零,SPI就会再次变成普通的主机或从机。

-

注意:

- 如果在发生模式故障错误的时候接收移位寄存器中有挂起的数据字节,那这个字节会丢失。

低能耗模式选项

Run模式下的SPI

在run模式下,如果SPI控制寄存器中的SPI系统使能(SPE)位为0,则SPI系统处于一种低能耗、禁用状态。SPI寄存器仍然可以访问,但是模块的时钟是禁用的。

Wait模式下的SPI

Wait模式下SPI的运行取决于SPI控制寄存器2中的SPISWAIT位。

- 如果SPISWAI为0,SPI当CPU在wait模式下正常运行

- 如果SPISWAI为1,SPI时钟生成会暂停,SPI模块当CPU在wait模式下进入节能状态。

- 如果置位了SPISWAI并且SPI被配置为主机,任何进行中的传输和接收都会在进入wait模式的时候停止。当退出wait模式时恢复传输和接收。

- 如果置位了SPISWAI并且SPI被配置为从机,如果来自主机的SCK继续运作,进行中的传输和接收都会继续。这会保持从机与主机和SCK的同步。

如果主机在从机处于wait模式时传输了多个字节,从机将继续发送与在等待模式开始时一样的字节。除非从机正在发送的是从主机接收到的最后一个字节,它将继续发送每个之前的主机字节。

-

注意:

- 如果当从机在wait或者stop模式下还想要从主机接收数据的话,要特别小心。尽管移位寄存器会继续工作,SPI的其它部分都关闭了(即不会产生SPIF中断直到退出stop或wait模式)。而且,来自移位寄存器中的字节不会被拷贝进SPIDR寄存器直到从机SPI已退出wait或stop模式。在从机模式下,在接收移位寄存器中挂起的收到的字节会在进入wait或stop模式时丢失。当且仅当在传输中进入或退出wait模式,会生成一份SPIF标志位和SPIDR的拷贝。如果从机在空闲模式下进入wait模式并在空闲模式下退出wait模式,SPIF和SPIDR拷贝都不会发生。

Stop模式下的SPI

Stop模式依赖于系统。当模块时钟被禁用(保持高电平或低电平),SPI进入停止模式。如果当CPU进入stop模式时,SPI处于主机模式下并且正在交互数据,传输会被冻结直到CPU退出stop模式。在恢复后,去或来自外部SPI的数据能被正确地交换。在从机模式下,SPI将与主机保持同步。

stop模式不依赖于SPISWAI位。

重置

寄存器和信号引脚的重置值在“内存映射与寄存器定义”中详细给出。

- 如果从机在重置后还没有数据写入SPIDR就发生了数据传输,它将传输无用数据,或者重置前最后一次从主机收到的数据。

- 在重置后从SPIDR读取的数据总是0。

中断

SPI只在被使能后(SPICR1中的SPE位为1)组织中断请求。以下是关于SPI是怎么生成一个请求以及MCU是怎么获得这请求的描述。中断向量偏移和中断优先级依赖于芯片。

中断标志位MODF、SPIF和SPTEF以 逻辑或 来生成中断请求。

MODF

当主机探测到

- MSTR = 0,SPICR1中的主机位重置。

MODF中断反映于状态寄存器的MODF标志位。清零这个标志位也将清除中断。这个中断将在MODF标志位为1时保持激活。MODF的自动清零序列描述在3.2.4 “SPI状态寄存器(SPISR)”中。

SPIF

SPIF发生于新数据被接收并拷贝进SPI数据寄存器时。在SPIF置位后,它不会被清零直到被处理。SPIF的自动清零序列描述在3.2.4 “SPI状态寄存器(SPISR)”中。

SPTEF

SPIEF发生于SPI数据寄存器准备好接收新数据时。在SPIEF置位后,它不会被清零直到被处理。SPIEF的自动清零序列描述在3.2.4 “SPI状态寄存器(SPISR)”中。

655

655

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?