NVIC 是一种片上控制器,可为 ARM Cortex-M MCU 中的中断驱动事件提供快速和低延迟的响应。在本教程中,我们将解释嵌套向量中断控制器(NVIC) 在 ARM Cortex-M 微控制器的中断处理请求中的作用。

中断介绍

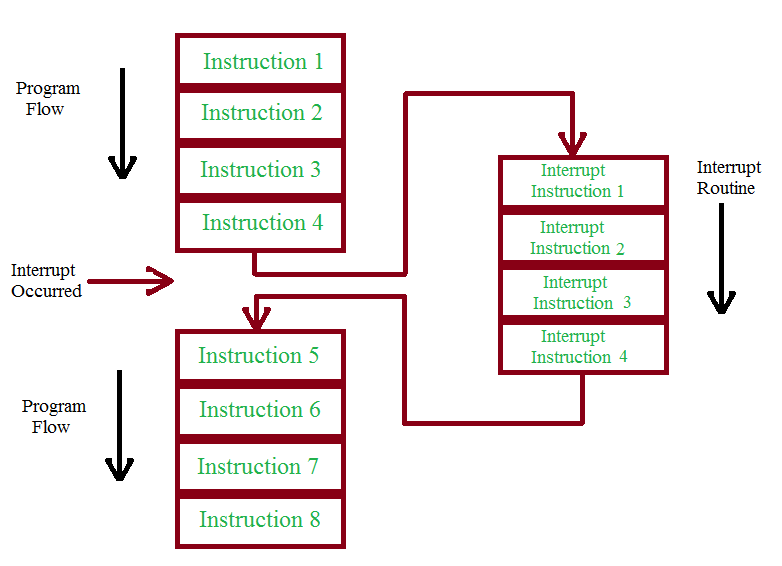

中断可以定义为系统异常或外围中断,它们可以导致程序流跳转到不同的位置。顾名思义,中断会妨碍正常的程序执行。硬件(即外部输入、复位按钮或其他外围设备)和软件(即内部输入或内核中断)都可以产生中断。如今,几乎每个微控制器都支持中断功能。

发生中断时会发生什么?

每当发生硬件或软件异常时,特定外设或外部/内部输入都需要对该中断作出响应。作为响应,会发生函数调用,并以称为服务例程 (SR) 或中断服务例程 (ISR) 的一段代码的形式执行所需的响应。在服务中的那组指令之后,执行例程,控制转移回发生中断的主程序。具体来说,当发生中断时,会执行以下一组步骤。

- 任何硬件或软件源都会产生中断。

- 处理器暂停当前运行的任务作为中断的响应。

- 之后,处理器会为中断服务程序(也称为中断处理程序)提供服务,以服务发生的中断。

- 然后处理器返回到挂起的任务并恢复其正常的程序执行。

什么是嵌套向量中断控制器?

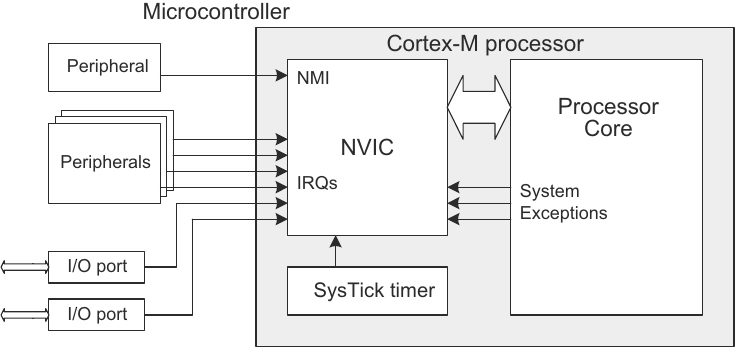

在 Cortex-M 微控制器中,通常称为 NVIC 的嵌套向量中断控制器用于处理 Cortex-M 支持的所有中断和异常。

嵌套向量中断控制器基本上是 Cortex-M 的一个集成部分,因为它与 Cortex-M 内核紧密集成。我们也可以根据需要使用特定的寄存器来配置中断控制器。大多数中断寄存器的操作模式是特权的,即它们只能在特权模式下访问,但如果中断是软件中断,那么这些寄存器也可以在用户模式下访问。NVIC的主要职责如下:

- 中断处理

- 可编程中断功能

- 中断尾链

- 低中断延迟管理

ARM Cortex-M 中的中断和异常

Cortex-M 总共支持 256 个中断。中断编号为 0-15,即前 16 个中断专用于系统中断,所有其他中断(即 16-255)称为用户或外设中断。根据 ARM 的命名法,中断是一种特殊的异常。简单来说,我们可以说所有的中断都是异常,但并不是所有的异常都被中断了。由于我们现在有了正常中断和 Cortex-M 中断处理程序的坚实背景,我们现在可以更深入地跳转到嵌套向量中断控制器 (NVIC)。

除了处理中断,NVIC 还包含一个称为SYSTICK 定时器的计时模块。此模块用作计时器的参考,系统(顾名思义)使用此计时器来管理其任务。正如我们所讨论的,Cortex-M 总共支持 256 个系统和用户异常/中断,这对于 NVIC 也是如此。它支持 240 (16-255) 个用户中断和 16(0-15) 个系统异常。这些数字不是常数,但它们可能会因硬件制造商而异。

嵌套向量中断控制器的主要特点

在上一节中,我们将讨论 NVIC 的主要职责和特点。

NVIC 中断处理

NVIC 的主要作用是处理中断。Cortex-M 包含一个向量表,其中包含中断服务例程 (ISR) 的地址以及每个中断号。下面给出了在发生中断时评估的步骤列表。

- 当前任务的执行被暂停。

- 程序的当前状态被保留。

- NVIC 启动对该向量表的调用,定位已发生的中断号,从该向量表中选择服务程序的地址。

- 之后,执行中断对应的服务。

- 程序的状态被保留,任务的正常执行被恢复。

NVIC 如何管理中断优先级

Cortex-M 架构为用户提供了一项功能,可以根据他们的使用和需要对中断进行优先级排序。前 16 个异常不能设置优先级,因为它们是系统异常,系统不会让用户更改其中断的优先级。此外,这些中断只能在特权模式下访问。但是,用户中断 (16-255) 可由用户编程。这些中断,无论是软件还是硬件,都可以由用户确定优先级,NVIC 在处理它们之前解码中断优先级。该工具允许 Cortex-M 用户配置基于 Cortex-M 架构的微控制器,以用于各种应用。

NVIC 中的“嵌套”一词是什么?

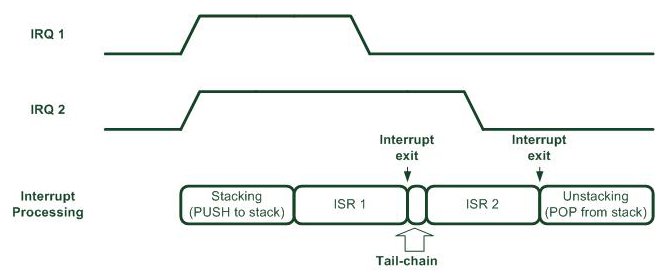

在谈论嵌套向量中断控制器时,中断嵌套是主要概念。这个概念有点类似于嵌套的for循环,即在另一个中断(具有较低优先级)中处理一个中断(具有较高优先级)。这可以使用 NVIC 来实现,因为 NVIC 允许我们设置每个中断的优先级,并且具有较高优先级的中断可以抢占具有较低优先级的中断,从而导致中断中的中断,这种对中断的抢占称为中断嵌套。

正如我们前面提到的,ARM Cortex-M 微控制器有 0-255 个异常/中断,每个异常都有一个优先级,一些异常是用户可编程的。这意味着在程序执行期间某些中断将具有比其他中断更高的优先级。此外,一些中断可以配置为关键中断或不可屏蔽。这意味着它们不能被禁用。

NVIC 的作用是管理所有低优先级和高优先级中断,即使低优先级中断发生得更早,高优先级中断总是在低优先级中断之前执行。

例如,如果发生低优先级中断并正在执行,如果发生更高优先级的中断。ARM CPU 会暂停低优先级中断,开始执行高优先级中断,如下图:

简而言之,NVIC的作用就是对每个中断的优先级进行解码,并根据其中断号和优先级进行处理。

NVIC 在中断延迟控制中的作用

NVIC 有助于确定中断的优先级,并有助于减少中断延迟。中断延迟定义为从中断发生时间到执行中断服务程序的第一条语句的时间间隔。NVIC 通过为应用程序提供更快的响应来帮助减少中断延迟。这反过来又快速执行中断并恢复程序流程。

NVIC 中断尾链

NVIC 支持的另一个概念是中断的尾链。这是中断嵌套的另一个名称,它有助于在不存在上下文切换问题的情况下连续执行中断。如果没有嵌套中断控制器,如果中断已经在执行,则即将到来的中断进入挂起状态,除非正在运行的中断完成其服务程序并返回程序并完成切换。然而,在嵌套中断中,我们不必这样做,并且在将控制权交还给调用程序之前,下一个中断会在第一个中断内执行。

当从低优先级任务到高优先级任务发生上下文切换,但低优先级任务的中断处理程序的执行仍在等待中。在这个过程中,低优先级的中断被链接起来,只有在所有高优先级的任务完成执行时才开始执行。

配置中断

嵌套向量中断控制器 (NVIC) 的前 16 个异常专用于系统异常,我们(作为用户)不允许配置或更改这些异常中的任何内容,系统会处理所有这些。接下来的 240 个中断是用户中断,我们有责任在这 16 - 255 个中断中配置和优先处理我们应用程序中需要的所有中断。在本节中,我们将讨论如何启动中断以及配置中断以使其准备好用于应用程序的步骤。

- 配置中断的第一步是全局启用中断。每个微控制器都有一个专用寄存器来启用微控制器中存在的所有中断,我们将设置寄存器的特定位并启用微控制器的所有中断。我们可以从该微控制器的技术参考手册中看到注册名称、地址和启用位。

- 在下一步中,我们将设置我们将要使用的每个中断的优先级。这是一个可选步骤,如果我们想要优先处理我们的中断,就需要实现它。如果当时我们不需要优先级,我们可以简单地跳过这一步。这样做会将所有中断的优先级设置为 0,这是一个中断的最高可配置优先级,如果同时发生 2 个中断,系统将决定首先处理哪个中断。

- 最后一步是启用我们想要使用的中断。例如,如果我们只想使用中断 20 和 21,我们不需要启用所有 240 中断。我们只会在我们的应用程序中启用这两个中断。

3128

3128

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?