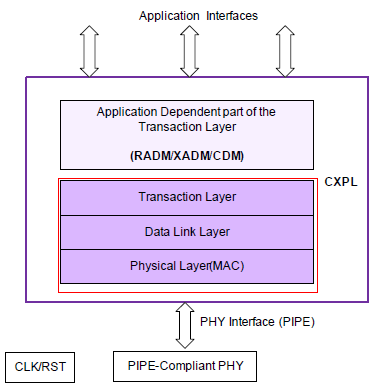

PCIe EP端控制器逻辑分为:应用层、事物层、链路层和物理层。

本文介绍的PCIe控制器逻辑主要包含以下几个部分:

- 端口逻辑(CXPL:Common Express Port Logic)。

- CXPL的主要组成部分包括:绝大部分事务层逻辑、全部的链路层逻辑和物理层中介质访问控制MAC逻辑,其中MAC逻辑实现了链路训练和链路状态机。

- CXPL与物理逻辑的硬IP通过PIPE连接。

- 应用层发送逻辑(XADM:Transmit Application-Dependent Module)。

- XADM主要包括:事物层协议(TLP:Transaction Level Protocol)仲裁、将应用数据包转换成TLP数据包、流控信令检查。

- 发送逻辑采用快通结构,即除了重传缓冲之外,发送通路上没有缓冲或队列,全部采用流水线实现TLP包的发送。

- XADM内部用LUT实现了一个目标完成查询表(TCLT:Target Completion Lookup Table)。当应用层通过发送接口发送一个读请求,XADM将应用层读请求转换成TLP读请求,并将该TLP读请求的头部信息存在TCLT中;最终,RADM会收到远端对该TLP读请求的响应报文,一般是TLP数据完成报文;只有正确接收到TLP数据完成报文,XADM才认为TLP读请求发送结束,应用层可以正确接收到数据。

- 应用层接收逻辑(RADM:Receive Application-Dependent Module)。

- RADM主要包括:将接收到的TLP数据包分类/排序/过滤、将接收到的TLP数据包放入队列、将接收到的TLP数据包路由到应用层接收接口。

- RADM内部用LUT实现了一个接收完成查询表(RCLT:Receive Completion Lookup Table)。RCLT可用于接收完成报文;RCLT还可以对应用层发送确认写请求进行超时监控,即本该在超时周期内收到一个完成报文,但并没有收到。

- 配置逻辑(CDM:Configuration-Dependent Module)。

- 标准PCIe配置空间。

- 控制器专用寄存器空间(端口逻辑寄存器),一般属于IOMem寄存器类。

- 电源逻辑(PMC:Power Management Controller)。

- 本地总线(LBC:Local Bus Controller)和数据总线接口(DBI:Data Bus Interface)

- 连接到DBI的CPU可以通过LBC访问以下资源,远程CPU可以通过PCIe总线最终可以通过LBC访问以下资源。

- CDM相关寄存器;

- 直连到ELBI上的外部应用层寄存器。

- 连接到DBI的CPU可以通过LBC访问以下资源,远程CPU可以通过PCIe总线最终可以通过LBC访问以下资源。

- 消息生成逻辑(MSG_GEN)。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?