💖 前置知识

-

置1:把开关打开(打上)

-

DR(Data Register):数据寄存器

-

AR(Address Register):地址寄存器

-

RAM(Random Access Memory):随机存取存储器

-

R0:R0寄存器

-

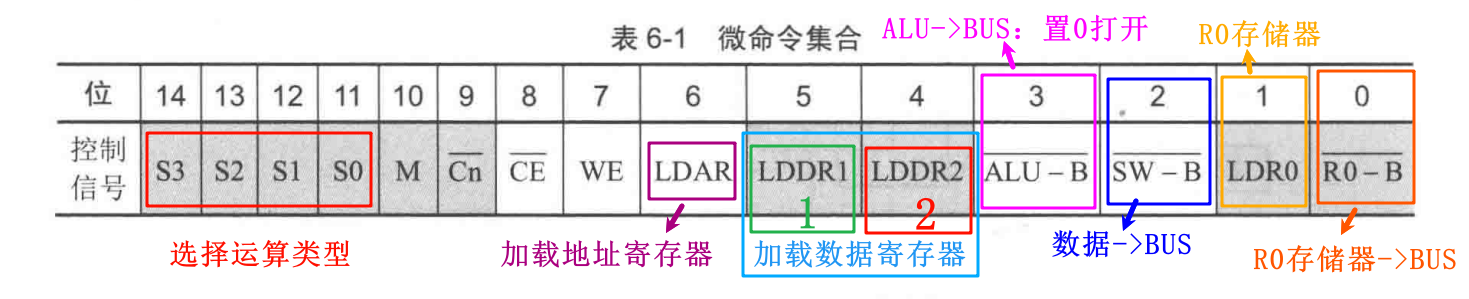

控制信号

- LDxx(load):从总线 输入(加载)数据到 xx

- xx-B:从 xx 输送数据到 总线

-

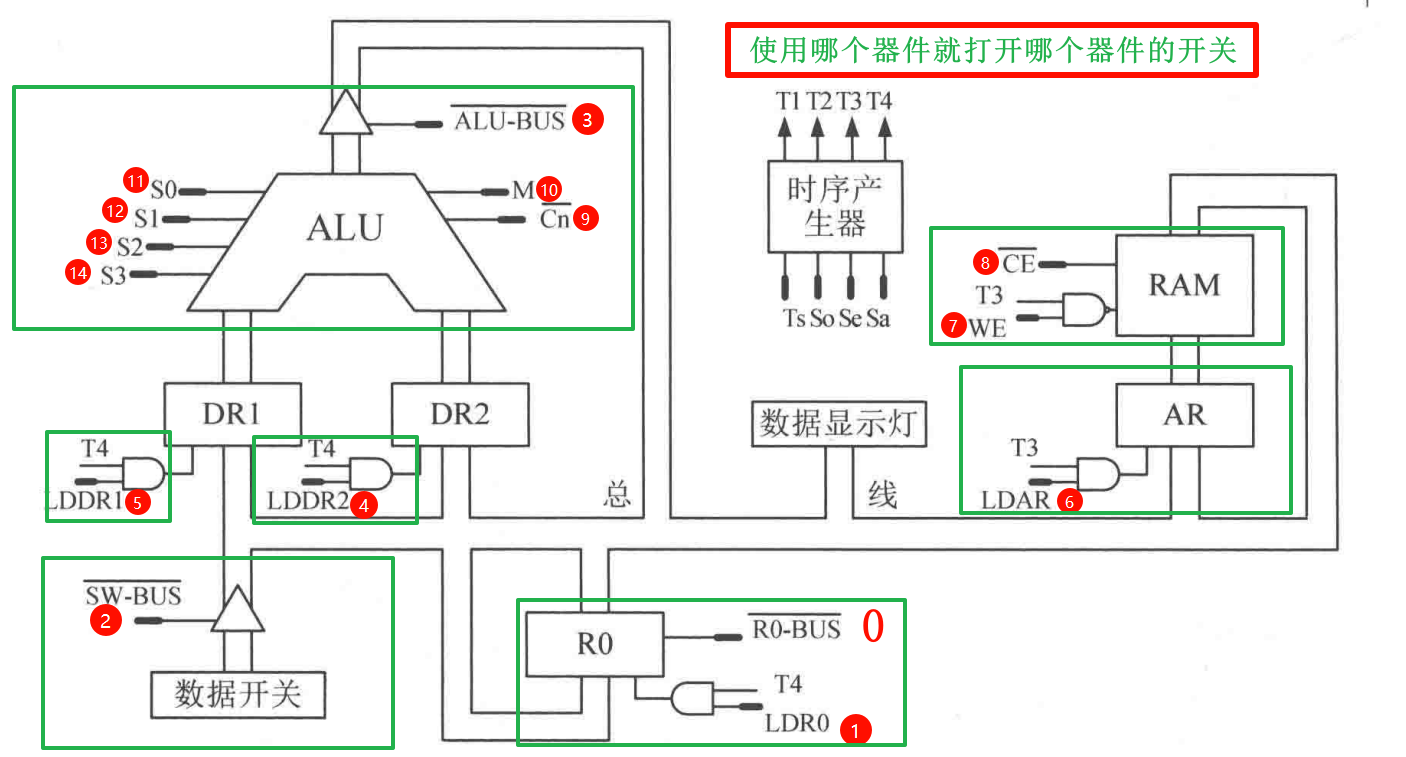

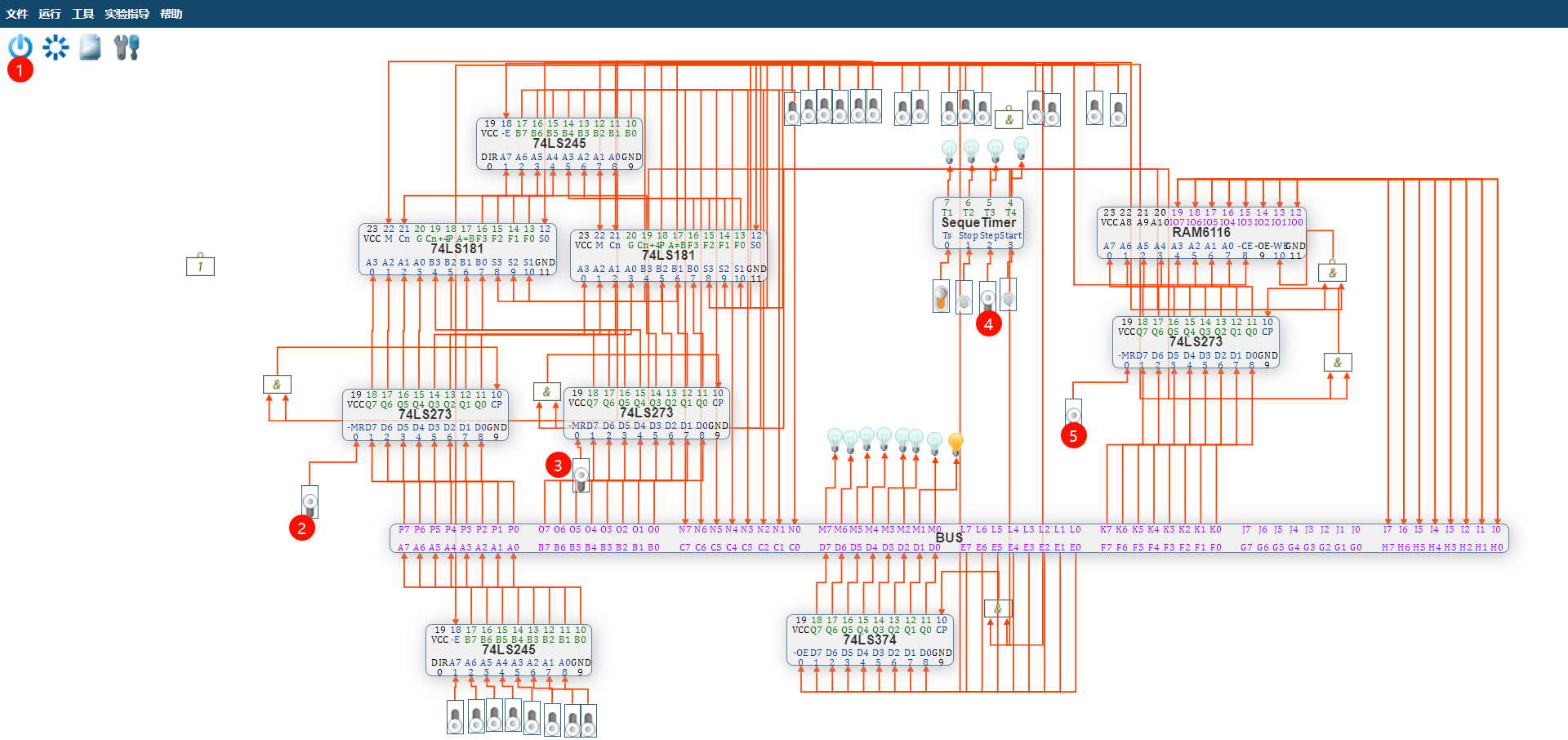

数据通路总框图

-

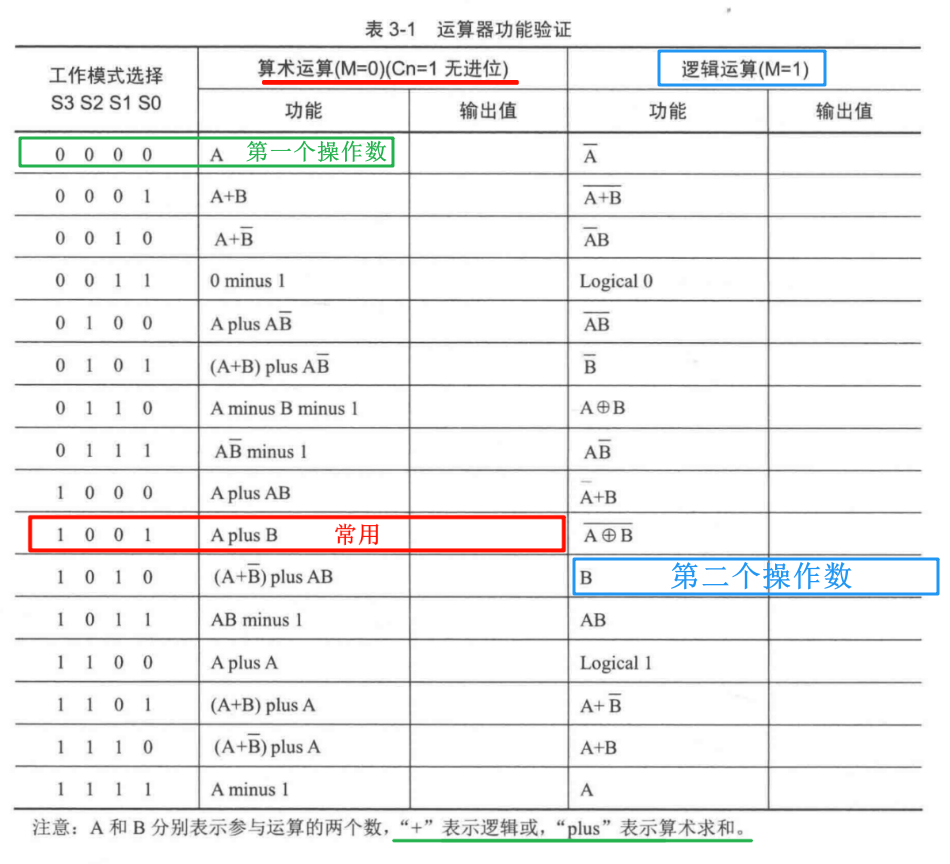

运算类型

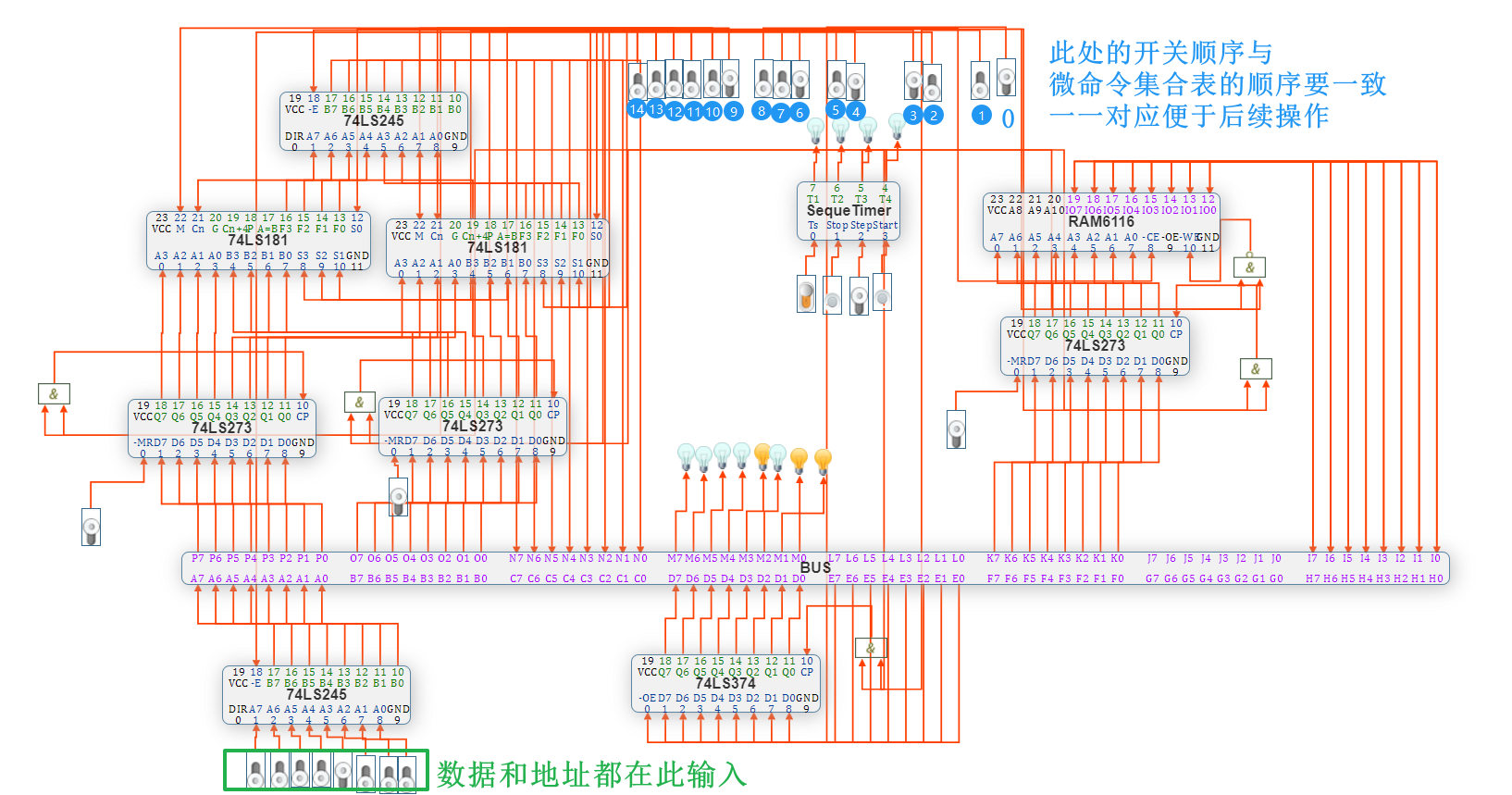

👨🏫 电路预设置

将 DR1 、DR2 和 AR 的 -MR位 置1, 时序发生器的 Step 置 1

有些电路图 DR1和DR2 的 -MR位 共用一个开关

😋 一波操作猛如虎

👨🏫 例子

例:求 3 + 5 ,存到存储器的某个位置

初始化(000001 100 00 11 01):全部关闭(低电平有效的位置 1)

① 把 3 存入DR1(000001 100 10 10 01):LDDR1(置1),SW-B(置0)

- 时序发生器:start

② 把 5 存入DR2(000001 100 01 10 01):LDDR2(置1),SW-B(置0)

- 时序发生器:start

③ DR1 + DR2 -> R0(100101 100 00 01 11):ALU-B(置0),LDR0(置1)

- 时序发生器:start

④ 存储单元地址 -> AR(000001 101 00 10 01):LADR(置1),SW-B(置0)

- 时序发生器:start

⑤ R0 -> 存储单元(000001 010 00 11 00):R0-BUS(置0),CE(置0),WE(置1)

- 时序发生器:start

👩🏫 补充

Tips:注意读取操作无需start ❗❗❗

- 读出DR1的数据到总线(LED):000001 100 00 01 01

- 读出DR2的数据到总线(LED):101011 100 00 01 01

- 读出R0的数据到总线(LED):00000 000 00 11 10

- 读出RAM6116存储器某地址到总线(LED)【

自求多福】:- 先指定存储单元地址 -> AR:000001 101 00 10 01

- 时序发生器:start

- 读取指定存储单元地址的数据:000001 000 00 11 01

👨🏫 减法:负数转补码运算

3686

3686

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?