目的:移植u-boot至FL2440开发板

操作系统:CentOS6.7(虚拟机)

开发板:FL2440开发板

交叉编译器:buildroot-2012.08

调试终端:SecureCRT

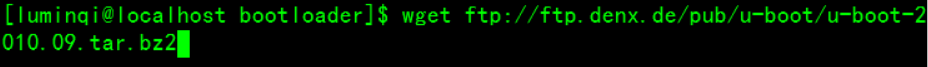

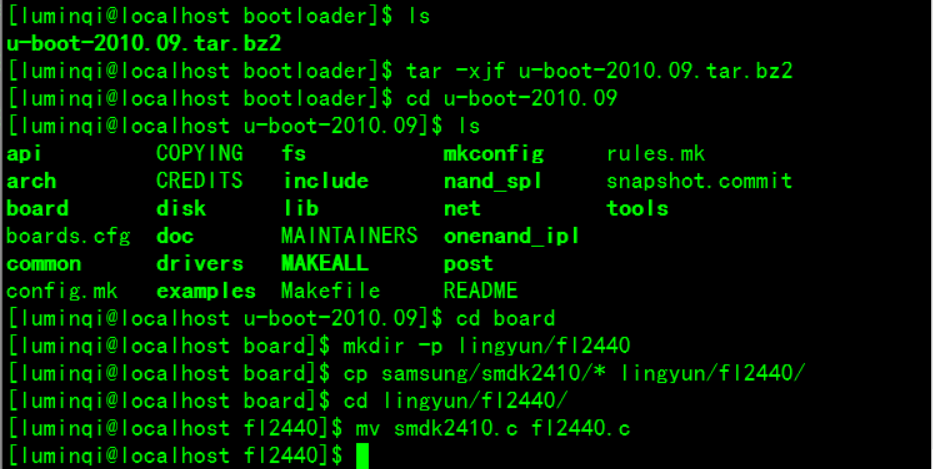

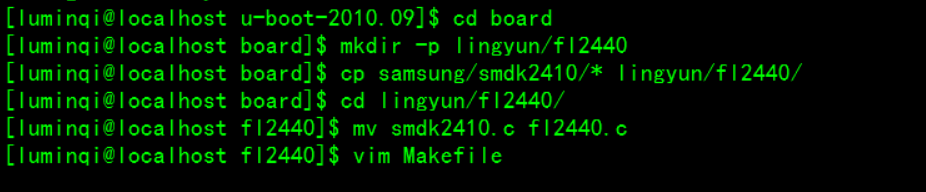

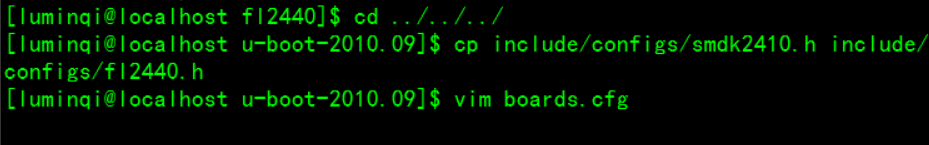

1.准备 u-boot 源码,U-boot 源码中添加 FL2440 开发板

-COBJS := smdk2410.o flash.o

+COBJS := fl2440.o flash.o

657 @@ -238,6 +238,7 @@

658 sbc2410x arm arm920t - - s3c24x0

659 smdk2400 arm arm920t - samsung s3c24x0

660 smdk2410 arm arm920t - samsung s3c24x0

661 +fl2440 arm arm920t fl2440 lingyun s3c24x0

662 voiceblue arm arm925t

663 omap1510inn arm arm925t - ti

664 afeb9260 arm arm926ejs - - at91

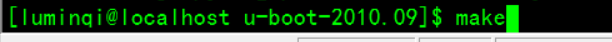

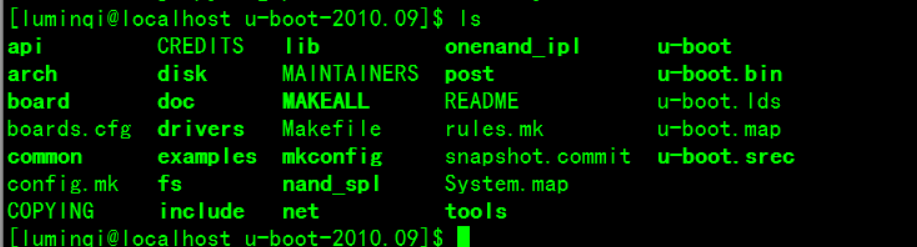

1.1 U-boot 初步编译测试

[luminqi@localhost u-boot-2010.09]$ vim Makefile

960 @@ -157,7 +157,7 @@

961

962 # set default to nothing for native builds

963 ifeq ($(HOSTARCH),$(ARCH))

964 -CROSS_COMPILE ?=

965 +CROSS_COMPILE ?== /opt/buildroot-2012.08/arm920t/usr/bin/arm-linux-

966 endif

967

968 # load other configuration

## 这里是交叉编译器的链路径,'=='后面不要留空格,否则找不到交叉编译器的路径##

进入顶层Makefile,有很多相对不同板子的配置,配置编译uboot第一步都是make *****_config。既然是make就得执行Makefile。Makefile就包括很多上面的语句,make *****_config,首先执行的就是上面的配置信息,这里即执行fl2440的配置。make xx_config会生成一个.config的隐藏文件。

这时候编译出来的 u-boot.bin 就是要烧到开发板上的 u-boot 文件,但这个代码是基于smdk2410 开发板的,我们并没有对这个代码作任何的修改,所以这个 bin 文件只能在smdk2410 这个开发板上跑。如果想运行在 FL2440 这个开发板上,接下来我们就要开始对源代码进行修改。

2.U-boot 移植之第一阶段汇编代码分析与修改

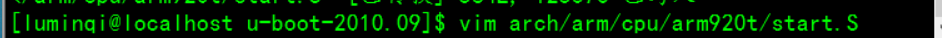

2.1 start.S 分析与修改

之前我们分析过 u-boot 是从 start.S 开始执行的,所以我们从 start.S 开始修改。

55 @@ -114,8 +114,8 @@

56 orr r0, r0, #0xd3

57 msr cpsr, r0

58

59 - bl coloured_LED_init

60 - bl red_LED_on

61 + @bl coloured_LED_init

62 + @bl red_LED_on

63

64 #if defined(CONFIG_AT91RM9200DK) || defined(CONFIG_AT91RM9200EK)

65 /*

66 @@ -159,13 +159,58 @@

67 ldr r1, =0x3ff

68 ldr r0, =INTSUBMSK

69 str r1, [r0]

70 -# endif

71

72 +#elif defined CONFIG_S3C2440

73 + ldr r1, =0x7fff

74 + ldr r0, =INTSUBMSK

75 + str r1, [r0]

76 +

77 +# endif

78 +# if defined(CONFIG_S3C2440)

79 +#define GPBCON 0x56000010

80 +#define GPBDAT 0x56000014

81 +#define GPBUP 0x56000018

82 +/*Set GPIO5, GPIO6, GPIO8, GPIO10 as GPIO OUTPUT mode*/

83 +ldr r0, =GPBCON

84 +ldr r1, [r0]

85 +bic r1, r1, #0x3c00 /*Set GPBCON for GPIO5,GPIO6 as 0x00 */

86 +orr r1, r1, #0x1400 /*Set GPBCON for GPIO5,GPIO6 as GPIOOUT, 0x01*/

87 +bic r1, r1, #0x00330000 /*Set GPBCON for GPIO8,GPIO10 as 0x00*/

88 +orr r1, r1, #0x00110000 /*Set GPBCON for GPIO8,GPIO10 as GPIOOUT, 0x01*/

89 +str r1, [r0]

90 +

91 +/*Set internal pullup resister*/

92 +ldr r0, =GPBUP

93 +ldr r1, [r0]

94 +orr r1, r1, #0x0560 /*Set bit 5,6,8,10, disable pullup resister*/

95 +str r1, [r0]

96 +ldr r2, =GPBDAT

97 +ldr r3, [r2]

98 +orr r3, r3, #0x0560 /*Set bit 5,6,8,10 as high level, Turn Off LED*/

99 +str r3, [r2]

100 +

101 +# define MPLLCON 0x4C000004

102 +# define MDIV_405 0x7f << 12

103 +# define PSDIV_405 0x21

104 +

105 +/* FCLK:HCLK:PCLK = 1:4:8 */

106 +ldr r0, =CLKDIVN

107 +mov r1, #0x05

108 +str r1, [r0]

109 +mrc p15, 0, r1, c1, c0, 0

110 +orr r1, r1, #0xc0000000

111 +mcr p15, 0, r1, c1, c0, 0

112 +Ldr r0,=MPLLCON

113 +mov r1, #MDIV_405

114 +add r1, r1, #PSDIV_405

115 +str r1, [r0]

116 +#else /*S3C2410, S3C2440 */

117 /* FCLK:HCLK:PCLK = 1:2:4 */

118 /* default FCLK is 120 MHz ! */

119 ldr r0, =CLKDIVN

120 mov r1, #3

121 str r1, [r0]

122 +#endif /* end of if defined(CONFIG_S3C2440) */

123 #endif /* CONFIG_S3C24X0 */

124

125 /*

126 @@ -183,6 +228,79 @@

127 cmp r0, r1 /* don't reloc during debug */

128 beq stack_setup

129

130 +judgment_norflash_nandflash_boot:

131 + ldr r1, =( (4<<28)|(3<<4)|(3<<2) )

132 + mov r0, #0

133 + str r0, [r1]

134 + mov r1, #0x3c

135 + ldr r0, [r1]

136 + cmp r0, #0

137 + bne norflash_boot

138 +/*Nandflash boot going here, recovery address 0x0000003C date*/

139 + ldr r0, =(0xdeadbeef)

140 + ldr r1, =( (4<<28)|(3<<4)|(3<<2) )

141 + str r0, [r1]

142 +

143 +nandflash_boot:

144 +#define LENGTH_UBOOT 0x60000

145 +#define NAND_CTL_BASE 0x4E000000

146 +/* Offset */

147 +#define oNFCONF 0x00

148 +#define oNFCONT 0x04

149 +#define oNFCMD 0x08

150 +#define oNFSTAT 0x20

151 + mov r1, #NAND_CTL_BASE

152 + ldr r2, =( (7<<12)|(7<<8)|(7<<4)|(0<<0) )

153 + str r2, [r1, #oNFCONF]

154 + ldr r2, [r1, #oNFCONF]

155 + ldr r2, =( (1<<4)|(0<<1)|(1<<0) ) @ Active low CE Control

156 + str r2, [r1, #oNFCONT]

157 + ldr r2, [r1, #oNFCONT]

158 + ldr r2, =(0x6) @ RnB Clear

159 + str r2, [r1, #oNFSTAT]

160 + ldr r2, [r1, #oNFSTAT]

161 + mov r2, #0xff @ RESET command

162 + strb r2, [r1, #oNFCMD]

163 + mov r3, #0 @ wait

164 +nand_delay:

165 + add r3, r3, #0x1

166 + cmp r3, #0xa

167 + blt nand_delay

168 +nand_wait:

169 + ldr r2, [r1, #oNFSTAT] @ wait ready

170 + tst r2, #0x4

171 + beq nand_wait

172 + ldr r2, [r1, #oNFCONT]

173 + orr r2, r2, #0x2 @ Flash Memory Chip Disable

174 + str r2, [r1, #oNFCONT]

175 + ldr sp, DW_STACK_START @ setup stack pointer

176 + mov fp, #0 @ no previous frame, so fp=0

177 + ldr r0, =TEXT_BASE

178 + mov r1, #0x0

179 + mov r2, #LENGTH_UBOOT

180 + bl nand_read_ll

181 + tst r0, #0x0

182 + beq ok_nand_read

183 +bad_nand_read:

184 +dead_loop:

185 + b dead_loop @ infinite loop

186 +ok_nand_read:

187 + @ verify

188 + mov r0, #0

189 + ldr r1, =TEXT_BASE

190 + mov r2, #0x400

191 +go_next:

192 + ldr r3, [r0], #4

193 + ldr r4, [r1], #4

194 + teq r3, r4

195 + bne notmatch

196 + subs r2, r2, #4

197 + beq stack_setup

198 + bne go_next

199 +notmatch:

200 +infinite_loop:

201 + b infinite_loop @ infinite loop

202 +norflash_boot:

203 ldr r2, _armboot_start

204 ldr r3, _bss_start

205 sub r2, r3, r2 /* r2 <- size of armboot */

206 @@ -215,12 +333,21 @@

207 add r0, r0, #4

208 cmp r0, r1

209 ble clbss_l

210 + ldr r1, =GPBDAT

211 + ldr r2, [r1]

212 + bic r2, r2, #(1<<5)

213 + str r2, [r1]

214

215 ldr pc, _start_armboot

216

217 _start_armboot: .word start_armboot

218

219 -

220 +#ifdef CONFIG_S3C24X0

221 +#define STACK_BASE 0x33f00000

222 +#define STACK_SIZE 0x10000

223 + .align 2

224 +DW_STACK_START: .word STACK_BASE+STACK_SIZE-4

225 +#endif

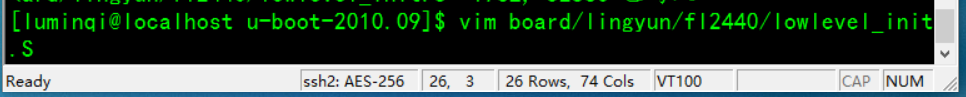

2.2 lowlevel_init.S 分析与修改

394 @@ -51,7 +51,7 @@

395 #define WAIT

本文详细介绍了如何将u-boot移植到FL2440开发板上,包括源码修改、交叉编译配置、汇编代码分析与修改、添加DM9000网卡驱动以及Nandflash支持。通过修改Makefile、start.S、lowlevel_init.S等文件,以及调整board/lingyun/fl2440/fl2440.c和include/configs/fl2440.h,实现了u-boot针对FL2440开发板的定制。移植过程中需注意防火墙设置、IP配置和J-link的使用。

本文详细介绍了如何将u-boot移植到FL2440开发板上,包括源码修改、交叉编译配置、汇编代码分析与修改、添加DM9000网卡驱动以及Nandflash支持。通过修改Makefile、start.S、lowlevel_init.S等文件,以及调整board/lingyun/fl2440/fl2440.c和include/configs/fl2440.h,实现了u-boot针对FL2440开发板的定制。移植过程中需注意防火墙设置、IP配置和J-link的使用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2162

2162

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?