点击上方"蓝字"关注我们

01、IIC概述

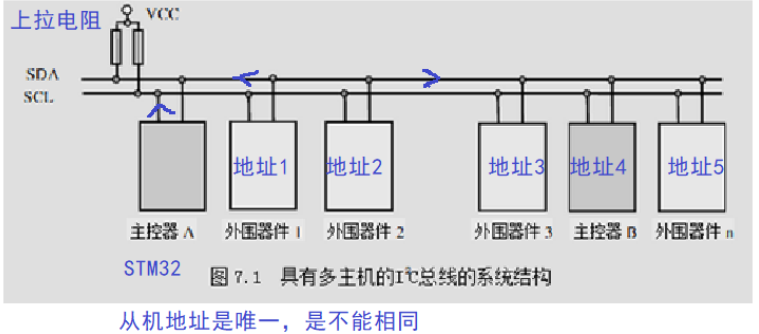

I2C(IIC,Inter-Integrated Circuit),两线式串行总线,由PHILIPS公司开发用于连接微控制器及其外围设备。

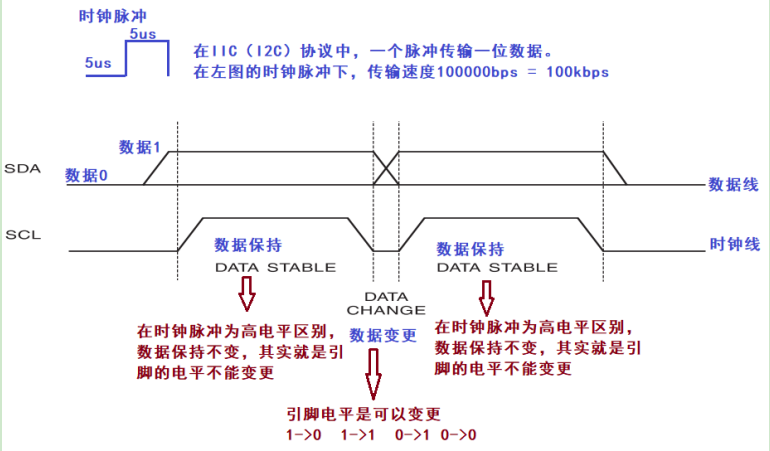

它是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。在CPU与被控IC之间、IC与IC之间进行双向传送,高速IIC总线一般可达400kbps。

IIC是半双工通信方式,可实现一对多。

-

SDA:数据线,用于传输数据;可主机到从机,也可以从从机到主机。

-

SCL:时钟线,只能由主机发送

-

-

,用于数据同步,一个脉冲发送/接收一位数据。

02、I2C通信原理/协议

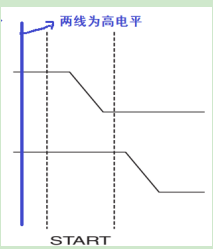

l空闲状态

l开始信号

l停止信号

l应答信号

l数据的有效性

空闲状态

I2C总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

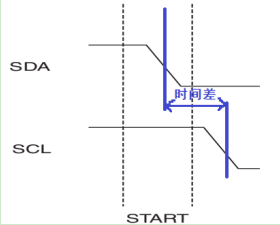

起始信号(主机发出,起始信号是针对所有的从机)

起始信号:当SCL为高期间,SDA由高到低的跳变;启动信号是一种电平跳变时序(上升沿或者下降沿)信号,而不是一个电平信号(高电平或者低电平)。

注意看启动信号的时序是由左到右进行查看。

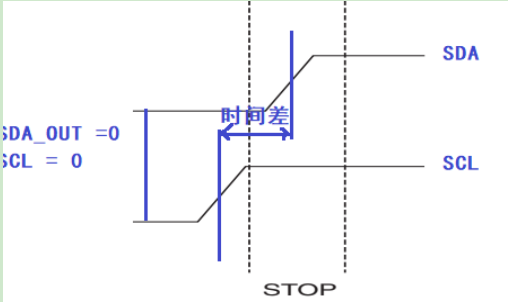

停止信号(主机发出)

停止信号:当SCL为高期间,SDA由低到高的跳变;停止信号也是一种电平跳变时序信号,而不是一个电平信号。

注意看停止信号的时序是由左到右进行查看。

数据有效性

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

即:数据在SCL的上升沿到来之前就需准备好。并在在下降沿到来之前必须稳定。

注意:在主机接受数据时,使用是的上面相同的时序,只不过SCL由主机发出,SDA由从机发出,那么主机要做为输入,进行接受数据。同样的道理,在SCL为低电平区间,从机在这区间可改变数据,在SCL为高电平区间保持数据的稳定。所以主机在SCL为高电平区间判断引脚的电平从而得到对应的数据。

应答信号ACK

发送器(STM32或者是从机)每发送一个字节,就在时钟脉冲9(前面8个脉冲周期用来发8位)期间释放数据线,由接收器反馈一个应答信号(反馈:发送一位数据,做为应答)。 应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。

对于反馈有效应答位ACK的要求是,接收器在第9个时钟脉冲之前的低电平期间将SDA线拉低,并且确保在该时钟的高电平期间为稳定的低电平。如果接收器是主控器,则在它收到最后一个字节后,发送一个NACK信号,以通知被控发送器结束数据发送,并释放SDA线,以便主控接收器发送一个停止信号P。

结论:

(1)每发送(主机与从机都适用)一个字节,则会(主机与从机都适用)接受一个应答信号(信号其实就是一位数据);每接收(主机与从机都适用)一个字节,则会(主机与从机都适用)发送一位应答信号(信号其实就是一位数据);

(2)规定低电平为有效应答,表示成功接受字节;规定高电平为无效应答,表示没有成功接受字节。

(3)假设主机接受数据,如果不想再接受,则发送一个无效应答(非应答)来通知从机不要再进行传输数据。

总结

天局,以自己为棋子,以写代码为代价,特别天真,英雄!!!工具!!!英雄在权力面前是拗不过的。

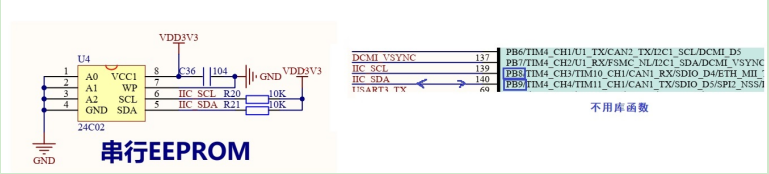

01、AT24C02

02、简介

l24C02是一个2K位串行CMOS 的EEPROM,内部含有256个8位字节(大小:256字节)。

l与 400KHz I2C 总线兼容

l1.8 到 6.0 伏工作电压范围

l低功耗 CMOS 技术

l写保护功能 当 WP 为高电平时进入写保护状态

l页写缓冲器

l自定时擦写周期

l1,000,000 编程/擦除周期

l可保存数据 100 年

l8 脚 DIP SOIC 或 TSSOP 封装

l温度范围 商业级 工业级和汽车级

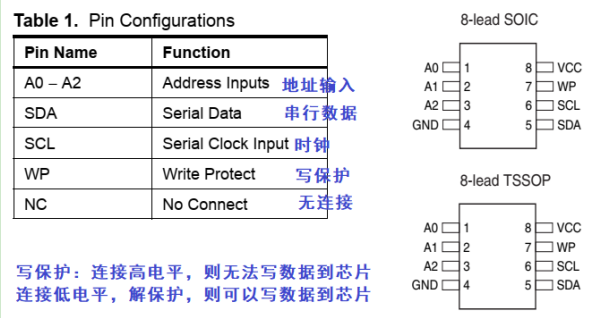

03、引脚

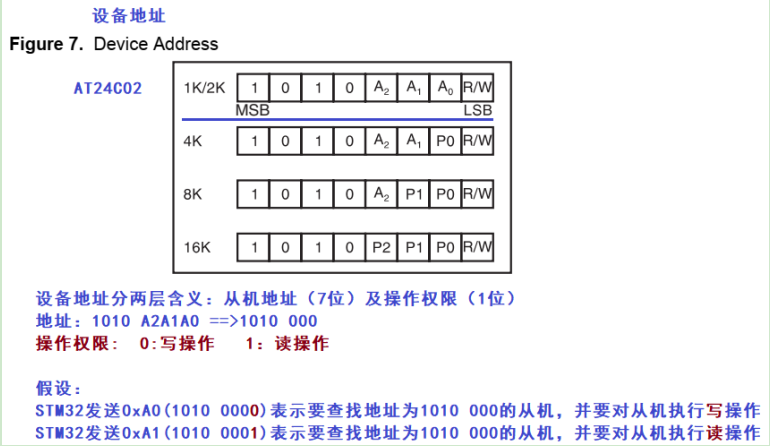

04、地址查找

开发板址址:A2 = 0, A1 = 0, A0 = 0;

1、LSB的意思是:全称为Least Significant Bit,在二进制数中意为最低有效位,一般来说,MSB位于二进制数的最左侧,LSB位于二进制数的最右侧。

2、MSB的意思是:全称为Most Significant Bit,在二进制数中属于最高有效位,MSB是最高加权位,与十进制数字中最左边的一位类似。

05、读写时序

写时序

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1452

1452

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?