若有不当或错误, 敬请批评指正!

加油,加油,加油!!!!

目录

2021年8月29日:更新三种映射的地址计算

一、填空题

1,cpu的组成:运算器+控制器

2,软件的分类:应用软件和系统软件

3,cache命中率计算:

题目:假设某计算机的存储系统由cache和主存组成。某程序执行过程中访存1000次,其中访问cache未命中100次,则cache的命中率是 90% .

解:(1000-100)/ 1000=900/1000=90%

注:Nc表示cache完成存取总次数,Nm表示主存完成存取总次数,h表示 cache 命中率 h = Nc / ( Nc + Nm )

4,根据定义选择映射方式:

题目:在Cache的地址映射中,凡主存中任意一块均可映射到Cache内的任意一块位置上,则这种映射方法称为 全相联映射

cache内存的地址映射主要有以下三种方式:

①、直接映射: 指主存的一个字块只能映像到Cache的一个准确确定的字块中。 特点:主存的字块只可以和固定的Cache字块对应,方式直接,利用率低。

②、全相联映射: 全相联映射是指主存中任意一个块都可以映射到Cache中任意一个块的方式,也就是说,当主存中的某一块需调入Cache时,可根据当时Cache的块占用或分配情况,选择一个块给主存块存储,所选的Cache块可以是Cache中的任意一个块。 特点:贮存中的字块可以和Cache的任何字块对应,利用率高,方式灵活,标记位较长,使用成本太高。

③、组相联映射: 是对全相联和直接映像的一种折中的处理方案。既不在主存和Cache之间实现字块的完全随意对应,也不在主存和Cache之间实现字块的多对一的硬性对应,而是实现一种有限度的随意对应。 特点:折中方案。组间全相联,组内直接映像。集中了两个方式的优点。成本也不太高。最常见的Cache映像方式。

地址计算

主存地址长度:主存中存储单元个数为

,则主存地址长度就是10

Cache地址长度:Cache中存储单元个数为

,则Cache地址长度就是10

t:主存地址长度 - Cache地址长度

c:Cache可以被分为块 m:主存可以被分为块

b:块长为2的b次方(按访存地址计算)

m = t + c

m=主存地址长度 - b

主存地址长度 = t + c + b

2.全相联映射

全相联中的t,c,b,m和直接映射中的都一样

3.组相联映射

2的c次方表示Cache的总块数

2的q次方 表示Cache分组个数(分组个数=分块个数/组内块数)

2的r次方 表示组内包含的块数(r=1,每组包含2块,叫做二路组相联)

s = t + r

q = c - r

5,cpi的计算:CPI=总的时钟周期数/IC IC为总的指令数

6,寄存器-寄存器,寄存器-存储器,存储器-存储器三种类型速度快慢/三类指令中,哪类指令的执行时间最长?

速度:寄存器-寄存器>寄存器-存储器>存储器-存储器

时间长短:存储器-存储器>寄存器-存储器>寄存器-寄存器

存储器-存储器最长(慢),寄存器-寄存器最短(快),因为不用经过内存 寄存器一般是集成CPU的内部,而存储器是在CPU的外部 寄存器的存取时间与存储器的存取时间不是一个数量级,前者要快很多

7,总线判优 集中式中三种方式及其特点

对电路故障最敏感的是:链式查询方式

响应速度最快的是:独立请求方式

①.链式查询方式:

注:在查询链中离总线控制器最近的部件具有最高优先权,离总线控制器越远,优先权越低。 链式查询通过接口的优先权排队电路实现。

优点:结构简单,主要运用在简单的嵌入式系统中

缺点:速度慢,需要一直向下查询,对电路故障特别敏感

BR(Bus Request) 总线请求线 ;BG (Bus Grant ) 总线响应线;BS(Bus State) 总线状态线。

②.计数器定时查询方式:

注:计数器的初值可用程序设置,以方便地改变优先次序。当然这种灵活性是以增加控制线数为代价的。

如果计数器的初值是从0开始,各部件的优先次序与链式查询法相同。

如果从中止点开始,则每个设备使用总线的优先级相等。

BR(Bus Request) 总线请求线 ;BS(Bus State) 总线状态线。没有BG线。

③.独立请求方式

优点:响应时间快,对优先次序的控制相当灵活

缺点:控制线数增加了很多

BR(Bus Request) 总线请求线 ;BG (Bus Grant ) 总线响应线;没有BS线。

例题:在集中式总线控制独立请求方式下,若有N个设备,则( )

A.有N个总线请求信号和1个总线响应信号

B.有N个总线请求信号和N个总线响应信号

C.有1个总线请求信号和N个总线响应信号

D.有1个总线请求信号和1个总线响应信号

8,I/O设备与主机交换信息时,共有哪几种控制方式?

①程序直接控制方式:也称查询方式,采用该方式,数据在CPU和外设间 的传送完全靠计算机程序控制,CPU的操作和外围设备操作同步,硬件结构简单,但由于外部设备动作慢,浪费CPU时间多,系统效率低。

②程序中断方式:外设备准备就绪后中断方式主动通知CPU,在CPU相应 I/O设备的中断请求后,在暂停现行程序的执行,转为I/O设备服务可明显提高CPU的利用率,在一定程度上实现了主机和I/O设备的并行工作,但硬件结构负载,服务开销时间大

③DMA方式与中断方式一样,实现了主机和I/O设备的并行工作,由于DMA 方式直接依靠硬件实现贮存与I/O设备之间的数据传送,传送期间不需要CPU程序干预,CPU可继续执行原来的程序,因此CPU利用率和系统效率比中断方式更高,但DMA方式的硬件结构更为复杂。

I/O与主机交换信息的控制方式中, 程序查询 方式CPU和设备是串行工作的。

程序中断 和 DMA方式 CPU和设备是并行工作的,前者传送与主程序是并行的,后者传送和主机是串行的。

9,给出芯片存储容量 ,计算总位数:

某DRAM芯片,其存储容量为512K×8位,该芯片的地址线和数据线数目为19, 8 ,总位数为 27

解:由存储容量可知,512K=2的9次方K=2的19次方,即地址线位数位19位,数据线位数为8位,故总位数为19+8=27位。

另一种题型:若一存储有m根地址线,n根数据线,则其存储容量最大可达到:2的m次方×n

例:存储器有10根地址线,8根数据线(8位输出),则存储容量为 1K×8位

解:2的10次方 ×8位,因为 2的10次方=1K,所以为1K×8位。

10,忘了,暂时想不起来了.......

二、选择题

1,立即寻址,直接寻址,间接寻址速度排序:立即>直接>间接

2,

存储器的层次结构:

缓存–主存层次主要解决CPU和主存速度不匹配的问题。由于缓存的速度比主存的速度高,只要将CPU近期要用的信息调入缓存,CPU便可以直接从缓存中获取信息,从而提高访存速度。但由于缓存的容量小,因此需不断地将主存的内容调入缓存,使缓存中原来的信息被替换掉。主存和缓存之间的数据调动是由硬件自动完成的,对程序员是透明的。

主存-辅存层次主要解决存储系统的容量问题。辅存的速度比主存的速度低,而且不能和CPU直接交换信息,但它的容量比主存大得多,可以存放大量暂时未用到的信息。当CPU需要用到这些信息时,再将辅存的内容调人主存,供CPU直接访问。主存和辅存之间的数据调动是由硬件和操作系统共同完成的。

3,冯诺依曼特点

冯•诺依曼(Von Neumann)机工作方式的基本特点是什么。

A、多指令流单数据流

B、按地址访问并顺序执行指令

C、堆栈操作

D、存储器按内容选择地址

冯.诺依曼计算机的特点是:

①计算机由运算器、控制器、存储器、输入设备、输出设备五大部件组成;

②指令和数据以同同等地位存放于存储器内,并可以按地址访问;

③指令和数据均用二进制表示;

④指令由操作码、地址码两大部分组成,操作码用来表示操作的性质,地址码用来表示操作数在存储器中的位置;

⑤指令在存储器中顺序存放,通常自动顺序取出执行;

⑥机器以运算器为中心(原始冯·诺依曼机)。

关于冯·诺依曼计算机的例题:

①现代计算机组织结构是以( )为中心,其基本结构遵循冯•诺依曼思想。

A、 寄存器 B、 存储器 C、 运算器 D、 控制器

②下列描述中正确的是哪个?

A、控制器能够识别、解释和执行所有的指令及存储结果

B、计算机主要由输入输出单元、控制器、存储器和算术逻辑单元构成

C、所有的数据运算都在控制器中完成

D、其它三者都正确 冯•诺依曼计算机中,

③CPU区分从存储器取出的是指令还是数据的依据是什么?

A、指令译码结果的不同

B、访问指令和访问数据时寻址方式不同

C、访问指令和访问数据时所处的指令执行阶段不同

D、指令和数据所在的存储单元地址范围不同

④以下有关冯•诺依曼结构计算机指令和数据表示的叙述中,正确的是什么?

A、指令和数据可以 从形式上加以区分

B、指令以二进制形式存放,数据以十进制形式存放

C、指令和数据都以二进制形式存放

D、指令和数据都以十进制形式存放

⑤冯•诺依曼计算机工作方式的基本特点是是什么?

A、程序从键盘输入的同时被计算机执行

B、程序直接从磁盘被 读到CPU中执行

C、程序中的指令按地址被访问并自动按序执行

D、程序被自动执行而数据通过手工输入。

⑥以下是关于冯诺依曼计算机结构的叙述中,其中错误的是是什么?

A、计算机由运算器、控制器、存储器和输入输出设备组成

B、程序由指令和数据构成,存放在存储器中

C、指令由操作码和地址码两部分组成

D、指令按地址访问,所有数据在指令中直接给出

⑦以下关于冯•诺依曼计算机工作方式的叙述中,错误的是什么 。

A、计算机完成的所有任务都必须通过执行相应的程序来完成

B、某任务用某语言(如 C++)编好程序后,一旦被启动,则马上可调至主存直接执行

C、程序执行时,CPU 根据指令地址自动按序到内存读取指令并执行

D、冯•诺依曼计算机工作方式为“存储程序”控制方式

4,

控制部件通过控制线向执行部件发出各种控制命令,通常这种控制命令叫做微命令,是最小单位,组成微指令,而执行部件接受微命令后所执行的操作就叫做微操作。

在机器的一个CPU周期中,一组实现一定操作功能的微命令的组合,构成一条微指令。

事实上一条机器指令的功能是由许多条微指令组成的序列来实现的。这个微指令序列通常叫做微程序。

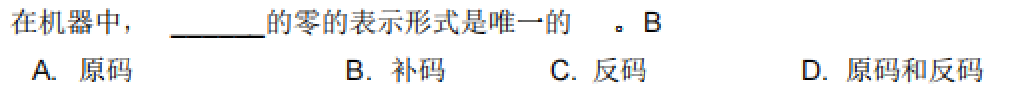

5,

注:移码的零的表示形式也是唯一的

6.缓存,寄存器,辅存...特性比较

记住这幅图就好

7,浮点数的表示范围和精度取决于______。

A.阶码的位数和尾数的位数

B.阶码采用的编码和尾数的位数

C.阶码的位数和尾数采用的编码

D.阶码采用的编码和尾数采用的编码

8,指令系统中采用不同寻址方式的目的主要是

A、实现存储程序和程序控制

B、缩短指令长度、扩大寻址空间、提高编程灵活性

C、可以直接访问外存

D.提供扩展操作码的可能并降低指令译码难度

9,I/O采用统一编址时,进行输入输出操作的指令是()。

A、控制指令

B、访存指令

C、输入输出指令

D、伪指令

10,

加法器电路相对于减法器来说要简单很多,成本就少很多

三、简答计算题

1,补码定点加减法计算

①会计算 (X+Y)补=X补+Y补 (X-Y)补=X补+(-Y补)

②判断是否溢出,若溢出说明上(正)溢还是下(负)溢

2,寻址方式

①根据给出地址根据表格可计算查询到操作数

例:某计算机有变址寻址、间接寻址和相对寻址等方式,设当前指令的地址码部分为001AH,正在执行的指令所在地址为1F05H,变址寄存器中的内容为23A0H,已知存储器的部分地址及相应内容如图,请填充:

地址

内容

001AH

23A0H

1F05H

2400H

1F1FH

2500H

23A0H

2600H

23BAH

1700H

(1)当执行取指令时,如为变址寻址方式则取出的数为(1700H)

(2)如为间接寻址方式则取出的数为(2600H)

(3)当执行转移指令时,转移地址(1F21H)

解: 1 变址寻址,操作数的有效地址是 变址寄存器的内容+指令地址码的部分. 23A0+001A=23BAH,对应的内容就是1700H.

2 间接寻址方式,指令的操作码部分给出的是操作数的有效地址的地址,也就是说001AH的内容是操作数的有效地址,001A中是23A0H.地址为23A0H中的内容就是操作数,也就是2600H.

3 转移指令采用的是相对寻址,是地址码部分+PC的值形成有效地址.当前指令的地址为是1F05H,也就是PC的值.按照答案看,取出当前的指令后,PC的值会加2.就变成了1F07H,再加上001A,就是1F21H.这就是转移的地址. PC的值怎么变化要给出具体的规定.本题是指令取出1个字节,PC+1.

若该计算机还有立即寻址,则取出的数即为指令的地址码:001AH, 若有直接寻址,则取出的数为:地址码001AH对应的23A0H。

3,异步串行通信字符

①给出格式,计算波特率

②根据格式写出给定数字的异步串行通信字符

波特率为单位时间内传输的二进制数据的位数

比特率为单位时间内传输的二进制有效数据的位数

例:在异步串行传送系统中,字符格式为:1个起始位、8个数据位、1个校验位、2个终止位。若要求每秒传送120个字符,试求传送的波特率和比特率。

解: 一帧 =1+8+1+2 =12位

波特率 =120帧/秒×12位 =1440波特

比特率 = 1440波特×(8/12 =960bps

或:比特率 = 120帧/秒×8 =960bps

起始位+数据位+校验位+终止位

起始位:一般为0

数据位:从数据最低位开始传输

校验位:一般为1位,奇偶校验,值为0或1

终止位:一般为1位有时也可以为2位,值一般为1

具体位数看题目规定

例 用异步串行传输方式发送8位十六进制数据95H。要求字符格式为:1位起始位、8位数据位、1位偶校验位、1位终止位。

解:95H=1001 0101 ,已有偶数个1,则偶校验位为0 异步串行传送在起始位之后传输的是数据位的最低位(95H的最低位D0=1),而且数据位的最高位(95H的最高位D7=1)传输之后传输校验位,最后是终止位。 故为 0 1 0 1 0 1 0 0 1 0 1

4,磁盘计算

①计算磁盘容量

②根据转速计算 数据传输率=每条磁道的容量/旋转一圈的时间

数据传输率=位密度 X 线速度,

又因为线速度=周长 X 转速 ,

因此数据传输率=位密度 X 周长 X 转速。

又位密度 X 周长=每个磁道的总位数,

因此数据传输率=每个磁道的总位数 X 转速。

例:每条磁道有12个扇区,每个扇区512B,磁盘机以7200rpm速度旋转

解: 磁道容量:12×512B 数据传输率:12×512B×(7200rpm/60s)=737280Bps

例:磁盘组有6片磁盘,最外两侧盘面可以记录,存储区域内径22cm,外径33cm,道密度为40道/cm,内层密度为400位/cm,转速3600转/分。

(1)共有多少存储面可用?

(2)共有多少柱面?

(3)盘组总存储容量是多少?

(4)数据传输率是多少?

解:

(1)共有:6×2 = 12个存储面可用;

(2)有效存储区域 =(33-22)/2= 5.5cm

柱面数 = 40道/cm × 5.5cm= 220道

(3)内层道周长=22*Π(圆周率)cm= 69.08cm

道容量=400位/cm×69.08cm= 3454B

面容量=3454B×220道 = 759 880B

盘组总容量 =759,880B×12面= 9,118,560B

(4)转速 = 3600转 / 60秒 = 60转/秒

数据传输率 = 3454B × 60转/秒= 207,240 B/S

注意:

1)Π(圆周率)的精度选取不同将引起答案不同,一般取两位小数;

2)柱面数 盘组总磁道数(=一个盘面上的磁道数)

3)数据传输率与盘面数无关;

4)数据传输率的单位时间是秒,不是分。

5,中断屏蔽字

①根据题目要求写出各个程序的中断屏蔽字并画图

注意:题目中1,0分别代表什么,

是1代表中断屏蔽,0代表中断开放;←书上是这种

还是1代表中断开放,0代表中断屏蔽。←出题有可能是这种

仔细审题!!!

中断屏蔽技术主要用于多重中断。

对应每一个中断请求触发器就有一个屏蔽触发器,将所有的屏蔽触发器组合在一起,就成了一个屏蔽寄存器,屏蔽寄存器中的内容称为屏蔽字。

屏蔽技术可改变优先等级 严格地说,优先级包含响应优先级和处理优先级。响应优先级是指CPU响应各中断源请求的优先次序,这种次序往往是硬件线路已设置好的,不便于改动。处理优先级是指CPU实际对各中断源请求的处理优先次序。如果不采用屏蔽技术,响应的优先次序就是处理的优先次序。

例如,有A、B、C、D,4个中断源,其优先级按A→B→C→D 由高向低次序排列。

在CPU执行主程序期间,同时出现了B和C的中断请求,由于B级别高于C,故首先执行B的服务程序。

当B级中断服务程序执行完返回主程序后,由于C请求未撤销,故CPU又再去执行C级的中断服务程序。

若此时又出现了D请求,因为D级别低于C,故CPU不响应, 当C级中断服务程序执行完返回主程序后再去执行D级的服务程序。

若此时又出现了A请求,因A级别高于D,故CPU暂停对D级中断服务程序的执行,转去执行A级中断服务程序,等A级中断服务程序执行完后,再去执行D级中断服务程序。

上述的中断处理示意图如图所示。

例:设某机有五个中断源L0、L1、L2、 L3、L4,按中断响应的优先次序由高向低排序为L0→L1 →L2 →L3 →L4,现要求中断处理次序改为L1→L4 →L2 →L0 →L3,根据下面的格式,写出各中断源的屏蔽字。

解:各中断源屏蔽状态见下表:

中 断 源

屏 蔽 字

0 1 2 3 4

L0

L1

L2

L3

L4

1 0 0 1 0

1 1 1 1 1

1 0 1 1 0

0 0 0 1 0

1 0 1 1 1

表中:设屏蔽位=1表示屏蔽,屏蔽位=0表示中断开放。

为了使所有中断都能得到及时响应,现行程序的中断屏蔽字一般设为全开放(全0)状态。

讨论:按照修改过的优先次序,当五个中断请求信号同时到来时,CPU中断处理过程如下图: 图中括号内为各程序的屏蔽码。

注意:中断屏蔽码的判优作用体现在对低级中断请求的屏蔽上,对于多个同时到来的高级中断请求信号之间则只有开放作用,没有判优作用。此时还需依赖硬件排队线路完成进一步的判优。

中断处理过程示意图(画法二:时空图表示)

例 设某机有4个中断源1,2,3,4,其硬件排队优先次序按1→2→3→4降序排列,各中断源的服务程序中所对应的屏蔽字如表所示。

中断源

屏蔽字

1

2

3

4

1

1

1

0

1

2

0

1

0

0

3

1

1

1

1

4

0

1

0

1

(1)给出上述4个中断源的中断处理次序。

(2)若4个中断源同时有中断请求,画出 CPU执行程序的轨迹。

解: (1)根据表,4个中断源的处理次序是按3→1→4→2降序排列。

(2)当4个中断源同时有中断请求时,由于硬件排队的优先次序是1→2→3→4,故CPU先响应1的请求,执行1的服务程序。

由于在该服务程序中设置了屏蔽字1101,故开中断指令后转去执行3的服务程序,且3的服务程序执行结束后又回到1的服务程序。

1的服务程序结束后,CPU还有2,4两个中断源请求未响应。

由于2的响应优先级高于4,故CPU先响应2的请求,执行2的服务程序。

在2的服务程序中由于设置了屏蔽字0100,意味着1,3,4可中断2的服务程序。

而1、3的请求已处理结束,因此在开中断指令之后转去执行4的服务程序,4的服务程序执行结束后又回到2的服务程序的断点处,继续执行2的服务程序,直至该程序执行结束。

下图示意了CPU执行程序的轨迹。

四、大题

1,补码一位乘

校正法(需考虑乘数正负)

例:已知[x ]补= 1.0101,[y]补=0.1101,求[x · y]补。

解;因为乘数y >0,所以按原码一位乘的算法运算,只是在相加和移位时按补码规则进行,如表所示。考虑到运算时可能出现绝对值大于1的情况(但此刻并不是溢出),故部分积和被乘数取双符号位。

部分积

乘数

说明

00.0000

+ 11.0101

1101

初值[z0]补=0

y4=1,+[x]补

11.0101

11.1010

11.1101

+ 11.0101

1110

0111

→1位,得[z1]补,乘数同时→1位

y3=0,→1位,得[z2]补,乘数同时→1位

y2=1,+[x]补

11.0010

11.1001

+ 11.0101

01

0011

→1位,得[z3]补,乘数同时→1位

y1=1,+[x]补

10.1110

11.0111

001

0001

→1位,得[z4]补

故 乘积[x×y]补=1.0111 0001

例:已知[x]补 =0.1101,[y]补 = 1.0101,求[x· y]补

解;因为乘数y <0,故先不考虑符号位,按原码相乘,最后再加上[ -x]补

部分积

乘数

说明

00.0000

+ 11.1101

0101

初值[z0]补=0

y4=1,+[x]补

00.1101

00.0110

00.0011

+ 00.1101

1010

0101

→1位,得[z1]补,乘数同时→1位

y3=0,→1位,得[z2]补,乘数同时→1位

y2=1,+[x]补

01.0000

00.1000

00.0100

+ 11.0011

01

0010

0001

→1位,得[z3]补,乘数同时→1位

y1=0,→1位,得[z4]补

+[-x]补进行校正

11.0111

0001

得最后结果[xy]补

故 乘积[x×y]补=1.0111 0001

由以上两例可见,乘积的符号位在运算过程中自然形成,这是补码乘法和原码乘法的重要区别。 上述校正法与乘数的符号有关,虽然可将乘数和被乘数互换,使乘数保持正,不必校正,但当两数均为负时必须校正。

总之,实现校正法的控制线路比较复杂。若不考虑操作数符号,用统一的规则进行运算,就可采用比较法。

Booth算法

例已知[x]补=0.1101,[y]补 =0. 1011 ,求[x×y]补。

解:[-x]补=1.0011

部分积

乘数yn

附加位yn+1

说明

00.0000

+ 11.0011

01011

0

初值[z0]补=0

ynyn+1=10,部分积+[-x]补

11.0011

11.1001

11.1100

+ 00.1101

10101

11010

1

1

→1位,得[z1]补

ynyn+1=11,→1位,得[z2]补

ynyn+1=01,部分积+[x]补

00.1001

00.0100

+ 11.0011

11

11101

0

→1位,得[z3]补

ynyn+1=10,部分积+[-x]补

11.0111

11.1011

+ 00.1101

111

11110

1

→1位,得[z4]补

ynyn+1=01,部分积+[x]补

00.1000

1111

最后一步不移位,得[xy]补

故 乘积[x×y]补=0.1000 1111

2,微指令

①根据题目要求写出具体格式

②根据上一问的下地址位数计算容量大小

微指令格式与微指令的编码方式有关,通常分为水平型微指令和垂直型微指令两种。

1.水平型微指令 水平型微指令的特点是一次能定义并执行多个并行操作的微命令。从编码方式看,直接编码、字段直接编码、字段间接编码以及直接和字段混合编码都属于水平型微指令。其中,直接编码速度最快,字段编码要经过译码,故速度受影响。

2.垂直型微指令 垂直型微指令的特点是采用类似机器指令操作码的方式,在微指令字中,设置微操作码字段,由微操作码规定微指令的功能。通常一条微指令有1 ~2个微命令,控制1~2种操作。这种微指令不强调其并行控制功能。

两种微指令格式的比较

①水平型微指令比垂直型微指令并行操作能力强.效率高,灵活性强。

②水平型微指令执行一条机器指令所需的微指令数目少,因此速度比垂直型微指令的速度快。 ③ 水平型微指令用较短的微程序结构换取较长的微指令结构,垂直型微指令正相反,它以较长的微程序结构换取较短的微指令结构。

④水平型微指令与机器指令差别较大,垂直型微指令与机器指令相似。

例 某微程序控制器中,采用水平型直接控制(编码)方式的微指令格式,后续微指令地址由微指令的下地址字段给出。已知机器共有28个微命令,6个互斥的可判定的外部条件,控制存储器的容量为512×40位。试设计其微指令格式,并说明理由。

解:水平型微指令由操作控制字段、判别测试字段和下地址字段三部分构成。因为微指令采用直接控制(编码)方式,所以其操作控制字段的位数等于微命令数,为28位。又由于后续微指令地址由下地址字段给出,故其下地址字段的位数可根据控制存储器的容量(512×40位)定为9位。当微程序出现分支时,后续微指令地址的形成取决于状态条件,6个互斥的可判定外部条件,可以编码成3位状态位。非分支时的后续微指令地址由微指令的下地址字段直接给出。微指令的格式如图所示。

操作控制28位

判断3位

下地址9位

例 某机共有52个微操作控制信号,构成5个相斥类的微命令组,各组分别包含5、8、2、15、22个微命令。已知可判定的外部条件有两个,微指令字长28位。

(1)按水平型微指令格式设计微指令,要求微指令的下地址字段直接给出后续微指令地址。 (2)指出控制存储器的容量。

解:(1)根据5个相斥类的微命令组,各组分别包含5、8、2、15、22个微命令,考虑到每组必须增加一种不发命令的情况,条件测试字段应包含一种不转移的情况,则5个控制字段分别需给出6、9、3、16、23种状态,对应3、4、2、4、5位(共18位),条件测试字段取2位。根据微指令字长为28位,则下地址字段取28-18-2 =8位,其微指令格式如图所示。

5个微命令

3位

8个微命令

4位

2个微命令

2位

15个微命令

4位

22个微命令

5位

2个判定条件

2位

下地址

8位

(2)下地址为8位,微指令字长为28位

故控制存储器的容量为2的8次方×28位

3,存储器扩展

①写出选用芯片数量及其地址范围

②画出具体连接图

实际存储器往往需要字数和位数同时扩充。一个存储器的容量为M×N位,若使用L×K位存储器芯片,那么,这个存储器共需要(M÷L)×(N÷K)个存储器芯片。

存储器扩展这个视频讲解的很清晰,三道题都过一遍 ,再自己做几道题应该就没问题了:

最后,b站上还有一个八道大题的讲解:

新增内容

暂时先完结了,想到什么会再补充的。

然后就再也没补充过了,假期拾起来

假期快结束了,也没拾起来

9617

9617

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?