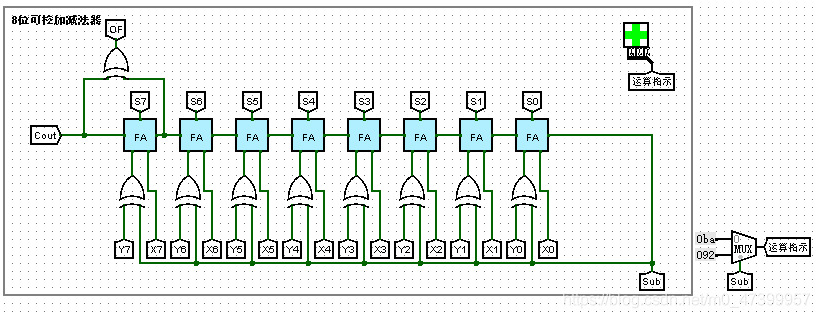

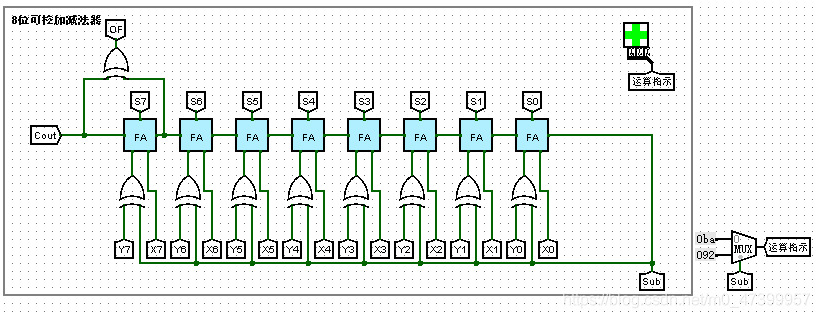

8位可控加减法电路设计

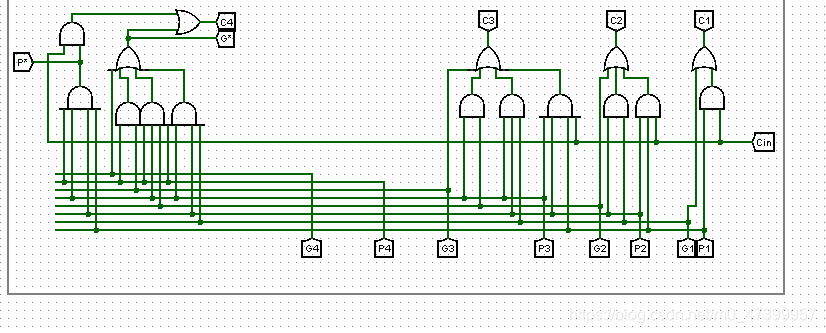

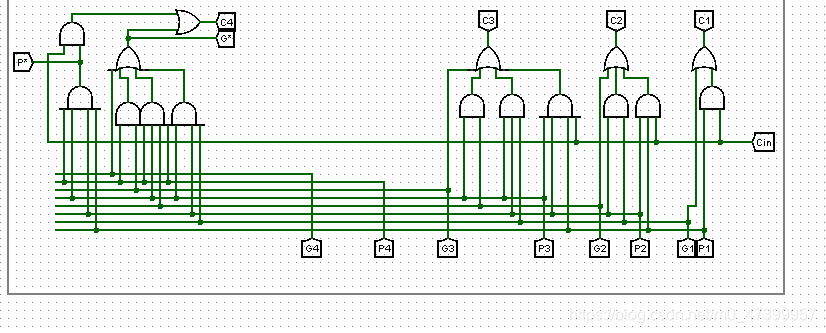

CLA182四位先行进位电路设计

CLA182四位先行进位电路设计

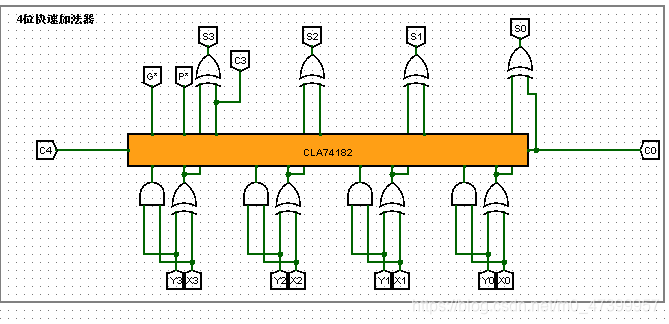

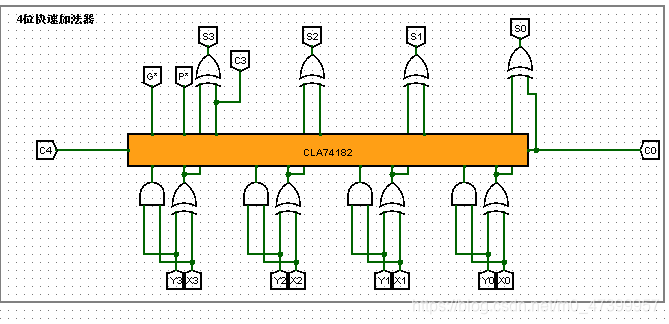

4位快速加法器设计

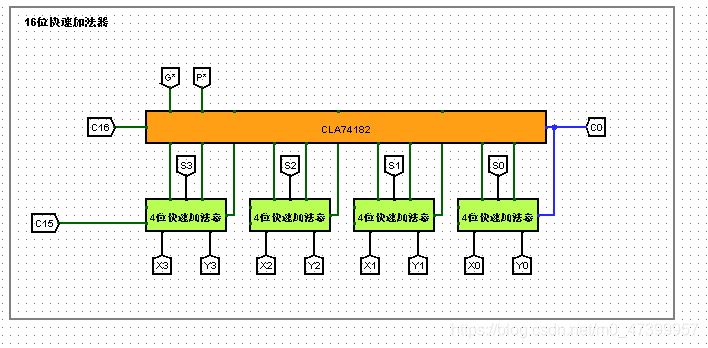

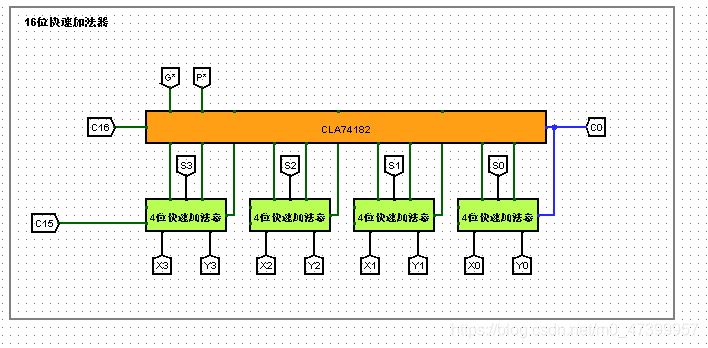

16位快速加法器设计

16位快速加法器设计

32位

logisim运算器设计逻辑图

最新推荐文章于 2024-05-21 10:00:41 发布

8位可控加减法电路设计

CLA182四位先行进位电路设计

CLA182四位先行进位电路设计

4位快速加法器设计

16位快速加法器设计

16位快速加法器设计

32位

4455

4455

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?