原码一位乘

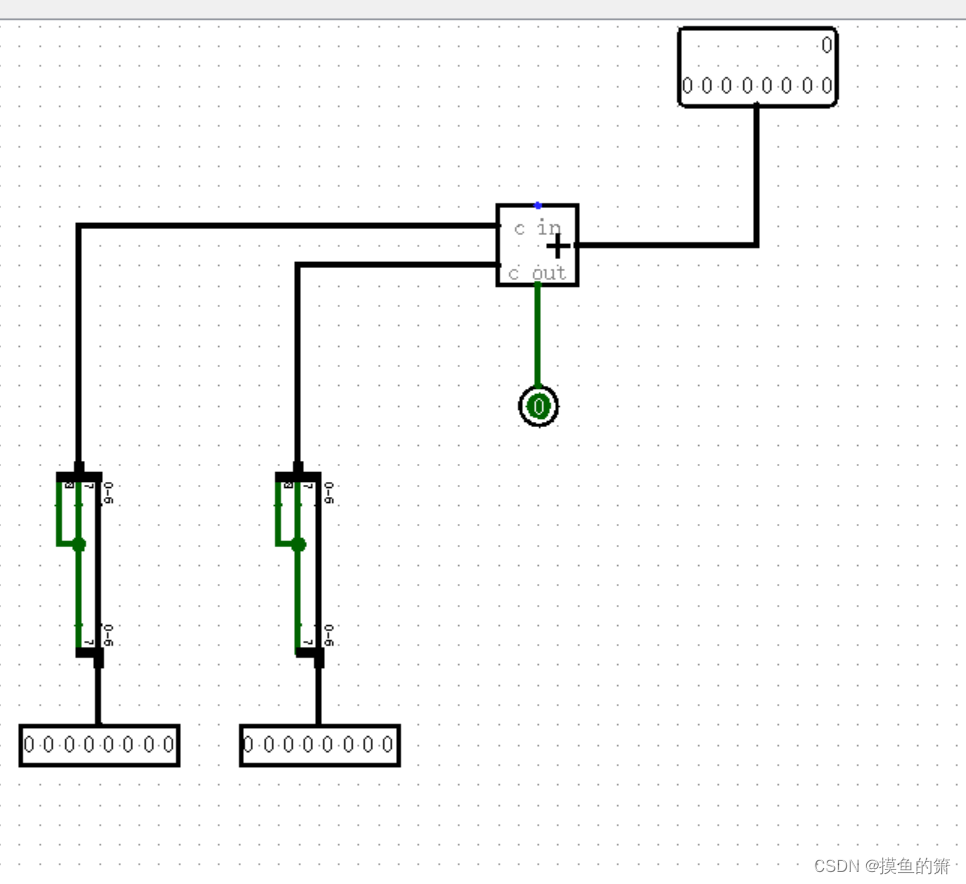

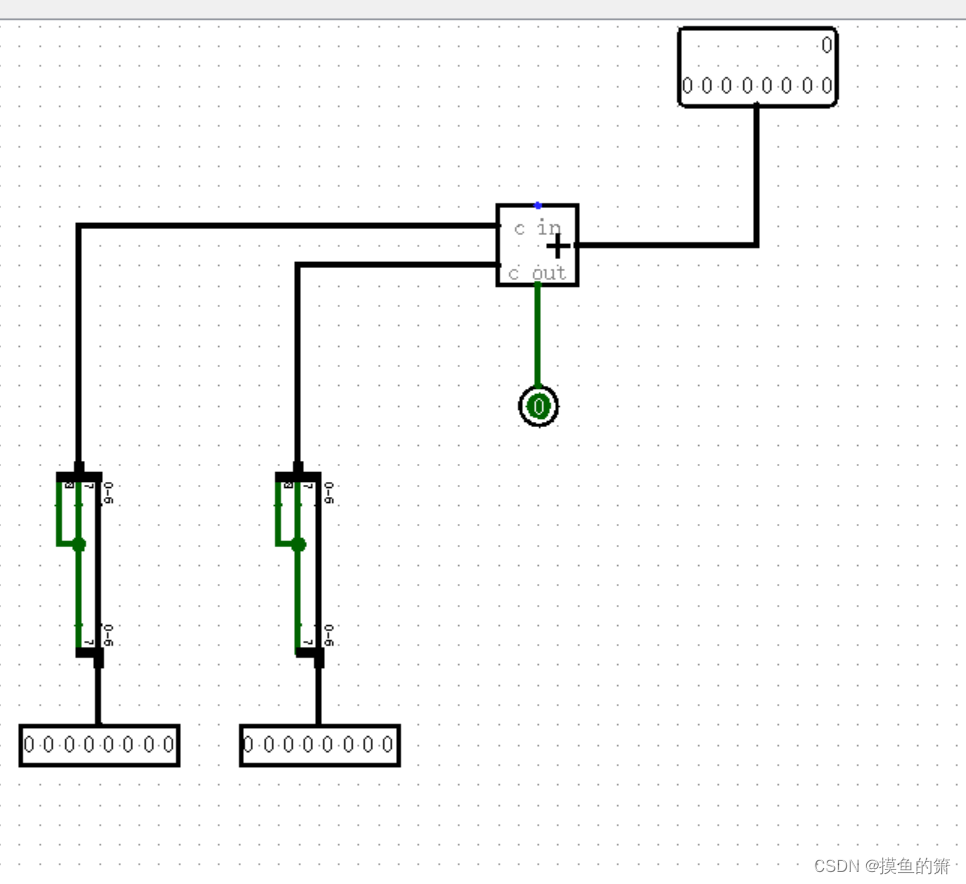

演示部分:

FA-8

Control

Shift-R

补码一位乘

分为main、选择器、加法器、右移1、右移2这几个文件

main:

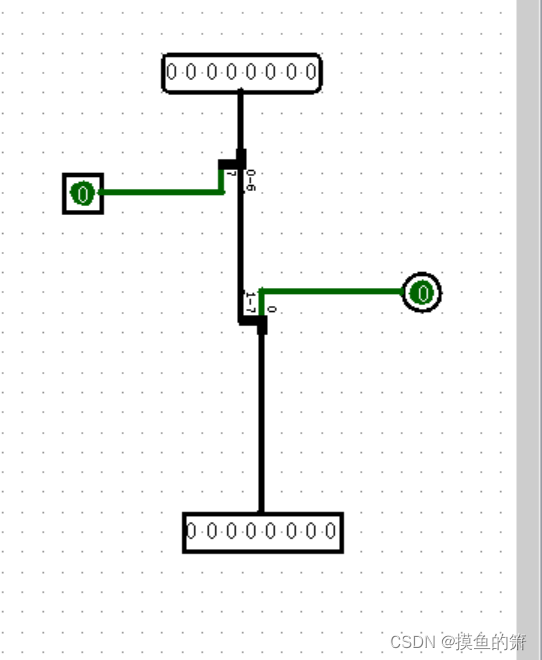

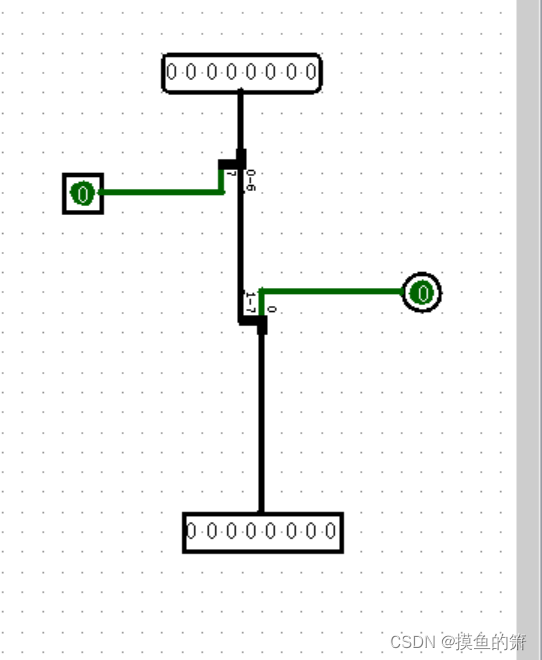

细节部分:

选择器:

加法器:

右移1

右移2:

演示部分:

FA-8

Control

Shift-R

分为main、选择器、加法器、右移1、右移2这几个文件

main:

细节部分:

选择器:

加法器:

右移1

右移2:

2404

2404

3516

3516

8685

8685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?