1 SerDes

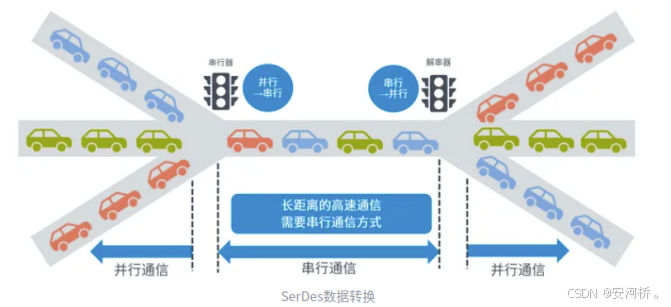

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。 它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,提升信号的传输速度,从而大大降低通信成本。

视频传输方式为:LVDS(低压差分信号传输)

1.1 差分信号:传统的信号传输是通过单一的信号线传输数据。而LVDS使用差分信号传输,即同时传输两个信号,分别为正向信号(P)和反向信号(N)。这两个信号的电压相反,当P信号上升时,N信号下降,从而形成一个差分信号。

1.2 高速传输:LVDS将信号传输速率提高到了几百兆赫兹(MHz)的级别,因此适用于高速数据传输。高速传输主要得益于差分信号的特性,差分信号具有抗干扰能力强、传输距离远等优点。

1.3 低电压:LVDS采用低电压传输,通常为1.2伏特(V)。低电压传输可以减少功耗,同时也减少了电磁辐射和干扰。

1.4 带宽:LVDS传输具有较大的带宽,通常可以达到几百兆赫兹(MHz)的级别。较大的带宽使LVDS适用于高分辨率图像、视频和音频等高带宽应用

目前加解串器主要是有两家

这里我们只介绍美信的,TI的FPDLINK回头再总结。

2 美信的加解串器用到的一些概念

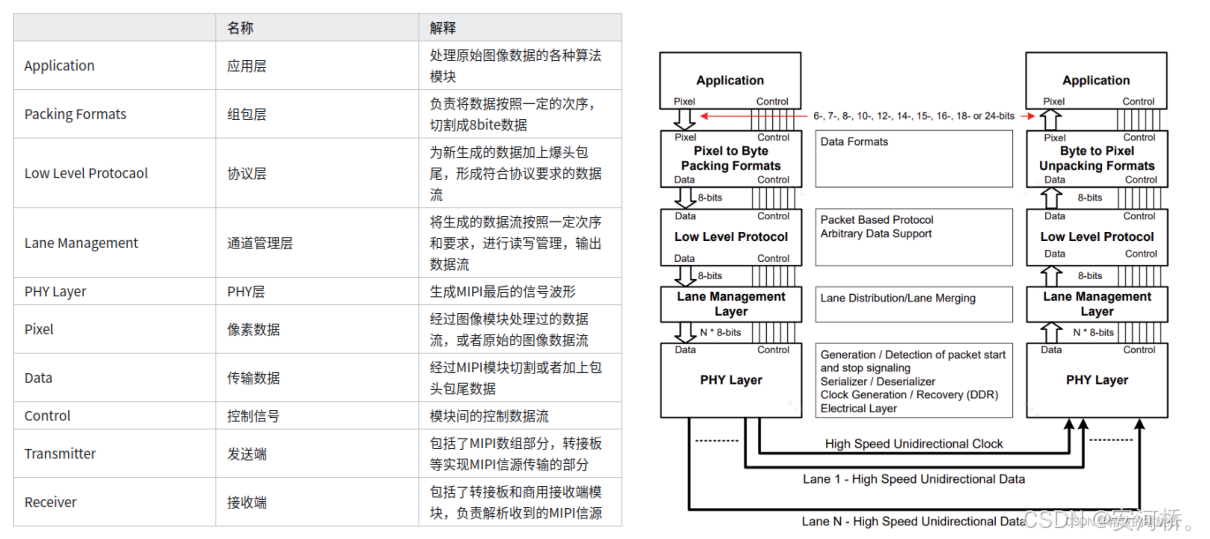

2.1 MIPI CSI

MIPI CSI2的分层分别为:应用层、协议层、物理层。

协议层再分为三层:像素/字节组包/解包层、底层协议层、通道管理层

2.2 Port(端口)

2.2.1 Port的定义

在美信加解串器的架构中,端口(Port)是一个物理接口,用于连接外部不同的设备或模块(sensor或者SOC)。它是数据流入和流出的通道接口。

2.2.2 Port的功能

(1)数据通道的端点:PORT端口作为数据传输路径的起始点或终止点。在从传感器到 SoC 的通路中,有输入端口接收来自传感器的原始数据,还有输出端口将处理后的数据发送给 SoC 或其他外部设备。不同类型的端口可以支持不同的数据格式、速率和协议。例如,有的端口用于传输图像数据,可能是并行数据端口;有的端口用于传输时钟信号,以保证数据传输的同步性。

(2)连接功能:端口提供了物理连接的位置。例如,在连接图像传感器(Sensor)和加串器时,传感器的数据输出端口会连接到加串器的输入端口,从而建立起数据传输的物理链路。

2.3 Link(链路)

2.3.1 Link的定义

Link 是指在两个设备(加解串器)之间建立的用于数据传输的逻辑连接。它可以由一条或多条物理通道(如 lane)组成,是数据传输的逻辑路径。

2.3.2 Link的功能:

(1)数据传输路径规划:在系统中规划出数据从一个设备传输到另一个设备的路线。例如,从加串器到解串器之间会建立一条链路,用于传输经过加串处理后的串行数据。这条链路可能会跨越不同的物理介质和芯片引脚,它定义了数据传输的方向和大致范围。

(2)逻辑抽象层:Link 是一种逻辑抽象,它隐藏了物理通道(lane)的细节。链路(Link)由多个 lane 组成,上层应用或系统设计人员在考虑数据传输时,通常可以将链路视为一个整体的传输通道,而不必过于关注每个 lane 的具体情况。不过,链路的性能(如带宽、传输速率等)是由组成它的 lane 共同决定的。

2.3.3 Link与Port的关系,Link与Lane的关系

Port与Link是N对N的关系,Link与Lane是1对N的关系

举例说明:假设 Port A 是一个多功能的数据输入端口,它可以接收来自不同数据源的信号,这些数据源的数据传输要求可能不同,因此可以通过配置不同的 Link(如 Link A 用于高速数据传输,Link B 用于低速控制信号传输)与 Port A 相连,以满足多种数据传输需求。同样,多个 Port(如 Port A 和 Port B)也可以连接到同一个 Link 上,用于数据的汇聚或分发,比如将 Port A 和 Port B 接收的数据合并到 Link A 上进行传输。

功能独立性:加解串器的 Port(端口)和 Link(链路)有不同的功能定义。Port 主要是物理接口,用于连接外部设备,如传感器、SoC 等;而 Link 是用于数据传输的逻辑连接,它可以由一条或多条物理通道(如 lane)组成。从功能角度看,一个 Port 可以支持多个 Link,或者多个 Port 可以共享一个 Link。在某些特定设计或简单应用场景下可能一一对应:在一些简单的系统或者为了简化设计和管理,会将 Port 和 Link 设计成一一对应关系。例如,在一个小型的视频监控系统中,Port A 专门用于接收摄像头的视频数据,通过 Link A 将数据传输到解串器进行处理,这种一一对应可以使系统架构更加清晰,便于理解和维护。

Sensor---PHY---Lane---PHY---Serializer--------------Link(lanes)--------------Deserializer---PHY---Lane---PHY---Soc

2.4 Lane(通道)

2.4.1 Lane的定义

Lane 是数据传输的物理通道,通常是指可以独立传输数据的线路或通路。在串行数据传输中,多个 lane 可以并行工作以增加数据传输的带宽。

Lane 是指信号传输路径中的一个单独的信道。在多通道通信中,一个通信链路Link可能由多个 lane 组成,每个 lane 可以传输一部分的数据。例如,在高速传输协议中,一个 lane 是独立的数据传输通道,它负责传输一定带宽的数据。多个 lane 可以并行工作,从而增加总的带宽。

2.4.2 Lane的功能

(1)数据传输实体通道:Lane 就像是高速公路上的车道,数据就像车辆在这些车道上行驶。每个 lane 都有自己的物理线路,可以独立地传输数据。例如,在高速串行数据传输中,数据可以通过一个或多个 lane 从加串器传输到解串器。在并行传输的情况下,多个 lane 可以同时传输不同的数据位,从而提高传输速率。

(2)带宽扩展单元:通过增加 lane 的数量,可以扩展系统的数据传输带宽。例如,如果一个 lane 的带宽为 1Gbps,那么使用 4 个 lane 并行传输数据时,系统的总带宽就可以达到 4Gbps。而且,不同的 lane 可以根据需要采用不同的传输速率或工作模式,以满足多样化的数据传输需求。

2.5 Phy(物理层)

2.5.1 Phy的定义

Phy 是物理层的简称,它主要负责处理物理介质上的信号传输和接收。包括信号的生成、调制、解调、放大、滤波、时钟恢复等物理层相关的操作。

2.5.2 Phy的功能

(1)信号处理:在发送端,Phy 将数字信号转换为适合在物理介质上传输的模拟信号。例如,它会对要发送的数据进行调制,将数字信号加载到高频载波信号上,以便通过电缆等物理介质进行远距离传输。在接收端,Phy 则进行相反的操作,将接收到的模拟信号解调为数字信号,并进行放大、滤波等操作,以去除噪声和干扰,恢复出原始的数据信号。

(2)物理层适配:Phy 还需要适配不同的物理介质和传输标准。例如,对于不同类型的传输电缆(如双绞线、同轴电缆等),Phy 会调整信号的参数(如电压、电流、频率等),以确保信号能够在这些介质上有效地传输。同时,它也会遵循相应的物理层传输协议,如高速串行通信协议中的信号电平标准、时钟恢复机制等。

在配置链路的时候,常常还要通过解串器使能phy的始终以及配置phy的速率。

2.5.3 Lane与PHY的关系

lane 是用于数据传输的物理通道,而 PHY 是负责物理信号传输的硬件层,lane 是通过 PHY 层传输数据的。一个是协议层一个是物理层,还是很好理解的。

Phy 和 Lane 不是一一对应的关系

在一些简单的系统设计中,可能会出现一个 Phy 对应一个 Lane 的情况,但这不是普遍规则。在更复杂的高速数据传输架构中,一个 Phy 可以管理多个 Lane。例如,在一个多 - Lane 的高速串行通信系统中,一个 Phy 可以同时协调和处理 4 个或更多的 Lane。Phy 负责这些 Lane 的物理层信号处理,包括为多个 Lane 提供统一的时钟信号或者进行时钟恢复管理。它还会对通过多个 Lane 的数据流量进行控制和调度,根据每个 Lane 的带宽利用率、数据优先级等因素,合理地分配数据传输任务。

Phy 为 Lane 提供物理层的支持和信号处理功能。它处理 Lane 中的物理信号,包括信号的编码、解码、时钟恢复、均衡等操作。从物理连接角度看,Lane 通常需要通过 Phy 与其他组件进行连接。Phy 作为物理层接口,将 Lane 传输的数据信号转换为适合在物理介质(如电缆、光纤等)上传输的形式,并确保信号在物理介质上有效地传播,减少信号的衰减、失真和干扰。

2.6 Virtual Channel(虚拟通道)

2.6.1 Virtual Channel 的概念

Virtual Channel 是 lane 上的虚拟通道,它用于在同一个物理传输通道(例如,一个 MIPI CSI 或 DSI lane)上实现 多路复用。虚拟通道允许在同一条物理链路(lane)上传输多个独立的数据流(例如,视频、控制信息等),而不需要额外的物理传输路径。在高速串行通信协议中(如 MIPI CSI、MIPI DSI 等),数据传输通常通过多个 lane 来进行,每个 lane 是独立的物理传输通道。

Virtual Channel 是在每个物理 lane 上的逻辑分隔通道,用来区分和组织不同的数据流。通过虚拟通道,一个物理 lane 可以承载多个不同类型的传输数据流,而不需要额外的物理通道或线路。

例如,在 MIPI CSI 或 MIPI DSI 中,多个 Virtual Channel 可以在同一物理链路上复用传输不同的数据类型,如:VC0 传输视频数据流,VC1 传输控制数据或同步信息

2.6.2 Virtual Channel 在 MIPI CSI 和 MIPI DSI 中的应用

MIPI CSI-2 和 MIPI DSI-2 都支持 Virtual Channel 的概念。每个物理 lane 可以携带多个 Virtual Channel,使得多个数据流(如视频数据流、控制数据流等)能够共享同一条物理链路。每个虚拟通道都会有一个独立的标识符,用于标明数据流的类型和用途。

-

MIPI CSI-2:图像传感器和 SoC 之间传输时,多个 Virtual Channel 可以在同一

lane上并行传输不同类型的数据(如图像数据、时序信息、控制命令等)。 -

MIPI DSI-2:显示器和 SoC 之间的数据传输,虚拟通道用于在同一物理

lane上复用不同的数据流(例如,主显示数据和辅助数据流)。

2.6.3 虚拟通道的优势

(1)带宽优化:通过复用同一个 lane,虚拟通道使得同一条物理链路能够高效地传输多个独立的数据流,提高了带宽的利用率。

(2)减少物理链路数量:在多个不同的数据流之间共享相同的物理 lane,减少了硬件接口的数量,降低了成本和复杂性。

(3)灵活的数据流管理:虚拟通道提供了对不同类型数据流的逻辑隔离,使得在同一个物理链路上能够传输不同的应用数据,简化了数据管理。

2.6.4 总结

(1)Virtual Channel 是在 lane 上实现多路复用的机制,使得多个独立的数据流能够共享同一条物理传输路径。

(2)在协议如 MIPI CSI-2 和 MIPI DSI-2 中,虚拟通道通过不同的通道编号来区分数据流,并通过同一物理 lane 传输。

(3)这种机制帮助提高了带宽的利用率,同时减少了所需的物理链路数量,提升了系统的灵活性和性能。

因此,Virtual Channel 是基于 lane 上的虚拟化技术,能够在有限的物理链路上支持多个数据流并行传输。

3 从Serializer到SOC的分析

从 deserializer 到 SoC 的数据传输通常是 并行的视频信号,并且使用的是 MIPI CSI 接口。

当从 serializer 转换到 deserializer,并且数据传输至 SoC 时,以下是常见的步骤:

3.1 Serializer-Deserializer

在数据到达 SoC 之前,首先经过 deserializer。这个设备的作用是将串行数据流(通常是由 serializer 转换的)转换回并行数据流。通过串行到并行转换,解码的图像数据为并行数据可以传递给 SoC 进行进一步处理。

3.2 Deserializer-Soc

转换后的数据是并行的,这意味着图像的每个像素的值(比如 RGB 或 YUV 格式)会通过多个数据线同时传输到 SoC。如果你使用的是 MIPI CSI 接口,通常会有多个并行的 lane 传输数据。一旦 SoC 接收到并行的数据,它通常会在多个并行信号线上接收图像的每个像素信息。SoC 中的接口(如 MIPI CSI 接口、Parallel Bus 等)会接收这些并行信号并进行进一步处理。

SoC 内部通常会有一个接收模块(例如,MIPI D-PHY 或其它接口的接收器)来接收这些并行数据流并将它们传递给处理单元,如图像处理单元(ISP)或其他硬件加速单元。

3.3 Lane在传输过程中存在的地方

在数据传输中,lane 通常存在于 serializer 和 deserializer 之间,而不是 deserializer 和 SoC 之间。

3.3.1 Serializer 和 Deserializer 之间的 Lane

Serializer 将并行的数据流(通常来自图像传感器)转换为 串行数据流,为了提高带宽,这个串行数据流是通过多个 lane 进行并行传输的。在这个阶段,多个 lane 用于承载不同部分的图像数据。例如,假设图像传感器输出的是 8 位宽的数据,serializer 会将这些并行的 8 位数据按一定的规则转换为串行数据,并通过多个 lane(如 1、2、4 或 8 条 lane)同时传输。

MIPI CSI 是一个常见的协议,它使用多个 lane 来并行传输数据,这些 lane 是物理传输通道,每个 lane 传输一部分数据。

因此,serializer 和 deserializer 之间,数据通过多个 lane 来实现高带宽传输。

3.3.2 Deserializer 和 SoC 之间的 Lane

在 Deserializer 端,串行数据流会被恢复为并行数据流。Deserializer 的作用是将这些通过多个 lane 串行传输的数据重新合并成并行的格式,供 SoC 进一步处理。

由于 SoC 通常不再需要串行到并行的转换,它接收的是并行的数据流。SoC 直接从 deserializer 获取并行数据,通常使用类似 MIPI CSI 接口 或 Parallel Bus 进行传输。这个过程一般不再涉及 lane。

对于不同的 Lane 数量,解串器将会输出不同位宽的并行数据流。若是4 条 Lane:每条 Lane传输 1 位数据,Lane 数量4 条,4 条 Lane 的 1 位数据合并成 4 位并行数据。

如果解串器的输出接口支持 8 位数据,它可能会将这些 4 位并行数据与其他数据进行填充或按需求补充,从而输出一个 8 位并行数据(字节流)。这意味着,虽然每个 Lane 只传输 1 位数据,但最终的传输数据宽度可能是 8 位 或更高。

所以,在 deserializer 和 SoC 之间,数据传输是并行的,通常通过数据总线或并行接口来传递,而不涉及多个 lane 的概念。

3.3.3 总结

Serializer 和 Deserializer 之间,多个 lane 用于并行传输数据。这是因为串行数据流是通过多个物理通道并行传输的,能够提供更高的带宽。

Deserializer 和 SoC 之间,数据已经是并行的。数据通过并行总线传输给 SoC,通常不再使用 lane 的概念。

所以,lane 存在于 serializer 和 deserializer 之间,用于并行化串行传输的数据,而在 deserializer 和 SoC 之间,数据通常已经是并行的,不再依赖于多个 lane。

4 配置流程的总结

| 配置项 | 说明 | 配置顺序 |

|---|---|---|

| 1. 电源和时钟初始化 | 确保电源稳定,初始化时钟系统 | 首先进行 |

| 2. PHY 配置 | 配置 PHY 工作模式(串行、数据速率、lane 数量) | 在 PHY 配置时进行 |

| 3. Lane 数量配置 | 设置所需的物理传输通道数量 | 紧接着 PHY 配置 |

| 4. 链路数据速率配置 | 配置链路的数据速率,匹配 lane 数量 | 与 lane 配置同步 |

| 5. 虚拟通道配置 | 配置虚拟通道,用于复用不同类型的数据流 | 在 lane 配置之后 |

| 6. 数据类型配置 | 配置数据格式(例如,RGB、YUV 等图像格式) | 在虚拟通道配置后 |

| 7. 映射配置 | 配置数据流的映射,确保正确的数据传输 | 数据类型配置后 |

| 8. PHY 输出频率配置 | 配置 PHY 的输出频率,确保与链路速率和 lane 数量一致 | 映射配置后 |

| 9. 启动数据传输 | 启动数据传输,确保数据正确传输到 SoC | 所有配置完成后 |

| 10. 监控与调试 | 监控链路稳定性,确保没有传输错误或丢包 | 传输开始后 |

在此之前插入一些官方的相关的参数原理介绍

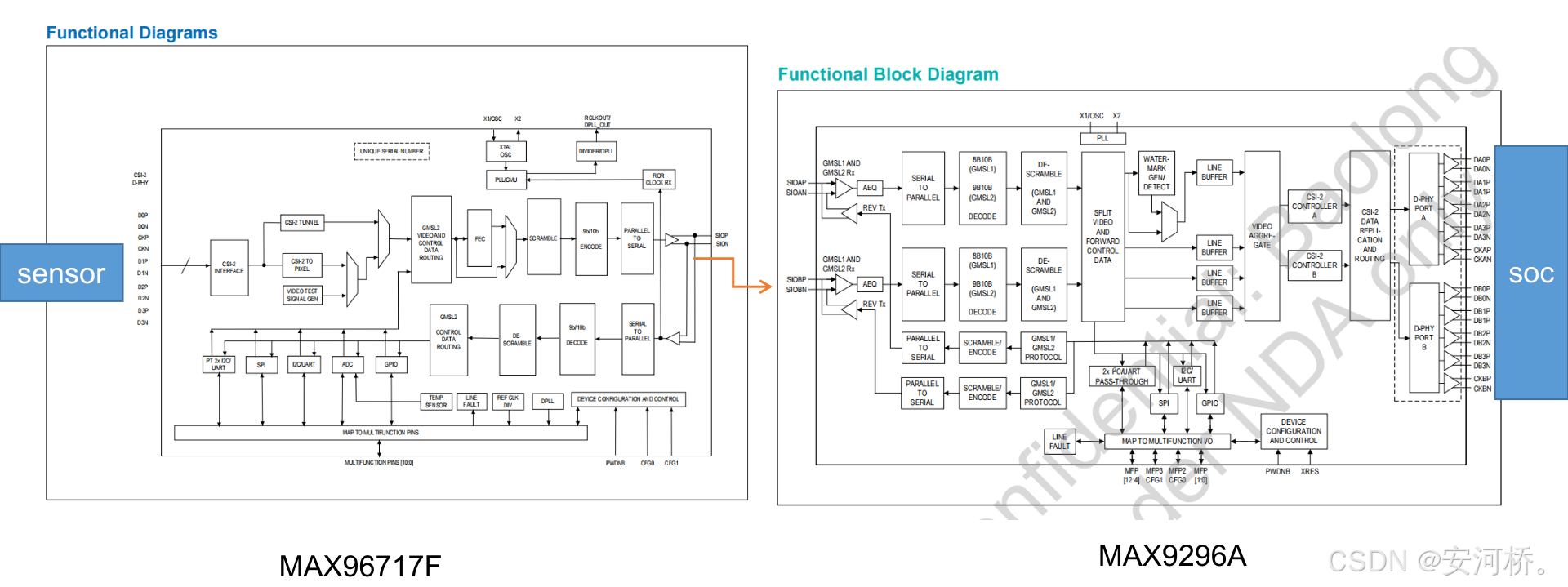

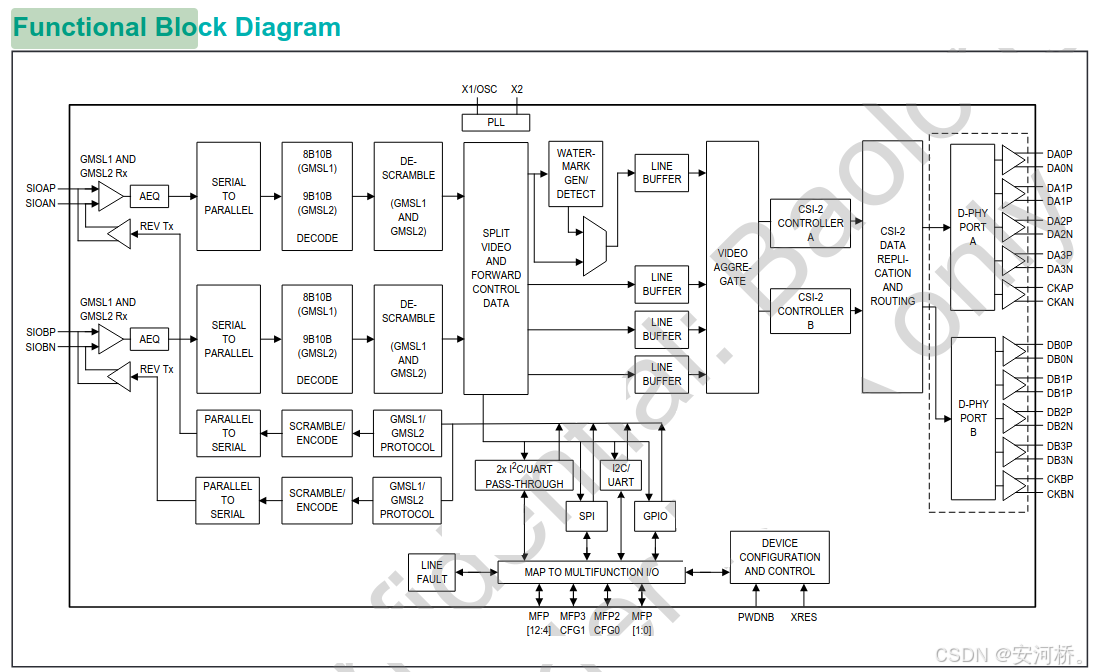

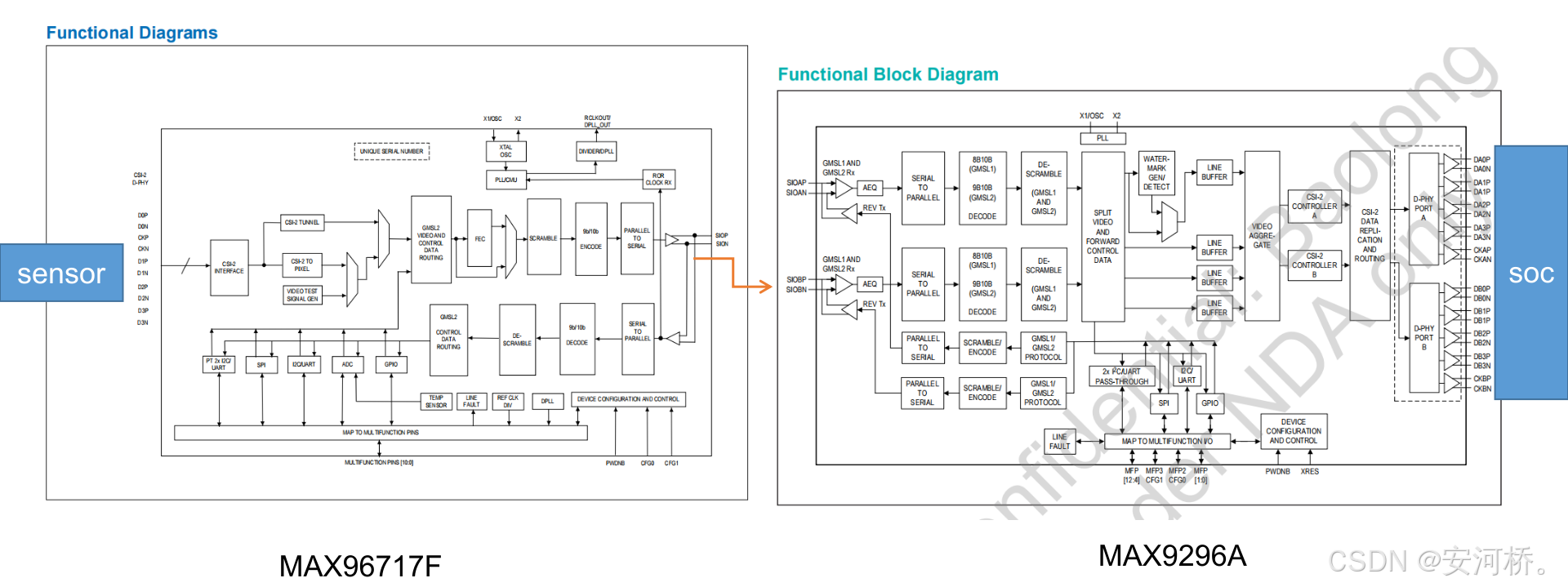

1.MAX96716:Dual GMSL2 to CSI-2 Deserializer解串器

MAX96716A/MAX96716K将双GMSL2串行输入转换为MIPI CSI-2。还可以实现前向视频和双向控制数据的全双工传输。GMSL2串行链路的正向固定速率为6Gbps或3Gbps,反向固定速率为187.5Mbps。串行输入独立操作,允许在每个输入上接收不同时序和分辨率的视频。

来自两个输入的视频数据可以在单个CSI-2端口上聚合输出,或者在第二个端口上复制以进行冗余处理。每个四车道MIPI CSI-2 D-PHY端口可以编程为操作一个,两个,三个,或四个活动数据通道。每个双通道MIPI CSI-2 C-PHY端口可以编程为与一个或两个活动数据通道操作。每个CSI-2端口支持16个虚拟通道,允许虚拟通道和数据类型重分配。

还有side-channel operates at 9.6kbps - 1Mbps in UART-UART mode \9.6kbps - 1Mbps in I2C-I2C mode with clock stretching.

特性

特性

-

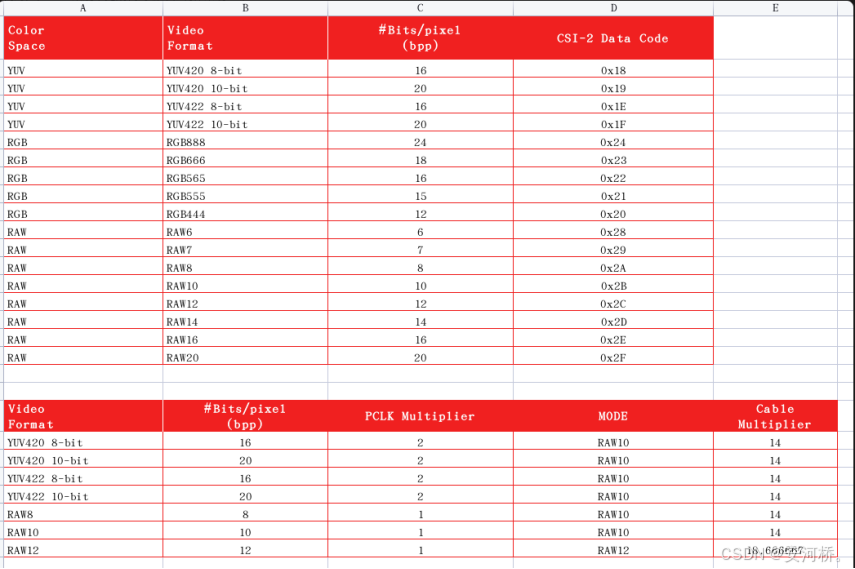

Dual Four-Lane D-PHY or Dual Two-Lane C-PHY MIPI CSI-2 v1.3 Output Ports • Aggregation and Replication Functions • Support for 16 Virtual Channels • Supports RAW8/10/12/14/16/20, RGB565/666/888,YUV422 8-/10-Bit, User-Defined, and GenericLong-Packet Data Types

2.Advanced MIPI D-PHY v1.2 Transmitters • 80Mbs - 2.5Gbps per Lane • Polarity Flip and Data-Lane Reassignment

3.Advanced MIPI C-PHY v1.0 Transmitters • 182Mbps - 4.56Gbps per Lane

4.Multiple GMSL2 Data Rates for System and PowerFlexibility • 3Gbps or 6Gbps Forward-Link Rates • 187.5Mbps Reverse-Link Rate

5.Full-Duplex Capability Over a Single Wire

6.ASIL-Relevant Functional Safety Features • ASIL-B Compliant • End-to-End Data Integrity Through CRC in TunnelMode • R-S FEC for Protection of Forward Video and Control-Channel Data • 16-Bit CRC Protection of Side-Channel Data (I2C,UART, SPI, GPIO) with Retransmission Upon Error Detection • 32-Bit CRC Protection of Video-Line Data

7.Concurrent Side-Channel for Device Configurationand Communication with Peripherals • I2C/UART, Pass-Through I2C/UART, SPI, GPIO,and Register-Programmable GPIO • Four Hardware-Programmable Device Addresses

映射D-PHY C-PHY PORTA(PORTD) PORTB(PORTE) 4LANE 2LANE

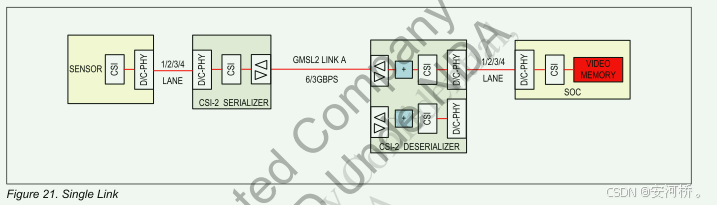

1.单Link的原理(a single sensor with a MIPI D-PHY output)

The MAX96716A/MAX96716K has dual four-lane D-PHY v1.2 output ports, which support a data rate of 80Mbps to 2.5Gbps or dual two-lane C-PHY CSI-2 v1.3 output ports, which support a data rate of 182Mbps to 4.56Gbps per lane. The number of active D-PHY v1.2 data lanes is programmable as one, two, three, or four lanes. The C-PHY interface is progammable as one or two lanes. Supported data types include RAW8/10/12/14/16/20, RGB555/666/888/YUV422 8/ 10-bit, user-defined and generic long-packet data types. Up to 16 virtual channels are also supported

The MAX96716A/MAX96716K has dual four-lane D-PHY v1.2 output ports, which support a data rate of 80Mbps to 2.5Gbps or dual two-lane C-PHY CSI-2 v1.3 output ports, which support a data rate of 182Mbps to 4.56Gbps per lane. The number of active D-PHY v1.2 data lanes is programmable as one, two, three, or four lanes. The C-PHY interface is progammable as one or two lanes. Supported data types include RAW8/10/12/14/16/20, RGB555/666/888/YUV422 8/ 10-bit, user-defined and generic long-packet data types. Up to 16 virtual channels are also supported

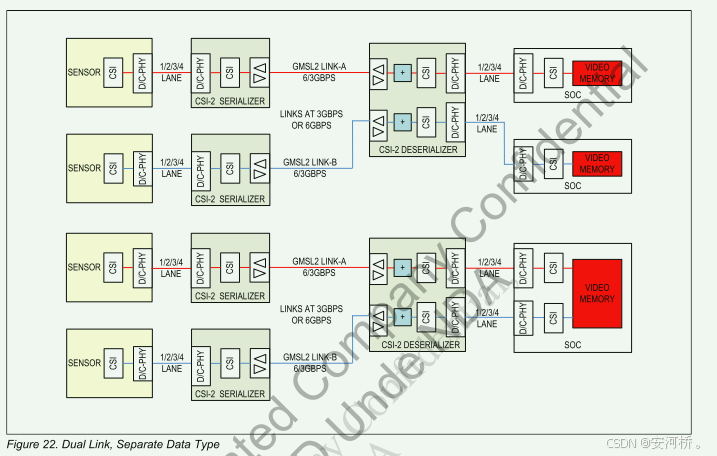

2.双LINK的原理(two GMSL2 serializers can be used with one deserializer to connect two sensors to one or two soc)

MAX9296A和MAX96717F链路配置示例:

exp:

803

803

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?