TESTKEY就是做一些测试结构,通过probe PAD来量测,评估测试结构的性能指标。得到此器件的SPICE模型。所以一般待测试器件结构会有多种变体.比如:mos器件,会有多种串并联方式外加L W 变化值的组合。组合出来的这些mos 三端口会单独连接到测试PAD上。MOM电容器件,会有多种叉指宽度变化,space的变化,金属层次的变化等。

有些公司在新工艺导入时,会做一些TESTKEY来摸底此工艺下,所关心的器件的实际电学模型.一般的设计方式是,设计者提供好需要测试的器件结构类型以及需要测试的各size 值。Layout 工程师根据这些信息手动调出对应的器件,修改成对应的参数,然后放置到teskline中,进行版图连接。对于pdk中不存在的器件或结构,只能手工layout。所需要的结构变化也只能手动调整。所以同一个结构可以就有几十种layout,人工做是非常耗时耗力的。

通过定制自动化flow,从四周工作量降到一周完成。效率提升明显。

准备工作梳理要测试的器件结构,统一做成参数化cell,pdk中pcell 或自定制udd cell

UDD 制作可以参考以前文章:

Step by Step 教你使用UDD做Pcell

UDD 是什么?版图中如何使用?

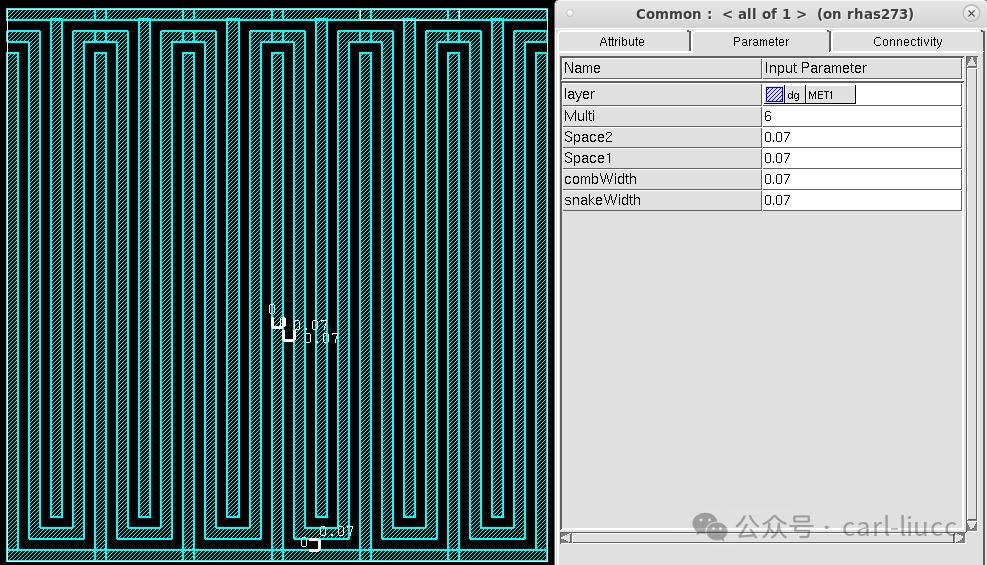

如下UDD 制作成的三端电容,开放需要变化的参数,供脚本来修改填充。

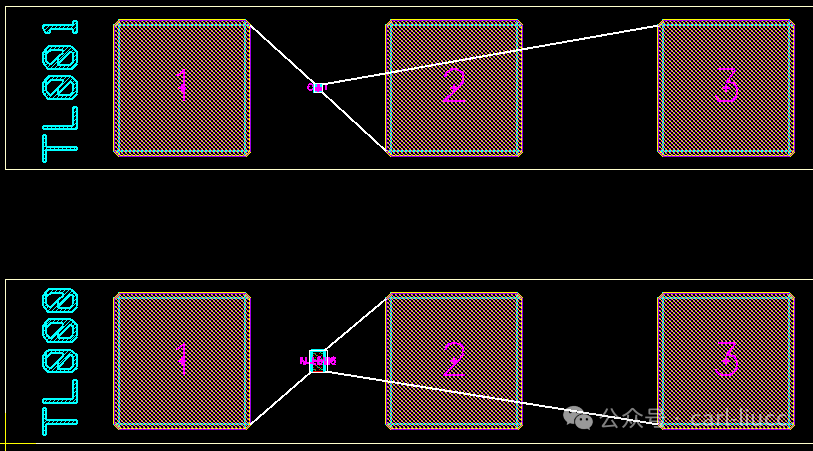

PAD的大小与pitch是固定这个比较容易处理,在第一颗PAD需要增加x方向offset,用来后续生成testline的标记logo

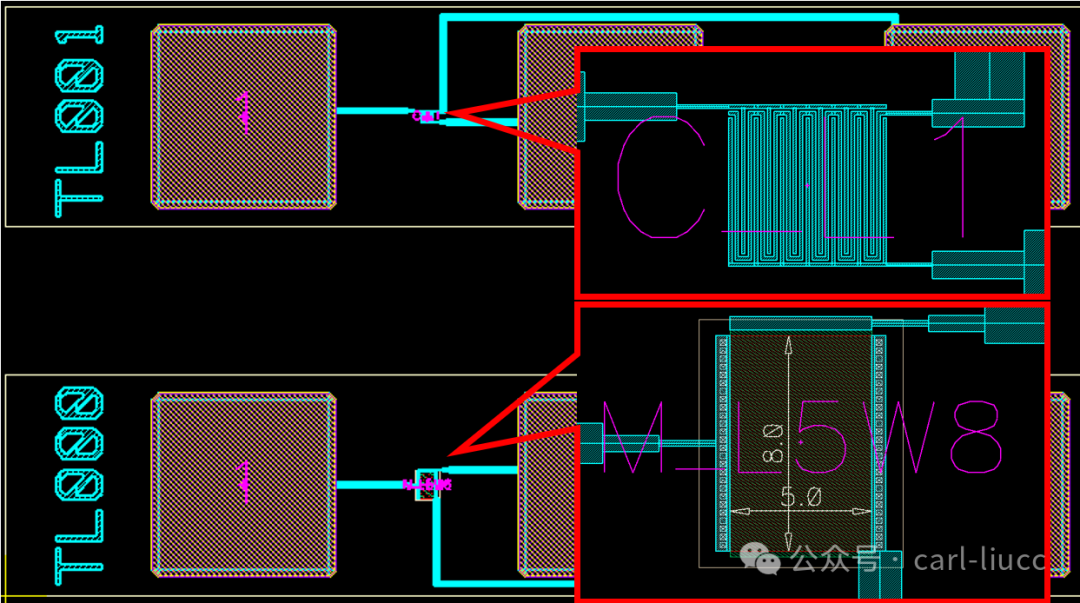

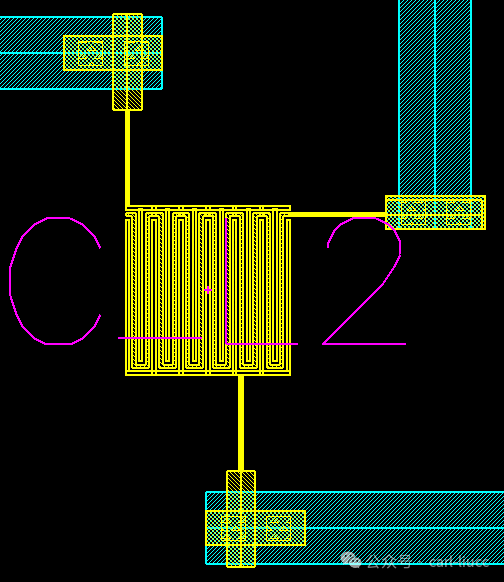

根据连接关系,脚本自动创建连接。这里给定使用Metal1 Metal2 两层金属可以使用。

这里在连接到器件上的pin时做了fan-in的处理,让连接更加强壮也可以避免宽走线在device附近的space问题。

电容使用Metal2 生成时的连线,也可以自动做router. 处理不太美观,但连接没有问题。

如此就可以批量完成testline的创建与probe line创建连接。

如何在工作中消除这类痛点。能否找到优化flow的方式。下面是我完成此需求的一些思路。

将痛点具体化:第一步拆分成子需求

1.testline PAD如何摆放,对应pitch与个数要求

2.器件参数化,pcell自定制使用UDD的方式实现

3.器件如何放置到需要连接的PAD指定位置

4.器件如何与对应的pad做自动连接,连线金属层与通孔约束

5.器件parameter与其他标识mark生成

6.上述各子需求之间的关系

第二步梳理出必要的输入信息

1.pad的pitch,testline的space,对应pcell或udd cell的参数列表与参数值列表。

2.device 放置的位置信息,pin连接到PAD的关系信息。

第三步脚本开发测试,结合实际项目需求优化.

IC模拟版图设计

IC 设计后端知识分享 EDA使用心得 Linux 环境 脚本分享 Perc开发 Custom compiler

57篇原创内容

公众号

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?