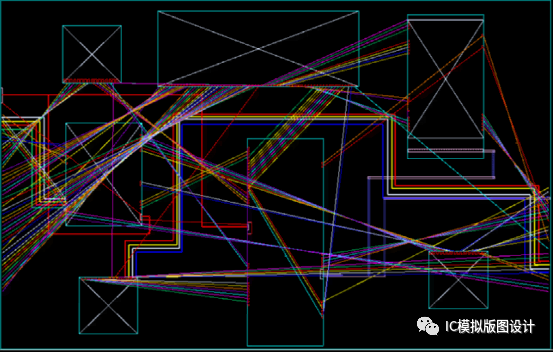

版图设计中很多情况都是TOP down设计加bottom up设计相结合,在初期做floorplan时,我们关心模块的大小,信号流走向,Bump或PAD所在位置,然后来确定每个模块所摆放位置。各模块大小可以根据参考版图或已有电路大概评估,Bump 或PAD布局要看封装电源域分布等确定。信号流有没有好的方式来查看呢?可能designer会给个大概的走向。我们来看看借助CC里的 Route功能是不是能更有效的来做信号流的连线。

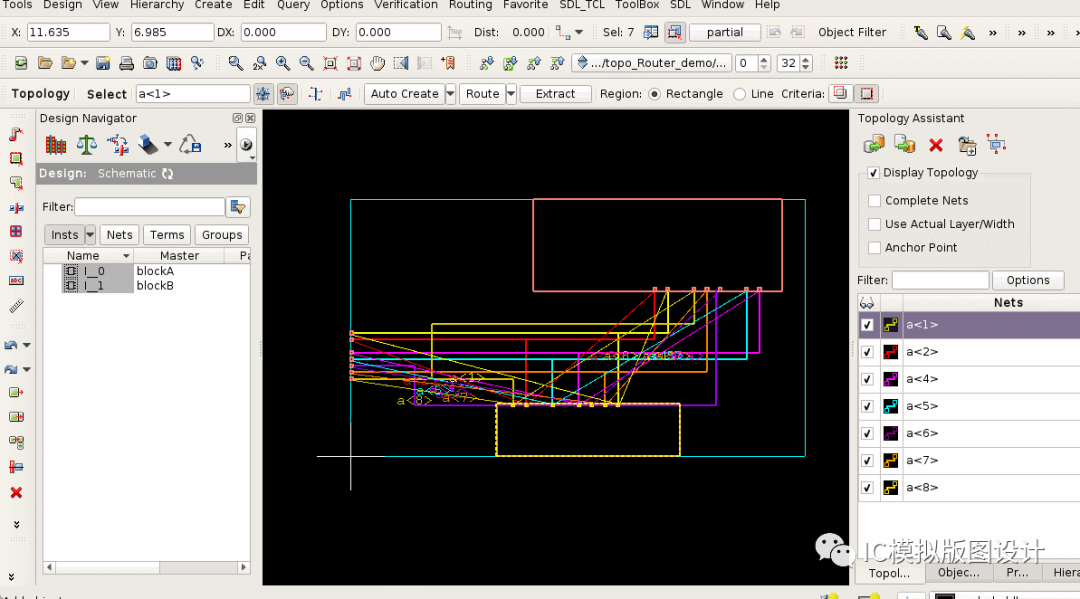

1.topology Routing是一种pin-pin的route guidance方式,可以自动生成规整的拓扑连线,也可以手动来产生或着调整这些拓扑连线。我们可以对每一段走线来定义使用的走线层次宽度,同时还可以根据EM和Resistance的约束来自动调整走线的宽度。重要的一点这些走线信息可以保存到当前design中或者导出到文本。这些拓扑走线可以随着pin的位置自动调整。这点跟普通飞线有很大区别。

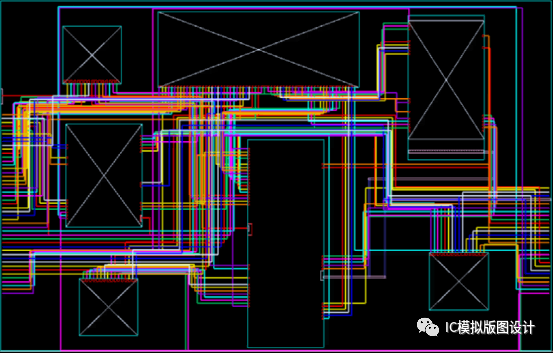

可见信号流比较清晰,floorplan阶段可以通过这样的拓扑连线调整每个模块内部出pin放下,关键信号宽度,是否sheilding.

上图可以看到随着模块的反转,拓扑走线会跟着模块的pin自动调整新的位置。每段走线也都可以人工干预。显示上可以使用实际的layer来显示preview 的routing效果(非真实layer)。没问题之后可以执行Route来产生最终的连线。

2.半自动交互式Route。p2p模式 可以选择两点来完成自动连线,或中间规定好走向。Ftc模块可以根据鼠标走向来完成route。每个都对应非常丰富的option供选择,这里不一一演示。

3.最常用的create path,cc里也有非常丰富的功能,比如下图演示对一组bus调整,可以直接调整bus的space,有fin-in/out 或Ladder,compact 等。

IC模拟版图设计

IC 设计后端知识分享 EDA使用心得 Linux 环境 脚本分享 Perc开发 Custom compiler

50篇原创内容

公众号

收录于合集 #文章汇总

68个

上一篇版图中几种设置parameter的方式

8162

8162

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?