目录

有三种用于两个IC间通信的时序模型——系统同步、源同步和自同步。

1.系统同步

系统同步:两片IC之间进行通信时,使用一个共用时钟,用于数据发送和接收。

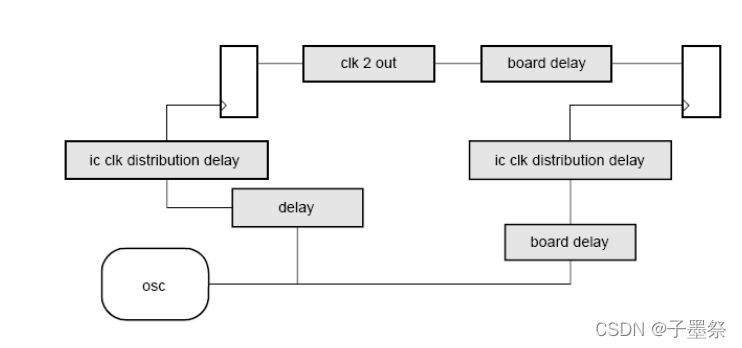

如下图1,这种方法是多年来最常用的。乍一看会觉得它很简单,但看过图2中的时序模型,就不会这么认为了。阴影框部分表示:为确保可靠,接收电路必须予以处理和抵消的延迟。

图1.系统同步结构图

图2.系统同步时序模型

系统同步:两片IC之间进行通信时,使用一个共用时钟,用于数据发送和接收。

2.源同步

源同步:两个IC间进行通信时,发送IC生成一个伴随发送数据的时钟信号。接收IC利用该转 发时钟进行数据接收。

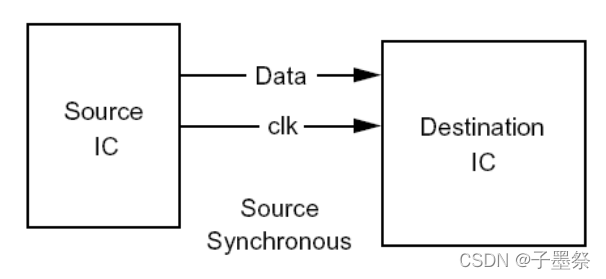

多年来,大多数的信号延迟都被忽略了,因为与有效时间相比,延迟时间很短。但是,随着速 度的提高,管理延迟变得越来越困难,甚至最终变得不可能。改善问题的方法之一就是在发送数据的同时发送一个时钟副本。这种方法叫源同步(图3),它极大地简化时序参数。

图3.源同步结构图

调节转发时钟的输出时间,使时钟在数据单元的中间位置发生翻转。因此,数据线和时钟线的 长度需要互相匹配。但是,这种方法存在一些缺点。在目的芯片接收到的数据必须从接收时钟 域转移到全局芯片时钟域中。

图4.源同步时序模型

源同步:两个IC间进行通信时,发送IC生成一个伴随发送数据的时钟信号。接收IC利用该转 发时钟进行数据接收。

转发时钟:转发时钟(cf)或时钟转发是用于源同步的另一个技术术语。

源同步设计导致时钟域数量的剧增。对于具有有限时钟缓冲器的现场可编程门阵列(FPGA)和 必须量身定制每个时钟树的专用集成电路(ASIC)等器件来说,这将带来时序约束和分析难题。 对于采用大型并行总线的设计来说,该问题会进一步加重:由于电路板的设计限制,每条数据 总线通常需要采用1个以上的转发时钟。因此,一条32位总线可能需要4个、甚至是8个转发时钟。

3.自同步

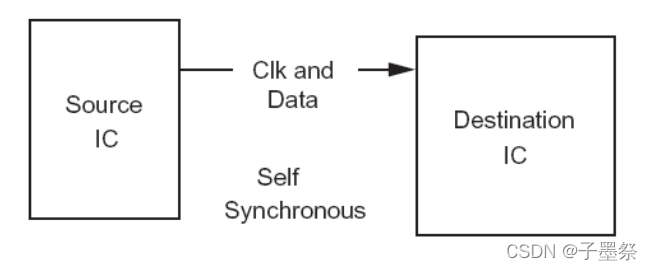

自同步:两块芯片之间的通信,其中发送芯片产生的数据流同时包括数据和时钟信息。

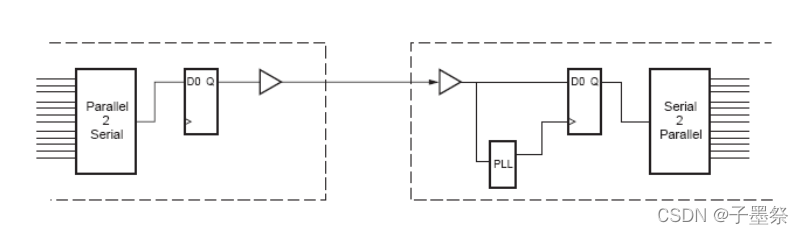

自同步模型如图5所示。这里,数据流包含数据和时钟。

自同步接口的三个主要模块分别是并串转换、串并转换和时钟数据恢复。

而这,也是高速串行接口的基础。

自同步:两块芯片之间的通信,其中发送芯片产生的数据流同时包括数据和时钟信息。

PS:我只是理论的搬运工。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?