1、系统设计要求

该交通灯控制器用于主干道与支道公路的交叉路口,要求是优先保证主干道的畅通,因此,设计要求如下。

1、平时处于“主干道绿灯,支道红灯”状态,只有在支道有车辆要穿过主干道时,才将交通灯切向“主干道红灯,支道绿灯”,一旦支道无车辆通过路口,交通灯又回到“主干道绿灯,支道红灯”的状态。

2、主干道每次通行的时间不得短于1min,支路每次通行的时间不得长于20s,而这两个状态交换过程中出现“主干道黄灯,支道红灯”和“主干道红灯,支道黄灯”的状态,持续时间都为4s。

2、设计分析

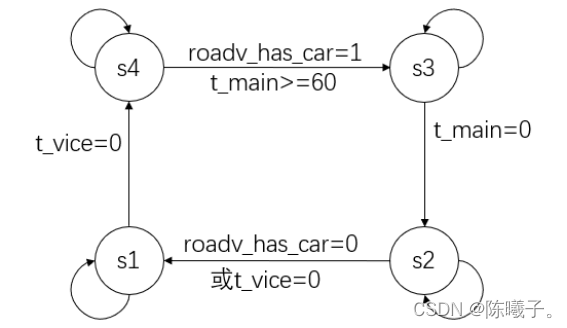

1、用状态机来设计实现交通信号灯的颜色状态。交通信号灯状态可以分成4种,s4:主干道绿灯、支道红灯;s3:主干道黄灯、支道红灯;s2:主干道红灯、支道绿灯;s1:主干道红灯、支道黄灯。状态转移图:

2、用计数器分频来实现状态之间的切换。当支道无车(因此需要定义一个“支道来车”变量has_car)时,将一直处于s4状态;若主干道绿灯超过1min且支道来车时,切换为s3状态;s3状态持续4s后切换为s2状态;s2状态持续20s后切换为s1状态;支道无车又恢复为s4状态。

3、具体实现过程

1、输入信号有时钟信号clk,使能信号en,支路来车信号has_car。输出信号有主干道信号l_m,支路信号灯l_v,主干道计时器t_m,支路计时器t_v。模块内部信号:表示状态信号state;计数信号count_m、count_v。计数为二位十进制因此用_1表示个位,_2表示十位。

2、信号灯用3位二进制数表示红绿黄三个灯,其中只有1位值为1,另外两个值为0,值为1代表该位灯亮,如100表示为红灯、010表示绿灯、001表示黄灯。

3、用二段状态机进行设计。第一段进行状态计数以及状态转移,第二段进行信号灯输出。

第一段:进行状态计数。触发信号为clk、en,触发方式为边沿触发。如果使能信号en为0,则重置计数信号;如果en信号为1,则根据状态信号state进行相应操作。

(1)状态为s4:主干道绿灯、支道红灯。计数器count_m正常每次加1计数,计数器count_v不工作,值为0。如果支路有车,即has_car由0变为1,并且count_m的计数值已经大于60,说明此时已经满足改变信号灯的条件,可以改变信号灯的状态,则状态变为s3,同时给count_m重新赋值4,以便进行下一状态计数。如果不能同时满足上述两个条件,则状态不变。

(2)状态为s3:主干道黄灯、支道红灯。计数器count_m从4开始每次减1,计数器count_v不工作。当count_m为1时,状态变为s2,同时给count_v赋值20。其他情况状态不变。

(3)状态为s2:主干道红灯、支道绿灯。计数器count_v计数从20开始递减。计数器count_m此时不工作,值为0。在此状态下,如果支路汽车通行完毕,即has_car由1变为0,或者count_v计数从20减为1,说明此时已经满足改变信号灯的条件,要改变信号灯的状态,则状态变为s1,同时给count_v赋值4。其他情况状态不变。

(4)状态为s1:主干道红灯、支道黄灯。此状态需要实现倒计时4s,只需count_v从4减为1就改变状态,当count_v为1时,状态变为s4。其他情况状态不变。

第二段:进行信号灯输出。触发信号为state,触发方式为电平触发,根据状态信号state进行相应输出。

(1)状态为s4:主干道绿灯、支道红灯。即输出为:l_m=3'b010; l_v=3'b100

(2)状态为s3:主干道黄灯、支道红灯。即输出为:l_m=3'b001; l_v=3'b100

(3)状态为s2:主干道红灯、支道绿灯。即输出为:l_m=3'b100; l_v=3'b010

(4)状态为s1:主干道红灯、支道黄灯。即输出为:l_m=3'b100; l_v=3'b001

4、最后用assign语句将时钟输出信号和内部计数信号连接。

4、Verilog HDL源码:

module Traffic(clk,en,has_car,l_m,l_v,t_m1,t_m2,t_v1,t_v2);

input clk,en,has_car; //时钟信号1Hz,使能信号,支路来车信号

output reg [2:0]l_m,l_v; //信号灯控制信号

output [3:0]t_m1,t_m2,t_v1,t_v2; //主干道m、支路v计时信号(1为个位,2为十位)

reg [3:0]count_m1,count_m2,count_v1,count_v2; //计数

reg [1:0] state;

parameter s1=2'b00,s2=2'b01,s3=2'b10,s4=2'b11; //定义状态

always@ (posedge clk or negedge en)

begin

if(!en)begin

state<=s4;

count_m1<=4'b0;

count_m2<=4'b0;

count_v1<=4'b0;

count_v2<=4'b0;

end

else case(state)

s4:begin

count_m1<=count_m1+1; //主干道十进制计时

count_v1<=4'b0;

count_v2<=4'b0;

if(count_m1==4'b1001)begin

count_m1<=4'b0;

count_m2<=count_m2+1;

end

if(has_car==1&&count_m2>=4'b0110) begin //判断状态转移条件

state<=s3;

count_m1<=4'b0100;

count_m2<=4'b0;

end

else

state<=s4;

end

s3:begin

count_v1<=4'b0; //主干道4s黄灯倒计时

count_v2<=4'b0;

count_m1<=count_m1-1;

if(count_m1==4'b1) begin

state<=s2;

count_v2<=4'b10;

count_v1<=4'b0;

end

else state<=s3;

end

s2:begin

count_m1<=0; //支路20s绿灯倒计时

count_m2<=0;

count_v1<=count_v1-1;

if(count_v1==4'b0)begin

count_v1<=4'b1001;

count_v2<=count_v2-1;

end

if(has_car==0||(count_v1==4'b1)&&(count_v2==4'b0))begin

state<=s1;

count_v1<=4'b0100;

count_v2<=4'b0;

end

else

state<=s2;

end

s1:begin //支路4s黄灯倒计时

count_m1<=4'b0;

count_m2<=4'b0;

count_v1<=count_v1-1;

if(count_v1==4'b1) state<=s4;

else state<=s1;

end

default:begin l_m<=0;l_v<=0;end

endcase

end

always@ (state)

begin

case(state)

s4:begin

l_m<=3'b010; //G

l_v<=3'b100; //R

end

s3:begin

l_m<=3'b001; //Y

l_v<=3'b100; //R

end

s2:begin

l_m<=3'b100; //R

l_v<=3'b010; //G

end

s1:begin

l_m<=3'b100; //R

l_v<=3'b001; //Y

end

default:begin

l_m<=3'bxxx;

l_v<=3'bxxx;

end

endcase

end

assign t_m1=count_m1;

assign t_m2=count_m2;

assign t_v1=count_v1;

assign t_v2=count_v2;

endmodule

如有错漏之处,敬请指正,不吝赐教。

2067

2067

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?