Versal 介绍

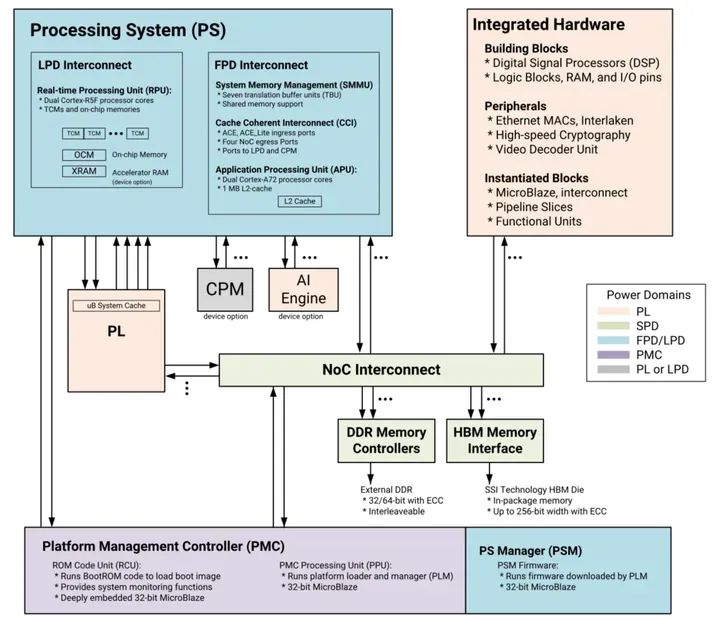

Versal 包含了 Cortex-A72 处理器和 Cortex-R5 处理器,PL 端可编程逻辑部分,PMC 平台管理控制器,AI Engine 等模块,与以往的 ZYNQ 7000 和 MPSoC 不同,Versal 内部是通过 NoC 片上网络进行互联。

Versal 芯片的总体框图

Versal 芯片的总体框图

PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SoC 的部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是 FPGA 部分。

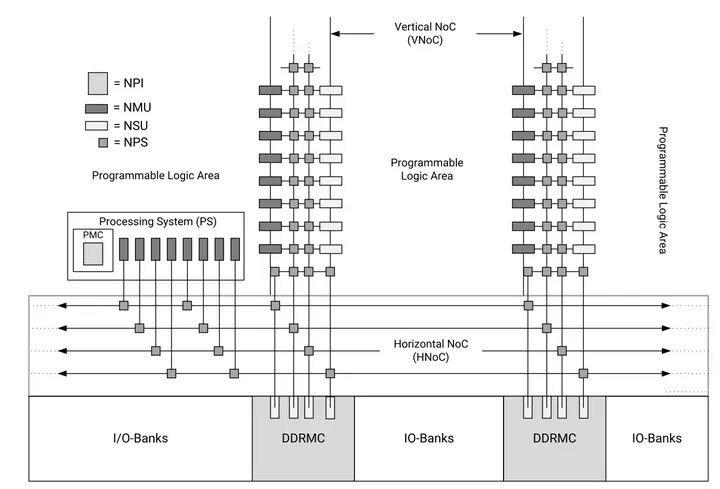

NoC 架构

Versal 可编程片上网络(NoC) 是一种 AXI 互连网络,用于在可编程逻辑 PL,处理器系统 PS 等之间共享数据,而之前的 Versal 系列采用的 AXI 交叉互联模块,这是 Versal 的不同之处。

NoC 是为可扩展性而设计的。它由一系列相互连接的水平(HNoC)和垂直(VNoC)路径,由一组可定制的硬件实现组件支持,这些组件可以以不同的方式进行配置,以满足设计时序、速度和逻辑利用率要求。以下是 NoC 的结构图

NoC 的结构图

从 NoC 的结构图,可以看到,其主要由 NMU(NoC master units),NSU(NoC slave units),NPI(NoC programming interface),NPS(NoC packet switch)组成。PS 端可以连接到 NMU,再通过 NPS 连接访问到 DDRMC,同样 PL 端也可以通过 NMU,NPS 访问到 DDRMC。通过 NPS 路由的方式,灵活地访问各模块。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

434

434

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?