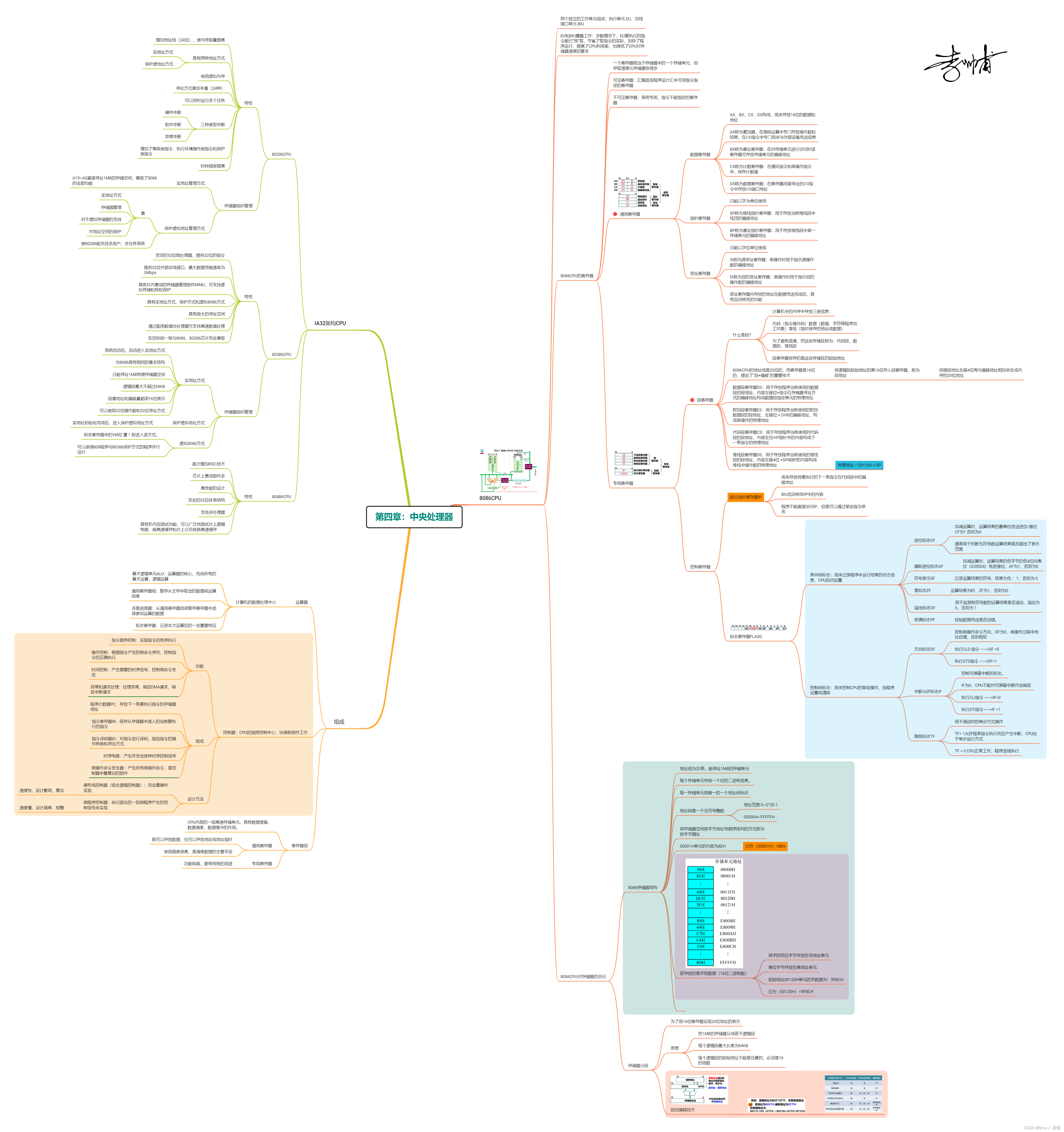

文章目录

8086CPU

两个独立的工作单元组成:执行单元 EU、总线接口单元 BIU

EU和BIU重叠工作:多数情况下,EU要执行的指令都已“预”取,节省了取指令的实际,加快了程序运行,提高了CPU利用率,也降低了CPU对存储器速度的要求

8086CPU的寄存器

-

一个寄存器相当于存储器中的一个存储单元,但存取速度比存储器快得多

-

可见寄存器:汇编语言程序设计汇中可用指令指定的寄存器

-

不可见寄存器:系统专用,指令不能指定的寄存器

-

通用寄存器

-

数据寄存器

- AX、BX、CX、DX构成,用来存放16位的数据和地址

- AX称为累加器,在乘除运算中专门存放操作数和结果,在I/O指令中专门用来与外部设备传送信息

- BX称为基址寄存器:在对存储单元进行访问时该寄存器可存放存储单元的偏移地址

- CX称为计数寄存器:在循环指令和串操作指令中,保存计数值

- DX称为数据寄存器:在寄存器间接寻址的I/O指令中存放I/O端口地址

-

指针寄存器

- 只能以字为单位使用

- SP称为堆栈指针寄存器:用于存放当前堆栈段中栈顶的偏移地址

- BP称为基址指针寄存器:用于存放堆栈段中某一存储单元的偏移地址

-

变址寄存器

- 只能以字位单位使用

- SI称为源变址寄存器:串操作时用于指示源操作数的偏移地址

- DI称为目的变址寄存器:串操作时用于指示目的操作数的偏移地址

- 变址寄存器内存放的地址在数据传送完成后,具有自动修改的功能

-

-

专用寄存器

-

段寄存器

-

什么是段?

- 计算机中的内存中存放三类信息:

- 代码(指令操作码)数据(数值,字符等程序加工对象)堆栈(临时保存的地址或数据)

- 为了避免混淆,把这些存储区称为:代码段,数据段,堆栈段

- 段寄存器保存的是这些存储区的起始地址

-

8086CPU的地址线是20位的,而寄存器是16位的,提出了“段+偏移”的重要技术

-

将逻辑段起始地址的高16位存入段寄存器,称为段地址

- 按照段地址左移4位再与偏移地址相加来生成内存的20位地址

-

-

数据段寄存器DS:用于存放程序当前使用的数据段的段地址,内容左移位+指令红存储器寻址方式的偏移地址构成数据段指定单元的物理地址

-

附加段寄存器ES:用于存放程序当前使用的附加数据段的段地址,左移位 + DI中的偏移地址,构成串操作的物理地址

-

代码段寄存器CS:用于存放程序当前使用的代码段的段地址,内容左位+IP指针中的内容构成下一条指令的物理地址

-

堆栈段寄存器SS,用于存放程序当前使用的堆栈段的段地址,内容左移4位 +SP或BP的内容构成堆栈中操作数的物理地址

- 物理地址 = SS*10H + SP

-

-

控制寄存器

-

指令指针寄存器IP

- 用来存放将要执行的下一条指令在代码段中的偏移地址

- BIU自动修改IP中的内容

- 程序不能直接访问IP,但是可以通过某些指令修改

-

标志寄存器FLASG

-

条件码标志:用来记录程序中运行结果的状态信息,CPU自动设置

-

进位标志CF

- 加减运算时,运算结果的最高位发送进位/借位 CF为1 否则为0

- 通常用于判断无符号数运算结果是否超出了表示范围

-

辅助进位标志AF

- 加减运算时,运算结果的低字节的低4位向高位(D3向D4)有进借位,AF为1,否则为0

-

符号表示SF

- 记录运算结果的符号,结果为负 :1,否则为 0

-

零标志ZF

- 运算结果为时,ZF为1,否则为0

-

溢出标志OF

- 用于监测有符号数的运算结果是否溢出,溢出为1,否则为 0

-

奇偶标志PF

- 检验数据传送是否出错。

-

-

控制码标志:用来控制CPU的某些操作,由程序设置或清除

-

方向标志DF

- 控制串操作命令方向,DF为0,串操作过程中地址自增,否则相反

- 执行CLD 指令 ——>DF =0

- 执行STD指令 ——>DF=1

-

中断允许标志IF

- 控制可屏蔽中断的标志。

- IF为0,CPU不能对可屏蔽中断作出响应

- 执行CLI指令 ——>IF=0

- 执行STI指令——>IF =1

-

跟踪标志TF

- 用于调试时的单步方式操作

- TF= 1允许每条指令执行完后产生中断,CPU处于单步运行方式

- TF = 0 CPU正常工作,程序连续执行

-

-

-

-

8086CPU对存储器的访问

-

8086存储器结构

-

地址线为20条,能寻址1MB的存储单元

-

每个存储单元存放一个8位的二进制信息。

-

每一存储单元用唯一的一个地址码标识

-

地址码是一个无符号整数

- 地址范围 0~2^20-1

- 00000H~FFFFFH

-

将存储器空间按字节地址号顺序排列的方式称为按字节编址

-

00001H单元的内容为8EH

- 记作(00001H)=8EH

-

若存放的是字型数据(16位二进制数)

- 将字的低位字节存放在低地址单元

- 高位字节存放在高地址单元

- 起始地址00120H单元的字数据为:5FBCH

- 记为(00120H)=5FBCH

-

-

存储器分段

-

为了用16位寄存器实现20位地址的表示

-

思想

- 把1MB的存储器分成若干逻辑段

- 每个逻辑段最大长度为64KB

- 每个逻辑段的起始地址不能是任意的,必须是16的倍数

-

段加偏移技术

-

IA32架构CPU

80286CPU

-

特性

-

增加地址线(24位),使内存容量提高

-

具有两种地址方式

- 实地址方式

- 保护虚地址方式

-

使用虚拟内存

-

寻址方式更加丰富(24种)

-

可以同时运行多个任务

-

三种类型中断

- 硬件中断

- 软件中断

- 异常中断

-

增加了高级类指令、执行环境操作类指令和保护类指令

-

时钟频率提高

-

-

存储器组织管理

-

实地址管理方式

- A19~A0直接寻址1MB的存储空间,兼容了8086的全部功能

-

保护虚拟地址管理方式

-

集

- 实地址方式

- 存储器管理

- 对于虚拟存储器的支持

- 对地址空间的保护

-

使80286能支持多用户,多任务系统

-

-

80386CPU

-

特性

- 灵活的32位微处理器,提供32位的指令

- 提供32位外部总线接口,最大数据传输速率为3Mbps

- 具有片内集成的存储器管理部件MMU,可支持虚拟存储和特权保护

- 具有实地址方式,保护方式和虚拟8086方式

- 具有极大的寻址空间

- 通过配用数值协处理器可支持高速数值处理

- 在目标码一级与8086、80286芯片完全兼容

-

存储器组织管理

-

实地址方式

- 系统启动后,自动进入实地址方式

- 与8086具有相同的基本结构

- 只能寻址1MB物理存储器空间

- 逻辑段最大不超过64KB

- 段基地址和偏移量都用16位表示

- 可以使用32位操作数和32位寻址方式

-

保护虚拟地址方式

- 实地址初始化完成后,进入保护虚拟地址方式

-

虚拟8086方式

- 标志寄存器中的VM位 置 1 即进入该方式。

- 可以使得8086程序与80386保护方式的程序并行运行

-

80486CPU

-

特性

- 首次增加RISC技术

- 芯片上集成部件多

- 高性能的设计

- 完全的32位体系结构

- 支持多处理器

- 具有机内自测试功能,可以广泛地测试片上逻辑电路、超高速缓存和片上分页转换高速缓存

组成

运算器

-

计算机的数据处理中心

- 算术逻辑单元ALU:运算器的核心,完成所有的算术运算,逻辑运算

- 通用寄存器组:暂存从主存中取出的数据或运算结果

- 多路选择器:从通用寄存器组或暂存寄存器中选择参加运算的数据

- 标志寄存器:记录本次运算后的一些重要特征

控制器:CPU的指挥控制中心,协调各部件工作

-

功能

- 指令顺序控制:实现指令的有序执行

- 操作控制:根据指令产生的微命令序列,控制指令的正确执行

- 时间控制:产生需要的时序信号,控制微命令发出

- 异常和请求处理:处理异常,响应DMA请求,响应中断请求

-

组成

- 程序计数器PC:存放下一条要执行指令的存储器地址

- 指令寄存器IR:保存从存储器中读入的当前要执行的指令

- 指令译码器ID:对指令进行译码,指出指令的操作种类和寻址方式

- 时序电路:产生并发出各种时序控制信号

- 微操作命令发生器:产生所有微操作命令,是控制器中最复杂的部件

-

设计方法

-

硬布线控制器(组合逻辑控制器):完全靠硬件实现

- 速度快,设计繁琐,复杂

-

微程序控制器:执行固化的一段微程序产生的控制信号来实现

- 速度慢,设计简单,规整

-

寄存器组

-

CPU内部的一组高速存储单元,具有数据准备,数据调度,数据缓冲的作用。

-

通用寄存器

- 既可以存放数据,也可以存放地址或地址指针

- 使用频度很高,是调度数据的主要手段

-

专用寄存器

- 功能转移,都有特殊的用途

5229

5229

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?