本科生期末试卷 三

一.选择题(每小题1分,共10分)

1.冯·诺依曼机工作的基本方式的特点是______。

A 多指令流单数据流

B 按地址访问并顺序执行指令

C 堆栈操作

D 存贮器按内容选择地址

2.在机器数______中,零的表示形式是唯一的。

A 原码 B 补码 C 移码 D 反码

3.在定点二进制运算器中,减法运算一般通过______来实现。

A 原码运算的二进制减法器

B 补码运算的二进制减法器

C 原码运算的十进制加法器

D 补码运算的二进制加法器

4. 某计算机字长32位,其存储容量为4MB,若按半字编址,它的寻址范围是______。

A 4MB B 2MB C 2M D 1M

5.主存贮器和CPU之间增加cache的目的是______。

A 解决CPU和主存之间的速度匹配问题

B 扩大主存贮器容量

C 扩大CPU中通用寄存器的数量

D 既扩大主存贮器容量,又扩大CPU中通用寄存器的数量

6.单地址指令中为了完成两个数的算术运算,除地址码指明的一个操作数外,另一个常需采用______。

A 堆栈寻址方式 B 立即寻址方式 C 隐含寻址方式 D 间接寻址方式

7.同步控制是______。

A 只适用于CPU控制的方式

B 只适用于外围设备控制的方式

C 由统一时序信号控制的方式

D 所有指令执行时间都相同的方式

8.描述 PCI 总线中基本概念不正确的句子是______。

A.PCI 总线是一个与处理器无关的高速外围总线

B.PCI总线的基本传输机制是猝发式传送

C. PCI 设备一定是主设备

D. 系统中只允许有一条PCI总线

9.CRT的分辨率为1024×1024像素,像素的颜色数为256,则刷新存储器的容量为______。

A 512KB B 1MB C 256KB D 2MB

10.为了便于实现多级中断,保存现场信息最有效的办法是采用______。

A 通用寄存器 B 堆栈 C 存储器 D 外存

二.填空题(每小题3分,共15分)

1.数的真值变成机器码可采用A. ______表示法,B. ______表示法,C.______表示法,移

码表示法。

2.形成指令地址的方式,称为A.______方式,有B. ______寻址和C. ______寻址。

3. CPU从A. ______取出一条指令并执行这条指令的时间和称为B. ______。由于各种指

令的操作功能不同,各种指令的指令周期是C. ______。

4.微型机的标准总线从16位的A. ______总线,发展到32位的B. ______总线和C.

______总线,又进一步发展到64位的PCI总线。

5.VESA标准是一个可扩展的标准,它除兼容传统的A. ______等显示方式外,还支持B.

______像素光栅,每像素点C. ______颜色深度。

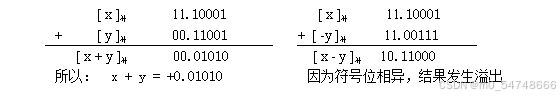

三.(9分)已知 x = - 0.01111 ,y = +0.11001,

求 [ x ]补 ,[ -x ]补 ,[ y ]补 ,[ -y ]补 ,x + y = ? ,x – y = ?

四.(9分)假设机器字长16位,主存容量为128K字节,指令字长度为16位或32位,共有128条指令,设计计算机指令格式,要求有直接、立即数、相对、基值、间接、变址六种寻址方式。

五.(9分)某机字长32位,常规设计的存储空间≤32M ,若将存储空间扩至256M,请提出一种可能方案。

本科生期末试卷三答案

一.选择题

1 B 2 B,C 3 D 4 C 5 A

6 C 7 C 8 C, D 9 B 10 B

二.填空题

- A.原码 B.补码 C.反码

2. A.指令寻址 B.顺序 C.跳跃 - A.存储器 B.指令周期 C.不相同的

- A.ISA B.EISA C.VISA

- A.VGA B.1280×1024 C.24位

三.解:[ x ]原 = 1.01111 [ x ]补 = 1.10001 所以 :[ -x ]补 = 0.01111

[ y ]原 = 0.11001 [ y ]补 = 0.11001 所以 :[ -y ]补 = 1.00111

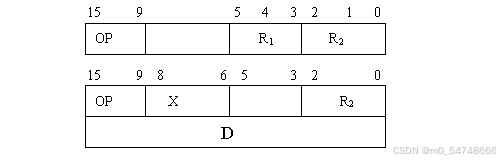

四.解:由已知条件,机器字长16位,主存容量128KB / 16= 64K字,因此MAR = 16位,共128条指令,故OP字段占7位。采用单字长和双字长两种指令格式,其中单字长指令用于算术逻辑和I / O类指令,双字长用于访问主存的指令。

寻址方式由寻址模式X定义如下:

X = 000 直接寻址 E = D(64K)

X = 001 立即数 D = 操作数

X = 010 相对寻址 E = PC + D PC = 16位

X = 011 基值寻址 E = Rb + D ,Rb =16 位

X = 100 间接寻址 E = (D)

X = 101 变址寻址 E = RX + D ,RX = 10位

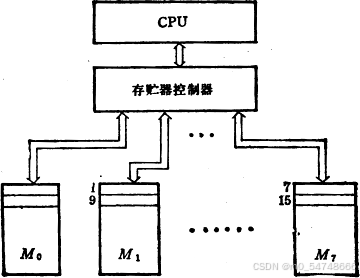

五.解:可采用多体交叉存取方案,即将主存分成8个相互独立、容量相同的模块M0,M1,M2,…M7,每个模块32M×32位。它各自具备一套地址寄存器、数据缓冲寄存器,各自以同等的方式与CPU传递信息,其组成结构如图B3.3:

图B3.3

CPU访问8个存贮模块,可采用两种方式:一种是在一个存取周期内,同时访问8个存贮模块,由存贮器控制器控制它们分时使用总线进行信息传递。另一种方式是:在存取周期内分时访问每个体,即经过1 / 8存取周期就访问一个模块。这样,对每个模块而言,从CPU给出访存操作命令直到读出信息,仍然是一个存取周期时间。而对CPU来说,它可以在一个存取周期内连续访问8个存贮体,各体的读写过程将重叠进行。

359

359

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?