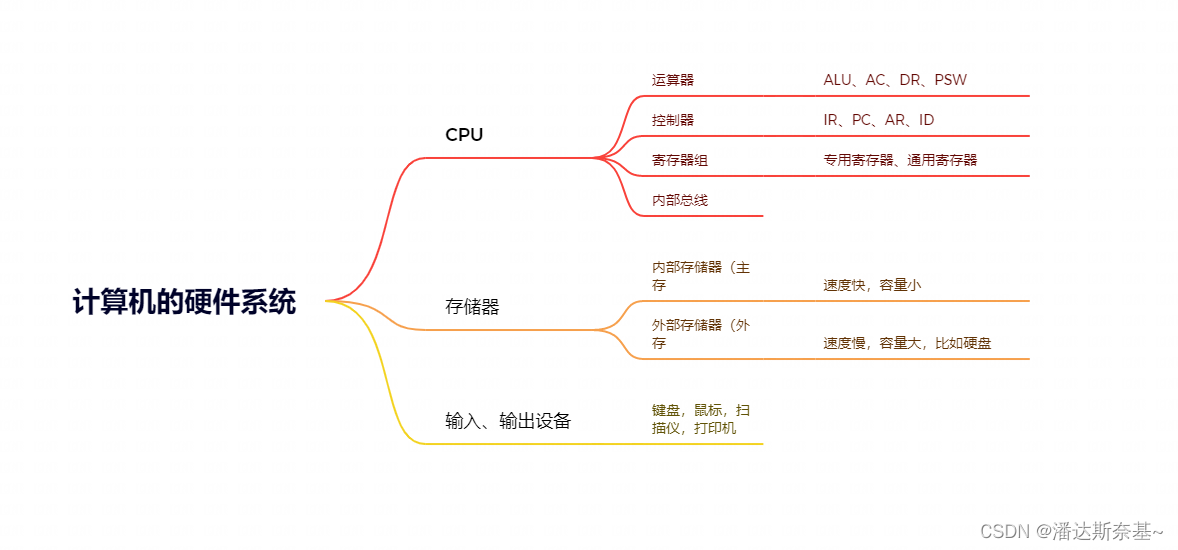

第一章 计算机系统基础

1.1计算机硬件系统组成

CPU的组成

运算器

-

功能:执行算术运算和逻辑运算,算术运算有加减乘除等,逻辑运算有与或非,零值测试等

-

组成:

- 算数逻辑单元(ALU):负责处理数据运算

- 累加寄存器(AC):也称累加器,当算ALU执行运算时,为期提供工作区域

- 数据缓冲寄存器(DR):对内存进行读写操作时,DR暂时存放读写数据或指令。作为CPU、内存、外设之间在操作速度上的缓冲,以及数据传送的中转站

- 状态条件寄存器(PSW):保存根据算术指令和逻辑指令运行或测试的结果建立的各种条形码内容

控制器

-

功能:决定计算机运行过程的自动化,保证程序的正常执行,也要能够处理异常事件

-

组成:

- 指令寄存器(IR):暂时存放一条指令,由指令译码器根据指令寄存器中的内容产生操作指令,控制其他部分协调工作

- 程序计数器(PC):存放的是将要执行的下一条指令的地址

- 地址寄存器(AR):保存当前CPU所访问的内存单元的地址,由于内存和CPU存储在操作速度上的差异,所以需要使用AR保存地址信息,直至内存读写操作完成

- 指令译码器(ID):对指令中的操作码字段进行分析解释,识别指令的操作,并向操作控制器发出具体的控制信号

进制转换

进制表示:

- 二进制:英文Binary 用B表示

- 八进制:英文Octal 用O表示

- 十进制:英文Decimal 用D表示

- 十六进制:英文Hexadecimal 用H表示

R进制之间转换

- 二、八、十六进制转十进制(按权展开)

- 十进制转二、八、十六进制(整除取余)

存储器与总线

- 数据总线(DB):用来传送数据信息,是双向的,DB的宽度决定了CPU和计算机其它设备之间每次交换数据的位数

- 地址总线(AB):用户传送CPU发出的地址信息,是单向的。地址总线的宽度决定了CPU的最大寻址能力

- 控制总线(CB):用来传送控制信号、时序信号和状态信息等。CB中的每一条线的信息传送方向是单向且确定的,但CB作为一个整体是双向的

输入与输出控制

- 无条件传送:外设总是准备好的,无条件,随时接收和提供数据

- 程序查询方式:CPU利用程序来查询外设状态,准备好了再传数据

- 中断方式:CPU不等待,也不执行程序取查询外设的状态,而是由外设在准备号以后,向CPU发出中断请求

- DMA方式:数据的传输是在主存和外设之间直接进行,不需要CPU的干预,实际操作是有DMA硬件直接完成

- 通道方式和外围处理机方式:更进一步减轻CPU对1/0操作的控制,更进一步提高了CPU的工作效率,但是是以增加更多硬件为代价的

1.2 计算体系结构与存储系统

考点: 计算机体系结构分类,流水线技术,存储系统

此考点不重要,了解下就行

计算机体系结构分类

(1)按处理机的数量进行分类:单处理系统、并行处理与多处理系统、分布式处理系统

(2)按并行程度分类:Flynn分类法;冯泽云分类法;Handler分类法等

流水线技术

- 流水线周期:各子任务中执行时间最长的(最慢的)子任务的执行时间

- 流水线执行时间计算:

假设有n条指令,T= 执行一条指令所需要的时间 + (n-1)* 流水线周期 - 吞吐率:是指单位时间里流水线处理机流出的结果数。即单位时间里执行指令数

- 吞吐率公式:p = 1/max(执行一条指令的时间),即最长子过程所用时间的倒数

存储系统

存储器的分类:

- 按存储器所处的位置:可分为内存和外存

- 按构成存储器的材料:可分为磁存储器,半导体存储器和光存储器

- 按存储器的工作方式:可分为读写存储器和只读存储器

- 按访问方式:可分为按地址访问的存储器和按内容访问的存储器

- 按寻址方式:可分为随机存储器,顺序存储器和直接存储器

随机访问存储器

- 静态随机访问存储器(SRAM)

- 动态随机访问存储器(DRAM)

高速缓存(重点)

- Cache是介于CPU和主存之间的一级存储器,其容量较小,但速度较快,一般比主存快5-10倍

- 作用:调和CPU的速度和内存存取速度之间的差异,从而提升性能

- 它使用的是程序的局部性原理,其内容是主存局部域的副本

- 当CPU需要读取数据时,首先判断要访问的信息是否Cache中,如果在即为命中,如果不在,就要按替换算法把主存中的一块信息调入Cache中

- 替换算法有:随机替换算法、先进先出替换算法、近期最少使用替换算法、优化替换算法等

- CPU工作给出的是主存地址,要从Cache存储器中读写信息,就需要将主存地址转换成Cache存储器的地址,这种地址的转换叫做地址映像

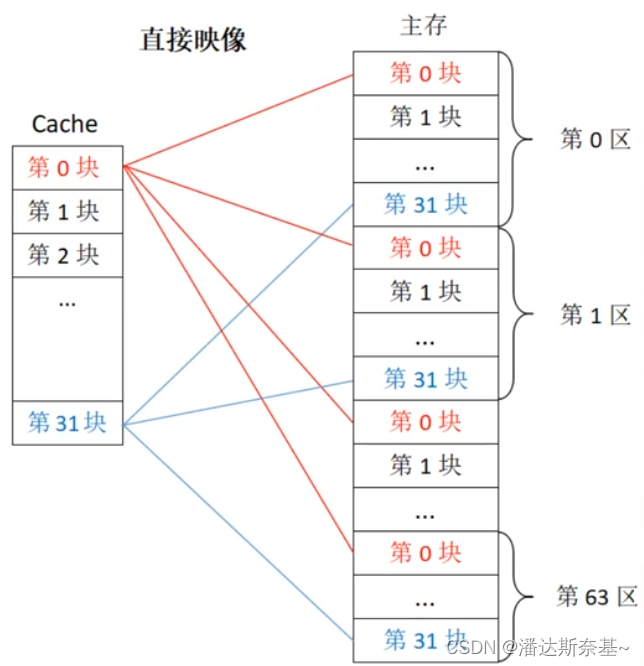

地址映像(重点)

-

直接映像:

- 主存的块与Cache块的对应关系是固定的,主存中的块只能存放在Cache存储器的相同块号中

- 优点:地址变换简单,访问速度快

- 缺点:块冲突率高,Cache空间得不到充分利用

- 主存地址:主存区号,区内块号,块内地址

-

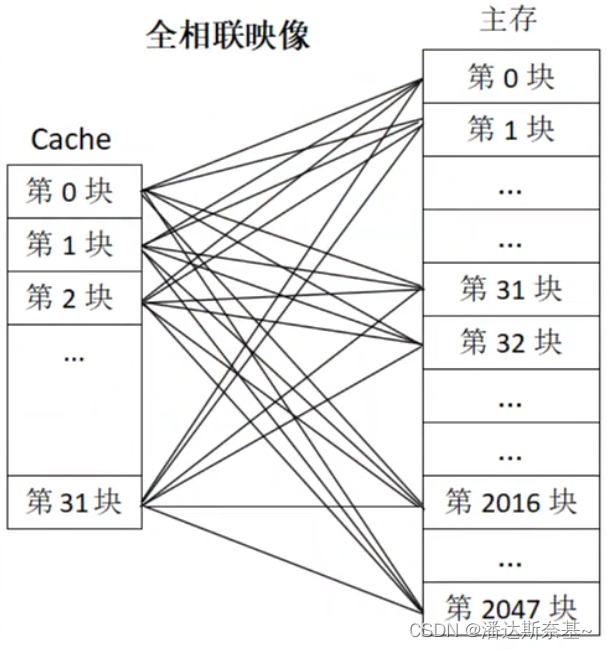

全相联映像

- 全相联映像:主存与Cache存储器均分成容量相同的块。允许主存的任意一块调入Cache存储器的任何一个块的空间中

- 优点:灵活,块冲突率低,只有Cache中的块全部装满后才会出现冲突,Cache利用率高

- 缺点:无法从内存块号中直接获得锁对应Cache的块号,变换比较复杂,地址变换速度慢,成本高

- 主存地址:主存块号,块内地址

-

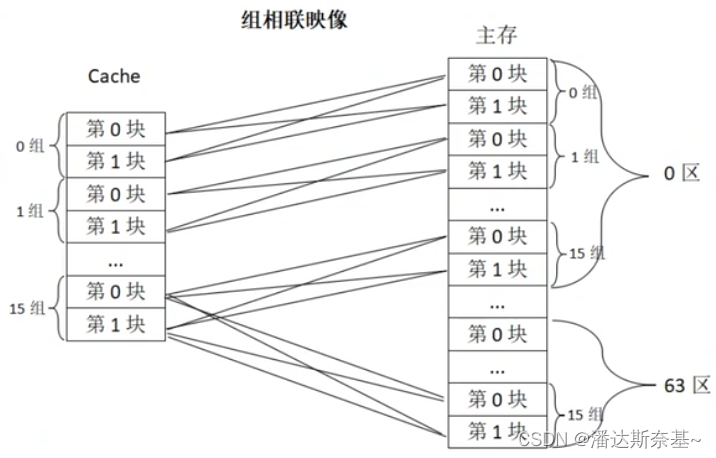

组相联映像

-

是前两种方式的折中。将Cache中的块再分成组。组采用直接映像方式,块采用全相联映像方式。主存的任何区的0组只能存到Cache的0组中,1组只能存放到1组中,依此类推,而组内的块可以存入Cache中相同组的任一块中

-

公式:

- 主存地址位数 = 区号+组号+主存块号+块内地址

- Cache地址位数 = 组号+组内块号+块内地址

-

1.3 安全性、可靠性与系统性能评测基础知识

重点:对称加密技术、非对称加密技术、信息摘要、数字签名和数字加密、计算机可靠性

对称加密技术

-

定义:文件加密和解密使用相同的秘钥,或者虽然不同,也可以从其中一个很容易地推导出另一个

-

代表算法:

- DES:主要采用替换和移位的方法加密,它用56位秘钥对64位二进制数据块进行加密

- 3DES:用两个56位的秘钥

- RC-5

- IDEA:类似于DES,其秘钥长度为128位

- AES:基于排列和置换运算

非对称加密技术

-

定义:同样使用两个秘钥:加密秘钥和解密秘钥,一个是公开的,一个是非公开的私有秘钥。他们是一对,只有使用对应的秘钥才能解密

-

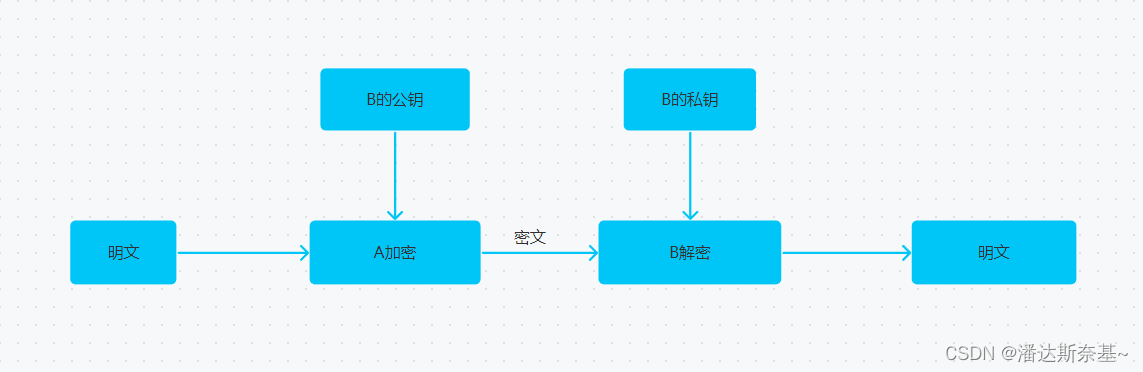

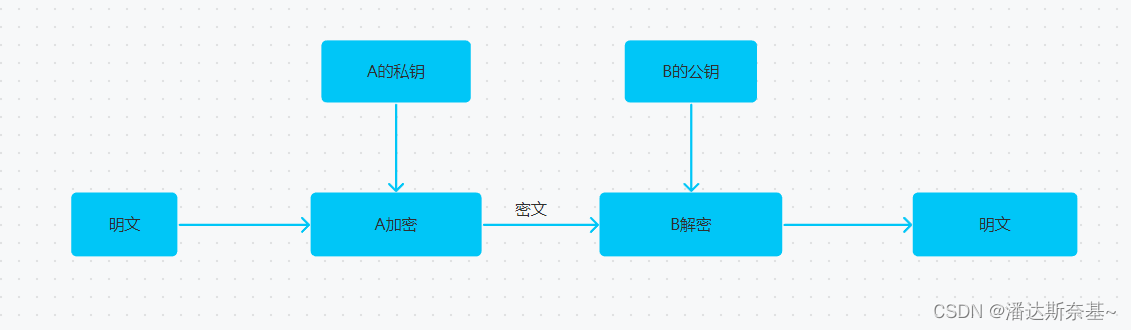

非对称加密有两个不同的体制:加密模型和认证模型

- 加密模型

- 认证模型

非对称加密算法的保密性较好,它消除了最终用户频繁交换秘钥的需要,但加密和解密花费时间长、速度慢,不适合与对文件加密,而只适用于对少量数据加密

代表算法:RSA,基于大素数分解的困难性

- 加密模型

信息摘要

-

Hash函数:输入一个长度不固定的字符串,返回一串固定长度的字符串,又称Hash值

-

单向Hash函数用户产生信息摘要

-

对于特定的文件,信息摘要是唯一的

-

在某一特定的时间内,无法查找经Hash操作后生成特定Hash值的原报文,也无法查找两个经Hash操作后生成相同Hash值的不同报文

-

在数字签名中,可以解决验证签名和用户身份验证、不可抵赖性的问题

-

MD2/MD4/MD5是被广泛使用的Hash函数,他们产生一种128位的信息摘要

-

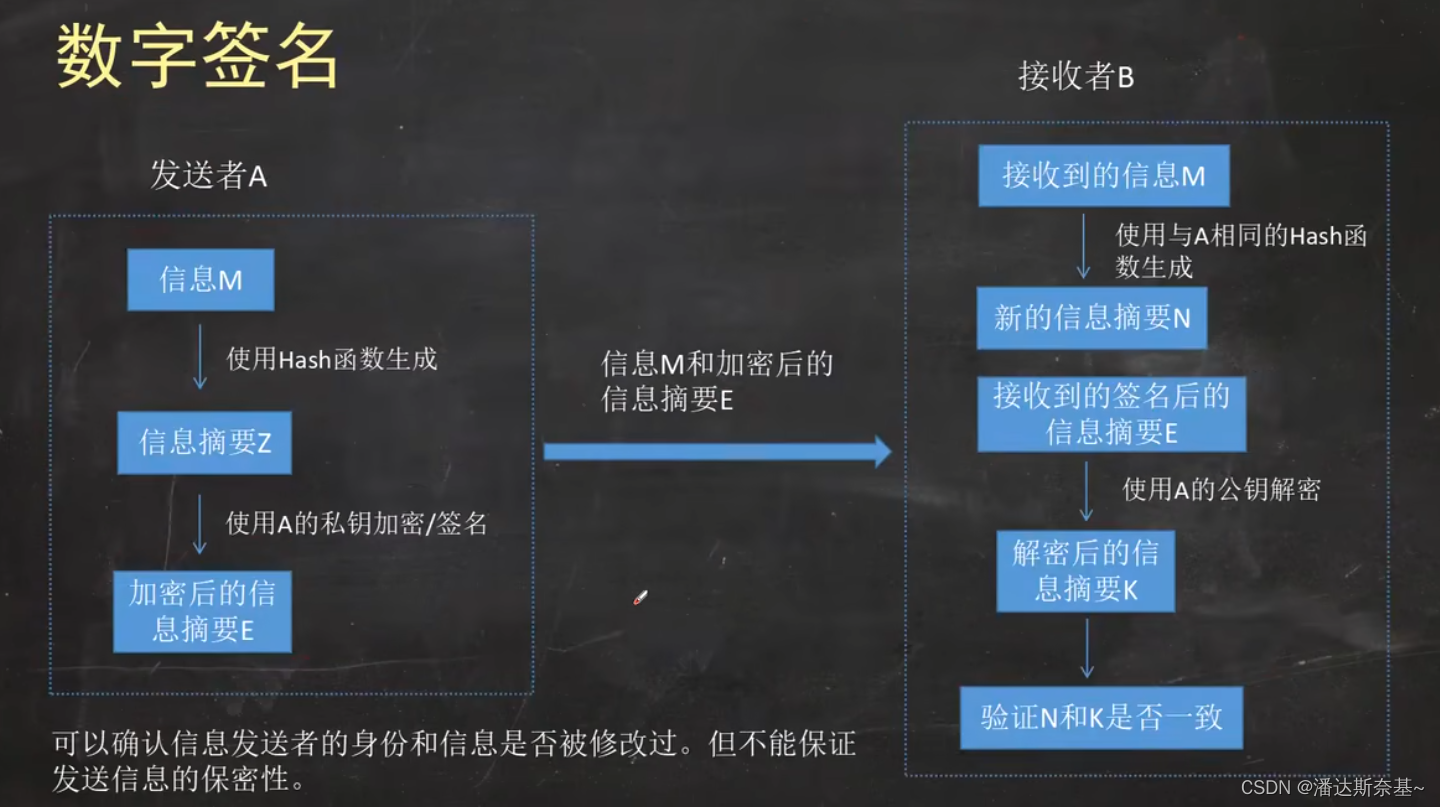

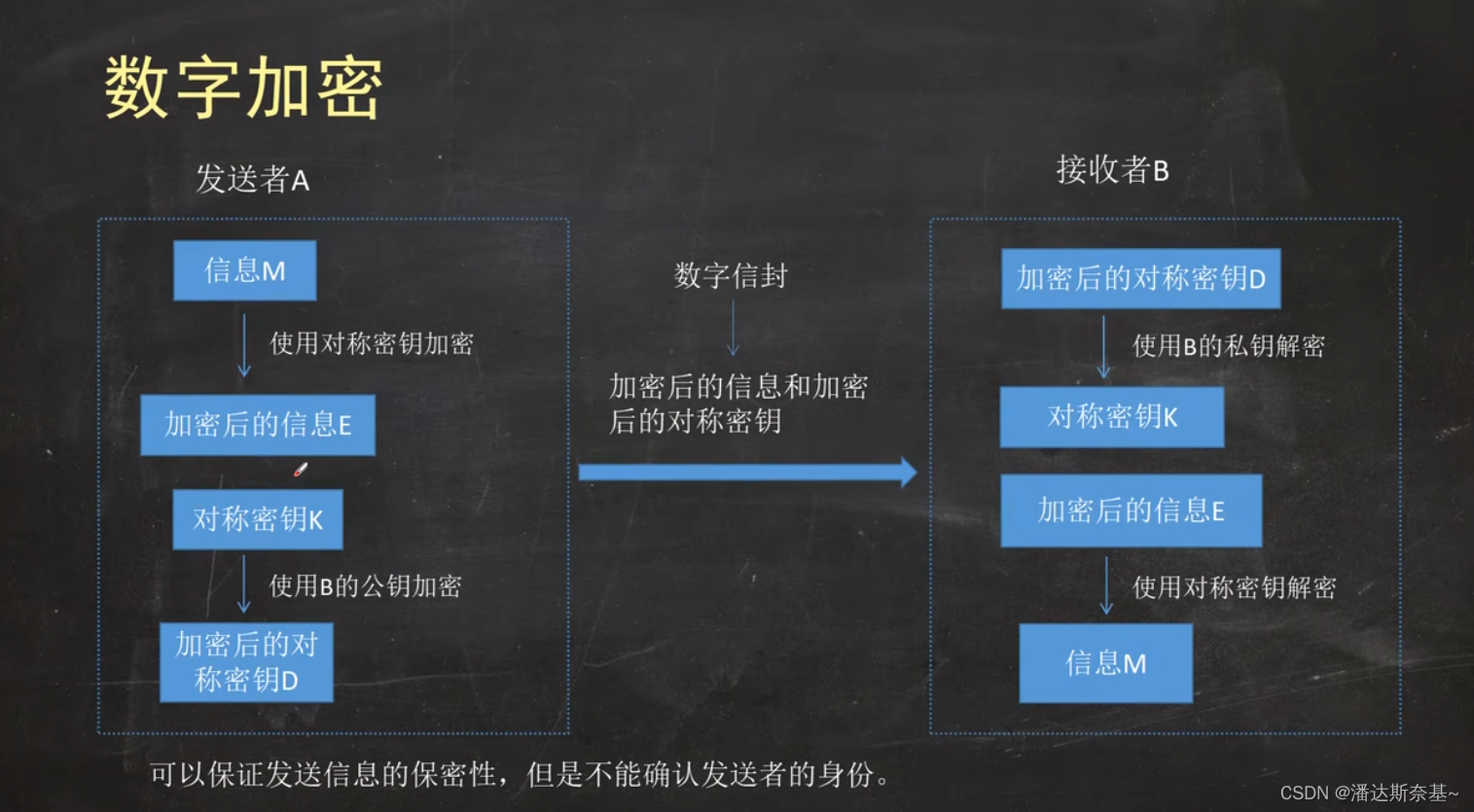

数字签名和数字加密的区别和联系

- 数字签名使用的是发送方的秘钥对,任何拥有发送方公开秘钥的人都可以验证数字签名的正确性。数字加密使用的是接收方的密钥对,是多对一的关系,任何知道接收方公开密钥的人都可以向接收方发送数据,但只有唯一拥有接收方私有秘钥的人才能对信息解密

- 数字签名只采用了非对称加密算法,他能保证发送信息的完整性、身份认证和不可否认性,但不能保证发送信息的保密性

- 数字加密采用了对称秘钥算法和非对称秘钥算法相结合的方法,他能保证发送信息的保密性

计算机可靠性

(1)串联系统的可靠性

R = R1*R2*R3*R4

(2)并联系统的可靠性

R = 1-(1-R1)-(1-R2)-(1-R3)....-(1-Rn)

436

436

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?