GPT写代码提升编程效率的能力是我去年就知道而且后来亲身体会过的。一位在亚马逊西雅图公司工作的软件高手跟我说,在他们的工作中每天都会使用大模型来编写代码,如果提问的时候描述精准的话,大模型给出的代码的准确率可以达到90%以上,经验丰富的工程师基于大模型给出的代码稍加调整就可以直接使用,原来5个小时的工作,现在可以1-2个小时搞定。

在我们2024年寒假练中,第一个平台 - 小脚丫FPGA核心板的项目,我们就会要求每一位同学都使用大模型来编写Verilog代码:

在前面三篇“大模型与电赛”的文章我介绍了大模型在方案设计方面的能力:

项目制定好,进入到实际的设计过程,就会遇到电路设计和代码编程方面的工作,由于在电赛中同学们多数使用实验室中现有的模块进行连接(如果准备充分的话),再考虑到GPT-4o的绘制电路图的能力还比较弱,在这里我们就不再电路设计进行介绍,不过我们确实可以让它就电路的结构描述一下,它提供的信息也足够我们使用。

今天主要介绍一下GPT在代码编程方面的能力,结合实际的题目来体验一下。

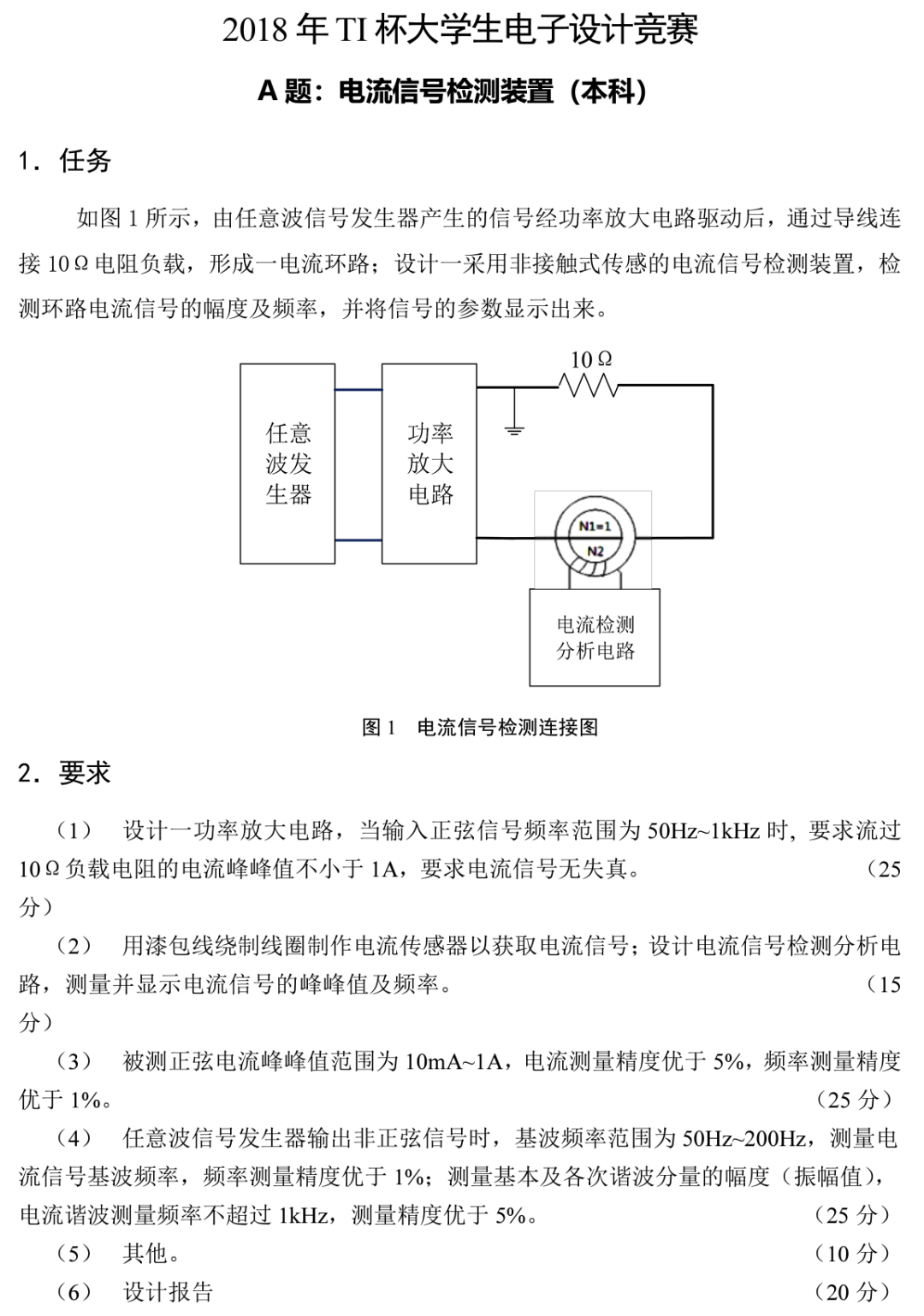

以2018年TI杯的A题为例:

方案设计

将PDF文件或截图上传给电子森林的AI助手,让它给出一个设计方案

AI助手给出的方案:

1. 系统总体方案

方案描述与选择:

-

信号源和功率放大电路:

-

任意波形发生器产生50Hz-1kHz的正弦信号,并通过功率放大器进行放大。选择线性功率放大器,以减少信号失真。

-

-

负载电阻:

-

采用10Ω的电阻作为负载,以形成电流环路,确保电流信号在0.1A到1A范围内。

-

-

非接触式电流传感器:

-

制作非接触式电流传感器,使用闭合式磁芯线圈感应负载中的电流。将漆包线缠绕在锰芯磁环上,形成感应线圈。

-

-

电流检测分析电路:

-

使用运算放大器和滤波电路对传感器输出信号进行放大与滤波。信号放大后送入单片机(如STM32)进行模数转换和数据分析。

-

-

数据显示模块:

-

通过LCD显示屏或串口通信,实时显示检测到的电流信号的峰值和频率等参数。

-

2. 理论分析与计算

电流测量方法:

-

传感器灵敏度计算:

-

选择合适匝数的漆包线绕制在锰芯磁环上,确保传感器能准确感应电流信号。

-

-

输出信号处理:

-

通过前端电路放大与滤波,提高信号的信噪比,避免干扰影响测量结果。

-

谐波分量测量方法:

-

FFT算法:

-

在STM32上实现快速傅里叶变换(FFT)算法,提取电流信号中的基本波及各次谐波的幅度(振幅值)和频率。

-

3. 电路设计

系统组成与电路设计:

-

功率放大电路:

-

选用OPA541等高精度运算放大器,保证输出信号线性。

-

-

传感器与信号调理电路:

-

使用锰芯磁环和漆包线制作电流传感器,通过运放进行信号放大。

-

滤波电路采用RC低通滤波器,截断高频噪声。

-

-

数据采集与处理电路:

-

运放输出接STM32的ADC通道,进行模数转换。

-

通过计算得到电流的峰值和频率,并进行FFT分析谐波成分。

-

-

显示电路:

-

LCD显示屏在I2C或SPI总线上连接,可实时显示电流信号的各项参数。

-

4. 测试方案与测试结果

测试方案:

-

频率响应测试:

-

使用任意波形发生器输出不同频率的信号,通过功率放大器驱动10Ω负载电阻,并记录相应的电流峰值与频率。

-

-

精度测试:

-

采用标准电流源,验证传感器在10mA到1A范围的测量精度,确保误差在5%以内。

-

-

数据处理测试:

-

根据所取样的数据,使用FFT算法,分离出基波和各次谐波的幅值,验证算法的准确性,确保频率测量精度在1%以内。

-

测试结果分析:

-

频率响应:

-

记录不同频率下电流信号的测量值,保证测量频率范围达到50Hz至1kHz。

-

-

精度分析:

-

对比标准电流源输出与测量值的误差。

-

-

谐波分析:

-

通过FFT算法的结果,比较各次谐波幅值,验证测量系统的准确性。

-

5. 设计报告结构及规范性

摘要: 简要描述设计任务、实施方法和最终结果。

报告正文:

-

引言:

-

设计背景、意义及目的。

-

-

系统设计:

-

详细描述系统硬件和软件设计方案。

-

-

理论分析:

-

解释电流传感和谐波分析的理论基础。

-

-

硬件电路设计:

-

提供详细电路原理图,标注关键参数。

-

-

软件设计:

-

描述数据采集、处理及显示的程序流程。

-

-

测试与结果:

-

记录测试过程与结果,分析误差并提出改进意见。

-

-

总结与展望:

-

总结设计成果,指出优缺点,并提出未来改进建议。

-

公式、图表、图片: 准确标注公式和参数,图表图片需清晰完整并附有说明。

功率放大器的电路设计

在这个方案中,它提出了使用OPA541来设计功率放大器,那我问它一下,这个功率放大器的电路该如何设计。

电子森林AI助手给出的电路:

下是一个简单的功率放大器电路原理图的示例。实际的功率放大器设计会根据具体需求和工作条件有所不同,但以下电路展示了基本的结构和原理:

基本功率放大器电路原理图

组件

-

OPA (运算放大器): 使用OPA541作为功率运放。

-

电阻器: 用于设定增益的反馈电阻。

-

输入与输出电容: 用于信号耦合和滤波。

VCC+

|

+|------------+

| |

(R3) (R4)

| |

Vin -----+----| |------|----------+

(C1) (R2) |

| | |

| +| |

+---|>|-----(+)- OPA541-(+)--- Vout

D1 ( )))

| / /

(R1) (GND) (GND)

|

(GND)

说明:

-

电源VCC+: 为OPA541提供正电源电压。

-

输入信号Vin: 通过耦合电容C1输入到运放的正端。

-

反馈网络:

-

电阻R3和R4设置运放的闭环增益。

-

电阻R1用于输入端的偏置。

-

二极管D1用作过压保护。

-

-

输出: 输出信号从OPA541的输出端Vout获得,并经过后续电容和电阻网络处理。

电路设计细节

1. 运算放大器(OPA541):

OPA541是一种高功率运算放大器,具有高输入阻抗和高电压增益特性,能够处理高功率输出。

2. 反馈网络:

-

使用电阻R3和R4配置运放的增益:增益 = 1 + (R4/R3)

-

反馈电路保证稳定性和线性度,提高放大器的性能。

3. 输入与输出耦合电容:

-

输入电容C1用于信号隔离,防止输入信号中的直流分量对运放偏置电压的影响。

-

输出端可以添加一个低通滤波器(电容和电阻网络),用于抑制高频噪声。

4. 电源和地:

-

提供适当的电源电压,确保运放能正常工作。

-

确保所有接地连接完好,避免地环路引起的噪声问题。

注意事项:

-

电路设计需要考虑功率放大器的工作电压、输入和输出电流、功率耗散等。

-

根据需求选择合适的电源电压和运放型号。

-

仔细计算各个元件参数,确保电路稳定工作并满足应用要求。

此电路示例是基础设计,实际应用中需要根据具体要求进行调整和优化。对于高功率输出需求,可以考虑增加散热设计和保护电路。

由此可见,GPT给出的电路更多是一个简单的文本构成的原理示意,附之丰富的文字说明,这些信息已经非常详尽,同学们完全可以理解并实施,如果还遇到问题,可以继续问它。

FFT分析谐波成分的C代码

在它给出的方案中,要用到FFT算法,分离出基波和各次谐波的幅值,这是一个非常常用的功能,我让GPT来给一段代码。

电子森林AI助手给出的C代码:

下面是一个使用FFT(快速傅里叶变换)分析信号谐波成分的C语言代码示例。这个代码基于GNU Scientific Library (GSL) 库进行FFT计算,你需要在使用前确保已安装GSL。

#include <stdio.h>#include <stdlib.h>#include <math.h>#include <gsl/gsl_fft_real.h>#include <gsl/gsl_fft_halfcomplex.h>// 定义信号长度#define N 1024// 主函数int main(void) { double data[N]; // 输入数据数组 double freq[N]; // 频率数组 double sampling_rate = 1000.0; // 采样率(可以根据实际情况调整) // 生成示例输入信号(例如正弦波和谐波) for (int i = 0; i < N; ++i) { double t = i / sampling_rate; data[i] = sin(2 * M_PI * 50 * t) + 0.5 * sin(2 * M_PI * 150 * t); // 基波50Hz,3次谐波150Hz } // 进行FFT转换 gsl_fft_real_workspace *work = gsl_fft_real_workspace_alloc(N); gsl_fft_real_wavetable *real = gsl_fft_real_wavetable_alloc(N); gsl_fft_real_transform(data, 1, N, real, work); gsl_fft_real_wavetable_free(real); gsl_fft_real_workspace_free(work); // 计算频谱 freq[0] = data[0]; for (int i = 1; i < (N / 2); ++i) { double real = data[2 * i]; double imag = data[2 * i + 1]; freq[i] = sqrt(real * real + imag * imag); } freq[N / 2] = data[1]; // Nyquist频率 // 打印频谱 for (int i = 0; i < (N / 2); ++i) { printf("Frequency = %f Hz, Amplitude = %f\n", i * sampling_rate / N, freq[i]); } return 0;}解释

-

生成示例信号:

-

生成一个包含基波50Hz和谐波150Hz的示例信号。

-

-

FFT变换:

-

使用GSL函数进行实时FFT变换。

-

-

计算频谱:

-

将FFT结果转换为频谱,计算每个频率点的幅值。

-

-

打印频谱:

-

打印频谱,显示频率和对应的幅值。

-

注意事项

-

依赖库:

-

在编译时需要链接GSL库。例如:

gcc -o fft_example fft_example.c -lgsl -lgslcblas -lm。

-

-

信号处理:

-

实际使用中,输入信号应根据实际需求进行适当预处理(例如滤波、去噪等)。

-

-

输出结果:

-

此代码将基波和谐波的频率和幅度打印到控制台,实际使用时可以根据需求将结果存储或进一步处理。

-

通过这个代码,你可以完成基本的信号谐波成分分析,进一步按照实际需求进行细化和优化。

生成任意波形的C代码

在很多项目中都会遇到使用MCU的程序来生成任意波形,在这个题目中也需要产生50Hz到1KHz的正弦波信号,让GPT来写一段:

电子森林AI助手给出的代码:

为了生成50Hz至1kHz范围内的正弦波信号,可以使用DAC(数模转换器)在STM32单片机上实现。以下是一个示例代码,仅供参考。本例假设读者具备一些基本的STM32开发知识,并配置了硬件,如DAC和定时器等。

初始化部分

#include "stm32f4xx_hal.h"#include "math.h"// DAC输出缓冲区大小#define DAC_BUFFER_SIZE 100DAC_HandleTypeDef hdac;TIM_HandleTypeDef htim6;uint16_t dac_buffer[DAC_BUFFER_SIZE];// 初始化DACvoid DAC_Init(void) { __HAL_RCC_DAC_CLK_ENABLE(); hdac.Instance = DAC; HAL_DAC_Init(&hdac); DAC_ChannelConfTypeDef sConfig; sConfig.DAC_Trigger = DAC_TRIGGER_T6_TRGO; sConfig.DAC_OutputBuffer = DAC_OUTPUTBUFFER_ENABLE; HAL_DAC_ConfigChannel(&hdac, &sConfig, DAC_CHANNEL_1);}// 初始化定时器void TIM6_Init(uint32_t frequency) { __HAL_RCC_TIM6_CLK_ENABLE(); htim6.Instance = TIM6; htim6.Init.Prescaler = HAL_RCC_GetPCLK1Freq() / (DAC_BUFFER_SIZE * frequency) - 1; htim6.Init.CounterMode = TIM_COUNTERMODE_UP; htim6.Init.Period = DAC_BUFFER_SIZE - 1; htim6.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1; HAL_TIM_Base_Init(&htim6); TIM_MasterConfigTypeDef sMasterConfig; sMasterConfig.MasterOutputTrigger = TIM_TRGO_UPDATE; sMasterConfig.MasterSlaveMode = TIM_MASTERSLAVEMODE_DISABLE; HAL_TIMEx_MasterConfigSynchronization(&htim6, &sMasterConfig);}// 填充DAC缓冲区,生成正弦波void Generate_Sine_Wave(uint32_t frequency) { for (int i = 0; i < DAC_BUFFER_SIZE; i++) { dac_buffer[i] = (uint16_t)(((sin(2 * M_PI * i / DAC_BUFFER_SIZE) + 1) / 2) * 4095); // 正弦波数据,12位DAC }}// 启动DACvoid Start_DAC(void) { HAL_DAC_Start_DMA(&hdac, DAC_CHANNEL_1, (uint32_t*)dac_buffer, DAC_BUFFER_SIZE, DAC_ALIGN_12B_R); HAL_TIM_Base_Start(&htim6);}主函数

int main(void) { HAL_Init(); SystemClock_Config(); // 确保系统时钟配置正确 DAC_Init(); TIM6_Init(1000); // 设置初始频率,例如1000Hz Generate_Sine_Wave(1000); // 生成正弦波形 Start_DAC(); // 主循环 while (1) { // 可根据需要调节频率 uint32_t new_frequency = 500; // 示例:将频率更改为500Hz TIM6_Init(new_frequency); Generate_Sine_Wave(new_frequency); }}注意事项

-

硬件连接: 确保DAC输出引脚正确连接到测量电路或负载。

-

库版本: 确保STM32 HAL库的版本和芯片型号正确。

-

定时与同步: 根据具体的STM32系列芯片,调整定时器和中断优先级设置。

通过以上代码,可以生成频率在50Hz至1kHz范围内的正弦波信号,并依据需要动态调整频率。

这段程序是假设了MCU内部有DAC,在多数情况下,MCU内部没有DAC,也没外部的DAC,其实可以使用PWM + LPF的方式同样生成正弦波信号,让GPT也来生成一段程序:

电子森林AI助手的代码:

如果你的MCU没有内置DAC,可以使用PWM(脉宽调制)来生成从50Hz到1kHz的正弦波信号。通过调整PWM的占空比,可以模拟出一个近似的正弦波。

下面是使用PWM生成正弦波信号的步骤和示例C代码:

步骤概述:

-

计算正弦波表: 预先计算一个正弦波的样本数组,通过这些样本来设置PWM的占空比。

-

设置定时器: 使用定时器中断来定期更新PWM的占空比。

-

配置PWM: 根据正弦波的表格值更新PWM占空比。

示例代码(假设使用STM32 MCU):

预先计算一个正弦波的样本数组

#include <math.h>#define PI 3.14159265358979323846#define PWM_RESOLUTION 256 // 一周期分成256个点#define PWM_TABLE_SIZE 256 // 生成256个占空比值uint8_t sine_table[PWM_TABLE_SIZE];void generate_sine_table() { for (int i = 0; i < PWM_TABLE_SIZE; ++i) { sine_table[i] = (uint8_t)((sin(2 * PI * i / PWM_RESOLUTION) + 1) * 127.5); // 0-255 范围 }}设置定时器和PWM

以下代码假设使用STM32 HAL库:

#include "stm32f4xx_hal.h"TIM_HandleTypeDef htim2;TIM_OC_InitTypeDef sConfigOC;/* 定时器中断处理程序 */void TIM2_IRQHandler(void) { static uint8_t index = 0; // 更新PWM占空比 __HAL_TIM_SET_COMPARE(&htim2, TIM_CHANNEL_1, sine_table[index]); // 更新数组索引 index = (index + 1) % PWM_TABLE_SIZE; // 清除中断标志 __HAL_TIM_CLEAR_IT(&htim2, TIM_IT_UPDATE);}/* 初始化定时器 */void Timer_Init() { __HAL_RCC_TIM2_CLK_ENABLE(); htim2.Instance = TIM2; htim2.Init.Prescaler = ((SystemCoreClock / 2) / (PWM_RESOLUTION * 1000)) - 1; // 1 kHz htim2.Init.CounterMode = TIM_COUNTERMODE_UP; htim2.Init.Period = PWM_RESOLUTION - 1; htim2.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1; HAL_TIM_PWM_Init(&htim2); sConfigOC.OCMode = TIM_OCMODE_PWM1; sConfigOC.Pulse = 0; sConfigOC.OCPolarity = TIM_OCPOLARITY_HIGH; sConfigOC.OCFastMode = TIM_OCFAST_DISABLE; HAL_TIM_PWM_ConfigChannel(&htim2, &sConfigOC, TIM_CHANNEL_1); HAL_TIM_Base_Start_IT(&htim2); HAL_TIM_PWM_Start_IT(&htim2, TIM_CHANNEL_1); HAL_NVIC_SetPriority(TIM2_IRQn, 1, 0); HAL_NVIC_EnableIRQ(TIM2_IRQn);}/* 主函数 */int main(void) { HAL_Init(); SystemClock_Config(); // 配置系统时钟 generate_sine_table(); Timer_Init(); while (1) { // 主循环 }}解释

-

生成正弦波表: 使用

sin()函数生成一个包含正弦波样本点的数组sine_table。 -

配置定时器: 初始化定时器,并设置定时器的中断频率为所需的正弦波频率(此处以1kHz为例)。

-

配置PWM: 初始化PWM并设置占空比为数组中的值,每次定时器中断时更新占空比。

-

主函数: 调用

generate_sine_table()生成正弦波表格,并初始化定时器。进入主循环后,定时器中断会定期更新PWM的占空比,输出近似的正弦波信号。

注意:实际的定时器配置和GPIO初始化会因具体的MCU型号而不同,具体的时钟配置也需要根据你的应用要求进行调整。

上述的这个题目展示了大模型写MCU代码的能力,在FPGA的项目中写Verilog代码如何?

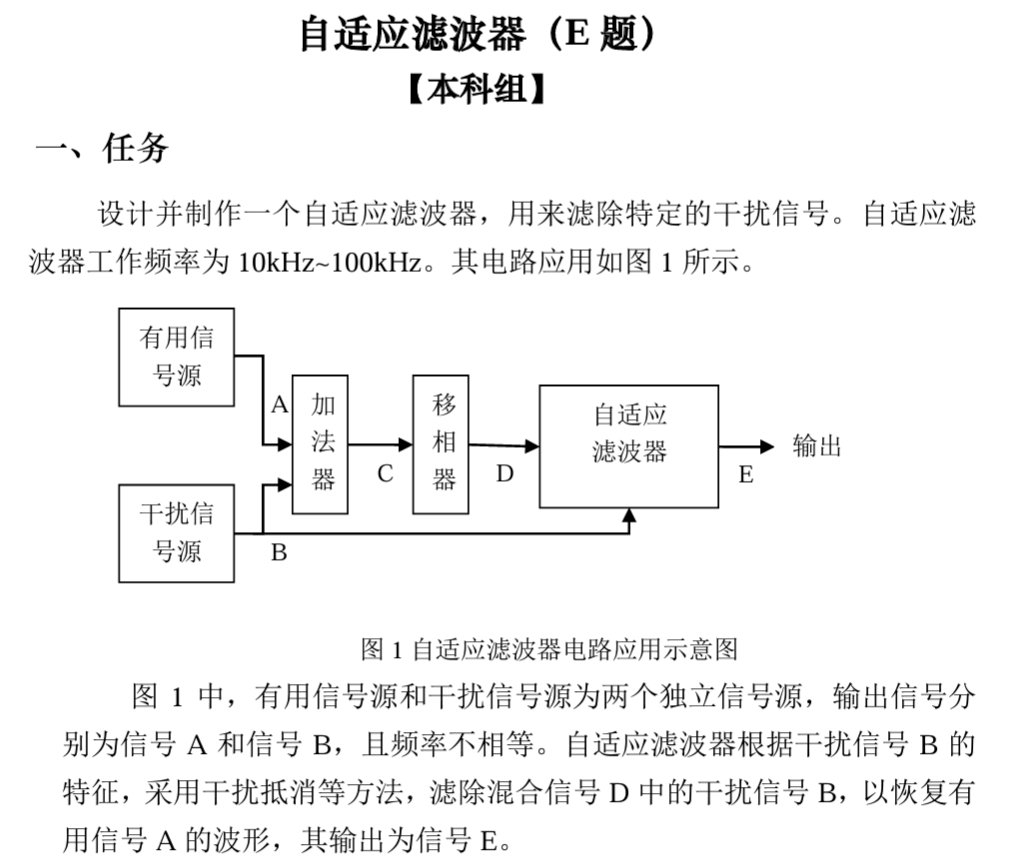

以2017年的国赛E题为例

将题目上传给电子森林的AI助手,AI助手给出的设计方案:

使用FPGA实现自适应滤波器的设计方案

一、任务与要求概述

任务

设计并制作一个自适应滤波器,用来除去特定的干扰信号。自适应滤波器工作频率为10kHz-100kHz,其他信号源和干扰信号源为两输入独立信号源,输出信号分别为信号A和信号B。根据图1中的系统结构,自适应滤波器根据干扰信号B的特征,采用干扰消除的方法,滤除组合信号D中的干扰信号B,以恢复有用信号A的波形,其中输出值为信号E。

要求

-

加法器实现C=A+B,其中信号A和B的峰值均为1~2V,频率范围为10kHz-100kHz,预留便于测量的输入输出端口。

-

移相器在频率范围内10kHz-100kHz内的各个频率的移相,实现0~180°可插拨式移相,将相偏差控制在±1.0度。

-

自适应滤波器有两个输入端口和一个输出端口。当干扰信号B为正弦信号,且频率稳定在100Hz时,输出信号E的幅度能够恢复信号A的波形,信号E与信号A的频率无关,误差不超过10%。

二、设计方案

1. FPGA总体架构

本设计基于FPGA(如Xilinx Spartan或Altera Cyclone),系统包括以下模块:

-

信号源模块:产生有用信号A和干扰信号B。

-

加法器模块:将信号A和信号B相加,得到组合信号C。

-

移相器模块:对干扰信号B进行0~180度移相,生成移相信号。

-

自适应滤波器模块:自适应滤波器根据干扰信号进行调整,滤除信号D中的干扰成分,输出滤波后信号E。

2. 模块设计

信号源模块

module signal_source( output reg [15:0] sig_A, output reg [15:0] sig_B);// 产生10kHz到100kHz的正弦信号,并添加事先设定的干扰信号Bendmodule加法器模块

module adder ( input wire [15:0] A, input wire [15:0] B, output wire [15:0] C); assign C = A + B;endmodule移相器模块

使用NCO(Numerically Controlled Oscillator)方法对干扰信号B进行移相控制。

module phase_shifter ( input wire clk, input wire [15:0] B, input wire [7:0] phase_shift, // 0~180度对应0~256 output wire [15:0] shifted_B); reg [15:0] phase_accum = 0; always @(posedge clk) begin phase_accum <= phase_accum + phase_shift; end assign shifted_B = B * $cos(phase_accum); // 数据类型根据使用FPGA平台处理endmodule自适应滤波器模块

自适应滤波器模块可使用LMS(Least Mean Square)算法,通过硬件电路实现滤波器的自适应调整。

module adaptive_filter ( input wire clk, input wire reset, input wire [15:0] C, input wire [15:0] shifted_B, output wire [15:0] E);// LMS自适应滤波算法的实现细节,包含权值更新、误差计算和信号调整// 省略实现细节endmodule3. 系统集成

将上述模块集成在一起,形成完整的自适应滤波器系统。

module adaptive_filter_system ( input wire clk, input wire reset, input wire [15:0] sig_A, input wire [15:0] sig_B, input wire [7:0] phase_shift, output wire [15:0] sig_E); wire [15:0] sig_C; wire [15:0] sig_shifted_B; // 实例化加法器 adder add_inst ( .A(sig_A), .B(sig_B), .C(sig_C) ); // 实例化移相器 phase_shifter phase_inst ( .clk(clk), .B(sig_B), .phase_shift(phase_shift), .shifted_B(sig_shifted_B) ); // 实例化自适应滤波器 adaptive_filter filter_inst ( .clk(clk), .reset(reset), .C(sig_C), .shifted_B(sig_shifted_B), .E(sig_E) );endmodule三、总结

本设计基于FPGA实现了一个自适应滤波器系统,利用加法器、移相器和自适应滤波器模块,通过LMS算法对输入的组合信号进行自适应滤波,从而有效地滤除干扰信号B,提高系统的抗干扰能力。此设计方案易于硬件实现,频率范围在10kHz到100kHz,满足设计要求。

估计由于篇幅限制,它没有给出自适应滤波器的详细代码,我再问它一下:

“请再给出使用LMS算法实现自适应滤波器的代码”

电子森林AI助手给出的代码:

下面是使用LMS(Least Mean Squares)算法实现自适应滤波器的Verilog代码。该设计基于前面提供的自适应滤波器模块结构,并添加具体的LMS算法实现。

LMS 自适应滤波器 Verilog 代码

参数说明:

-

DATA_WIDTH: 数据宽度,默认16位。 -

MU: 步长因子,用于控制权值更新速度。

module adaptive_filter #( parameter DATA_WIDTH = 16, parameter MU = 16'h0001 // 步长因子) ( input wire clk, // 时钟信号 input wire reset, // 复位信号 input wire signed [DATA_WIDTH-1:0] in_C, // 输入信号 C (组合信号) input wire signed [DATA_WIDTH-1:0] in_B, // 输入移相信号 B output reg signed [DATA_WIDTH-1:0] out_E // 输出信号 E); // 滤波器权值 reg signed [DATA_WIDTH-1:0] weight; // 滤波器输出 wire signed [DATA_WIDTH-1:0] filter_out; // 误差信号 wire signed [DATA_WIDTH-1:0] error; // 滤波器输出计算 assign filter_out = in_B * weight; // 误差计算 assign error = in_C - filter_out; // LMS权值更新 always @(posedge clk or posedge reset) begin if (reset) begin weight <= 0; end else begin // 更新权值:w(n+1) = w(n) + μ * error * x(n) weight <= weight + ((MU * error * in_B) >>> (DATA_WIDTH - 1)); end end // 输出信号计算 always @(posedge clk or posedge reset) begin if (reset) begin out_E <= 0; end else begin out_E <= error; end endendmodule解释:

-

滤波器权值 (weight): 初始化为0,并不断根据误差信号进行更新。

-

滤波器输出 (filter_out): 计算当前滤波器权值和输入移相信号的乘积。

-

误差信号: 计算组合信号

in_C与滤波器输出filter_out之差。 -

权值更新: 使用LMS算法,下一个权值等于当前权值加上误差信号、步长因子和输入信号乘积的调整值。

-

输出信号 (out_E): 输出当前的误差信号。

通过持续调节权值,LMS自适应滤波器能够有效消除输入信号中的干扰成分,使输出信号尽可能接近有用信号。

大模型的局限及意义

使用过大模型写代码的同学们都知道,我们不能完全相信大模型写出来的代码,毕竟它是基于互联网上各种项目中不同层次的代码分享者的作品(良莠不齐)总结出来的,而且它的理解也不是100%,因此肯定会有错误。但它至少提供给了我们:

-

一个完整的框架

-

一套规范的代码结构

-

我们可以不断拷问它,它能不厌其烦、而且很谦卑地帮我们修正

想一下,如果真的能实现我们让它写啥,它就能写啥,而且都是准确的,那我们自己做这件事情的意义在哪里?这个电赛是不是可以取消了?

所以,它是一个非常有用的工具,就像我们使用的交通工具,还需要我们自己学会驾驭,但用上它,总比自己走路快很多。

同学们不妨在备战电赛的过程中多体验它,找到“驾驭它”的感觉,在赛前成长为“开GPT的老司机”,在考试的过程中一定会取得很好的成绩。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?