本文章是在学习计算机组成原理过程中个人感觉需要理解与记忆的问题,还有一些在学习过程中自己产生的疑问以及解答,本文章可能排版不良,精力有限,还请见谅

第一章:

(1)MAR的位数对应着存储单元的个数,这是为什么那?

因为:

存储体是由多个存储单元构成,存储单元是由多个存储元构成(在地址进行寻址过程中“+1”是+的一个存储单元比如(程序计数器pc中的+1))而且MAR是地址寄存器。

MAR是10位的话 则有个存储单元

(2)地址总线的条 数与内存单元的个数有关与MAR位数相同

(3)数据总线与存储字长相同 ,与MDR位数也相同

(4)MDR是数据寄存器,存储的是一个存储单元内的数据,所以位数与存储单元中存储元件(bit)的个数相同

(5)pc的位数与主存的容量相关

因为 主存容量=存储单元的个数*存储字长

(6)在存储中的时候k,m,g是以2的幂次

在速度与频率中是以10为幂次(且在本场景下为k(小k))

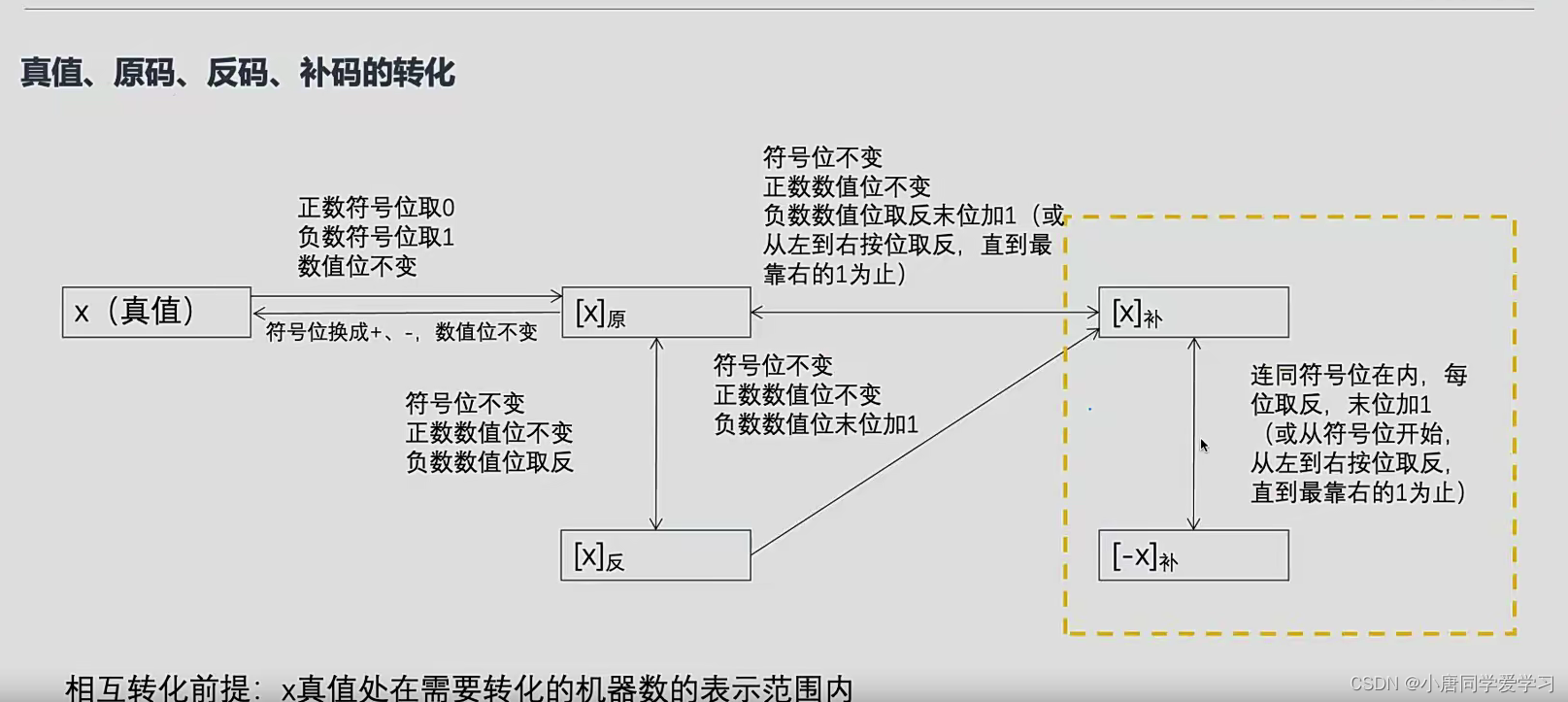

第二章:

(1)机器存储的机器数

整数原码:

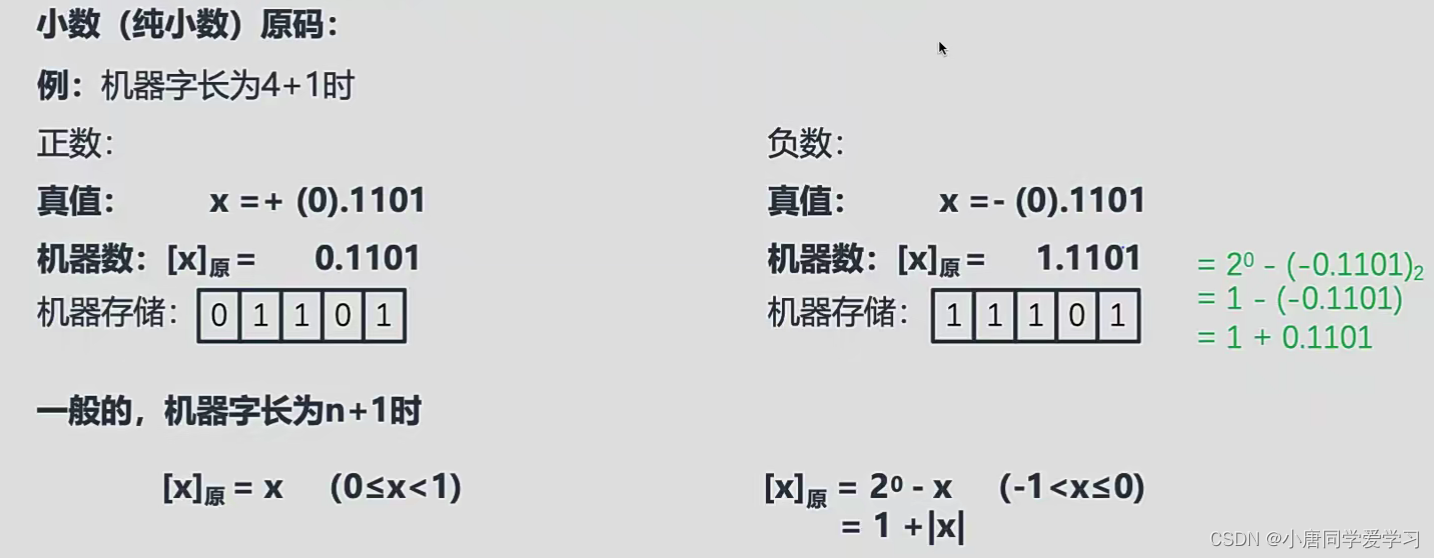

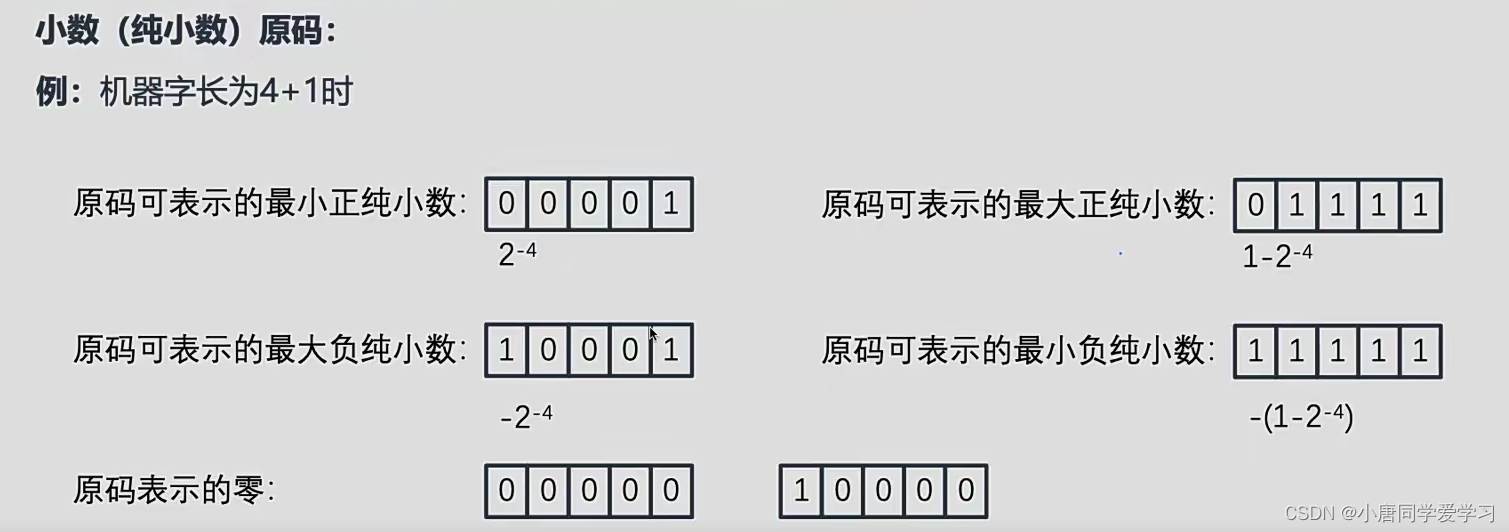

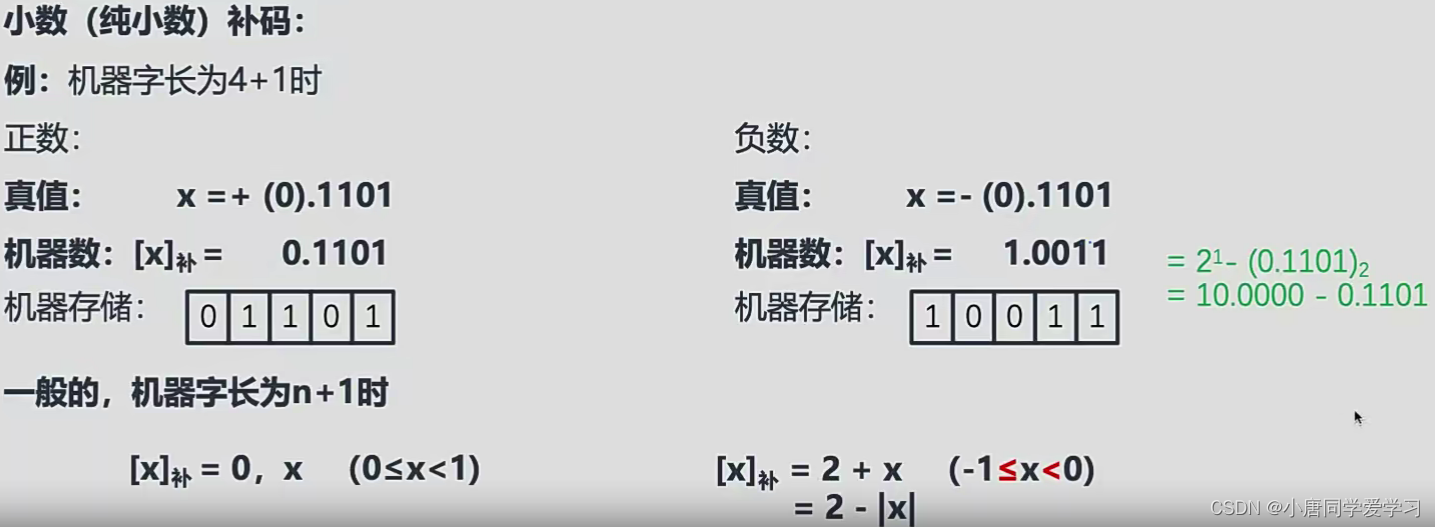

纯小数原码:

(2)0的原码有两种表示方式(+0,-0)

(3)在机器字长为n位时,补码可表示的最小负整数时

因为:

在n位二进制补码表示法中,最高位是符号位,0表示正数,1表示负数。因此,在n位补码表示法中,对于有符号整数,最小的负数是将符号位设为1,其他各位设为0,即100...00100...00,其值为

(个人理解 正数的最大数值是-1 ,负数的范围比正数大1,所以复数的最小数为

而且补码与它绝对值的原码相同, 因为补码0只有一种表示方式)

(4)-8的补码为什么是1000

-8的补码是1000,因为在计算机中,负数通常使用补码来表示。

首先,我们需要了解补码的定义。正整数的补码与其二进制原码相同,而负整数的补码是将其对应的正整数的补码取反后再加1。

对于-8这个负整数,它的绝对值的二进制原码是 1000,其中最高位的1表示符号(0表示正数,1表示负数)。现在要求-8的补码,我们需要先将其绝对值的二进制原码取反得到 0111,然后加上1得到 1000,即为-8的补码。

因此,-8的补码是 1000。

(5)移码是对真值的操作,给真值加一个偏移量为 机器字长为(n+1)

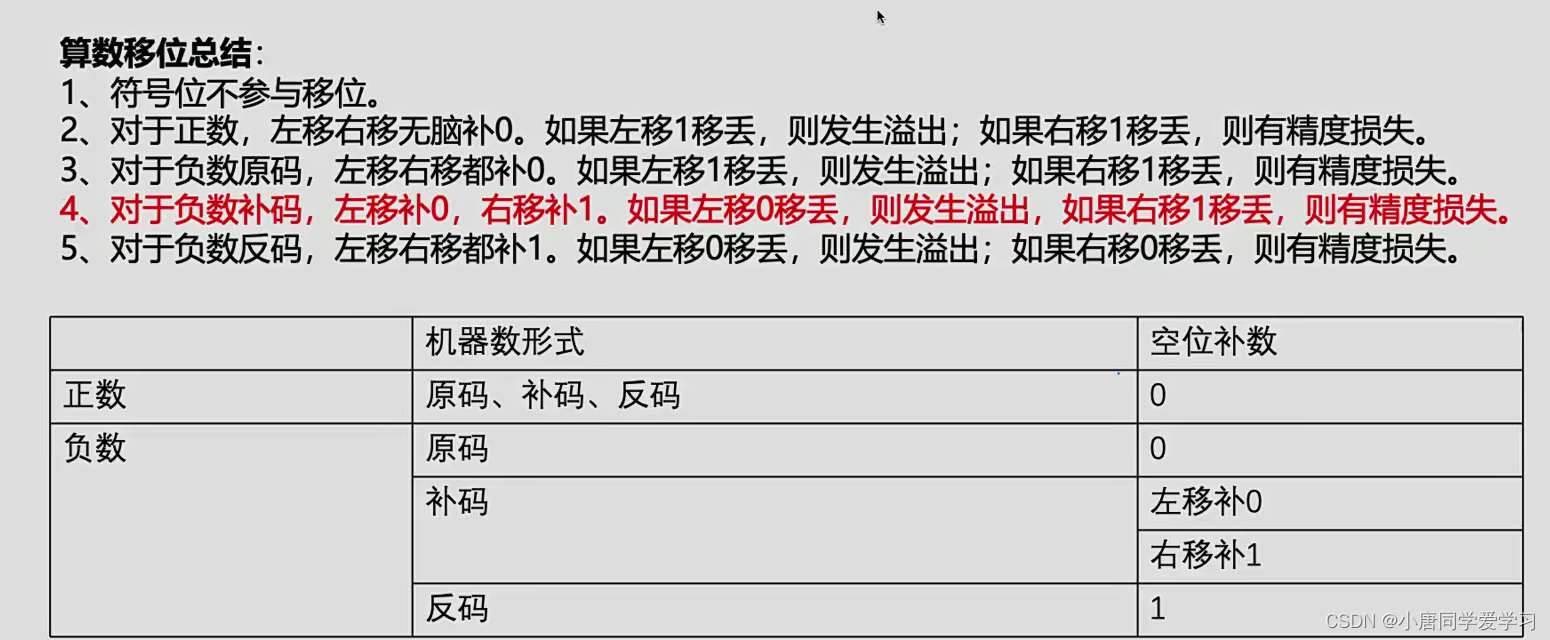

移位操作:

加减法的四大标志位:

OF:为什么最高位的进位异或次高位的进位 表示溢出?

溢出只有两种情况(只对有符号数有效)

(1)正数+正数=符号位为1的数

(2)负数+负数=符号位为0的数

情况(1):当正数加正数时 两数的最高位都为0 则最高位进位为0 如果次高位进位为1 则结果为1(负数),发生溢出 此时异或结果为1

情况(2):当两个负数相加的时候,两数的最高位都为1 则最高位的进位必为1 如果次高位进位为0,则最终结果为0 (正数),发生溢出,此时异或结果为1】

SF:判断有符号数的正负性,对无符号数没有意义

SF:0 正数

SF:1 负数

ZF:表示结果是否为0

ZF: 1 结果为0

ZF:0 结果不为0

CF:是表示无符号数在进行加减法的过程中是否发生进位或者借位(加法是进位,减法是借位)。

CF=最高位产生的进位 异或 sub(加减法控制器)

CF:1 表示进位或者借位

CF:0 表示不发生进位或者借位

原码加减交替法最后余数的处理:

在学习原码出发的时候,学到加减交替法,到最后产生了疑惑。

那就是最后的余数的处理。它的符号到底与什么有关?

后来发现原码的加减交替法是数值位与符号位分开处理的,则在数值计算的过程中,商和余数的符号位一定为0 ,最后根据除数与被除数的符号确定商与余数的符号。(最后的余数如果为负,则需要商0并且加上[|y|]的补码)最后一次不需要移位(为什么说i它最后一位不需要进行移位那 因为不恢复余数法的思想就是2*a+b直接进行下次运算 最后的结果是不需要移位的)

在最后结果,余数与被除数符号一致

n位数值位,则可能加减n+1次或者n+2次 移位n次

补码加减交替法总结:

补码的加减交替法是带符号位进行运算,最后的商与余数也是补码

执行加或减是根据除数与被除数的符号进行判断的:

同号进行减操作,异号执行加操作

由余数与除数的符号来判断商1还是0:

同号:商1,左移减去除数

异号:商0,左移加上除数

商的末尾一定商1 不用进行矫正

原码加减交替法与补码加减交替法对比:

在判断数值是否溢出的时候引入双符号位

在判断数值是否溢出的时候引入双符号位

01:表示正溢出:两个正数相加,得到的结果超出最大正范围

10:表示负溢出:两个负数相加,得到的结果超出最小负范围

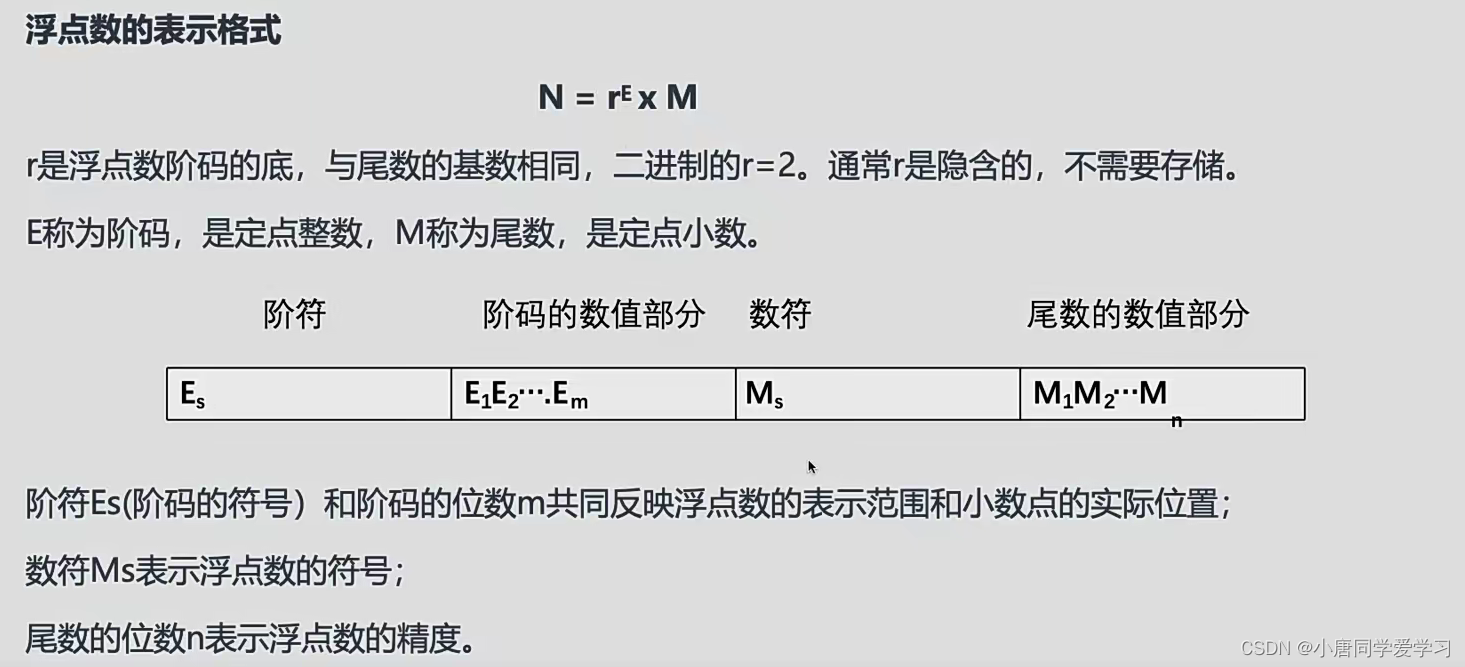

浮点数的表示与计算:

浮点数的规格化:

左规格化:当尾数的最高数值位不是有效位,则左规,进行消0处理(对应的阶码减一),左规可以进行多次

右规格化:当尾数有效位进到小数点之前的时候,将尾数进行右规格化(右移一位),只需进行一次

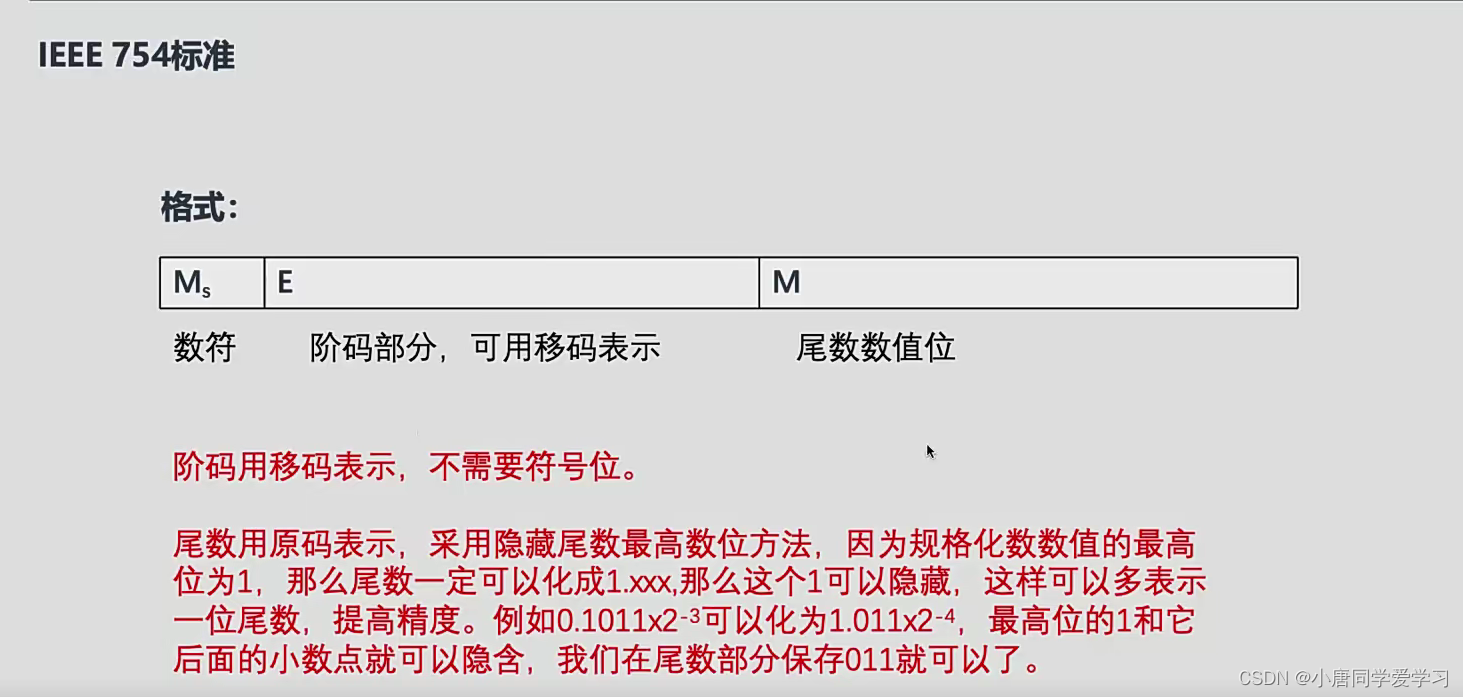

在规格化过程中,常用的是IEEE754标准,

在IEEE754标准中会用到移码,对移码中的偏移值产生了疑问?

偏移值定义了在移码中的正零点的位置,偏置值是一个固定的整数,用于表示移码中的零点,常用的偏置值为

eg:

在一字节(5bite)的移码表示中,偏置值为127。这意味着表示值为0的移码将是01111111(即2^7 - 1),而表示正整数的移码将从10000000到11111111,负整数则从00000000到01111111。

机器字长:CPU进行一次整数运算所能处理的二进制数据的位数(通常与ALU直接相关)

存储字长:一个存储单元中的二进制代码的位数(通常和MDR位数相同)

也就是存储字长的位数代表一个存储单元可以可以表示数据的上下限

10000---

M与MB 的区别

1m字表示1000000个字

1mb表示2的20次方的B

存储系统:

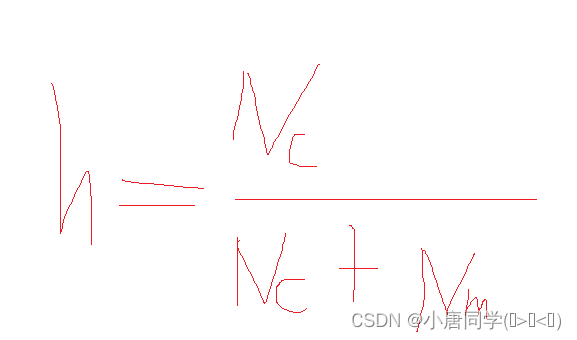

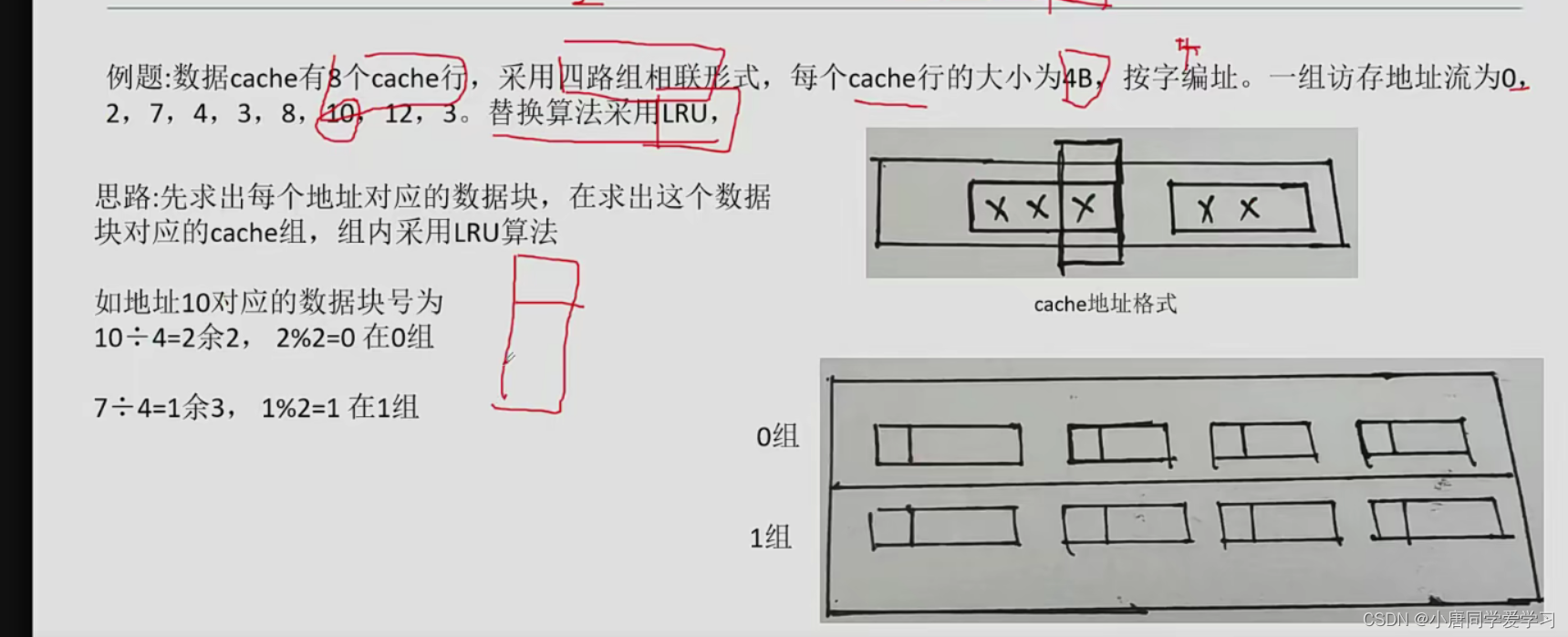

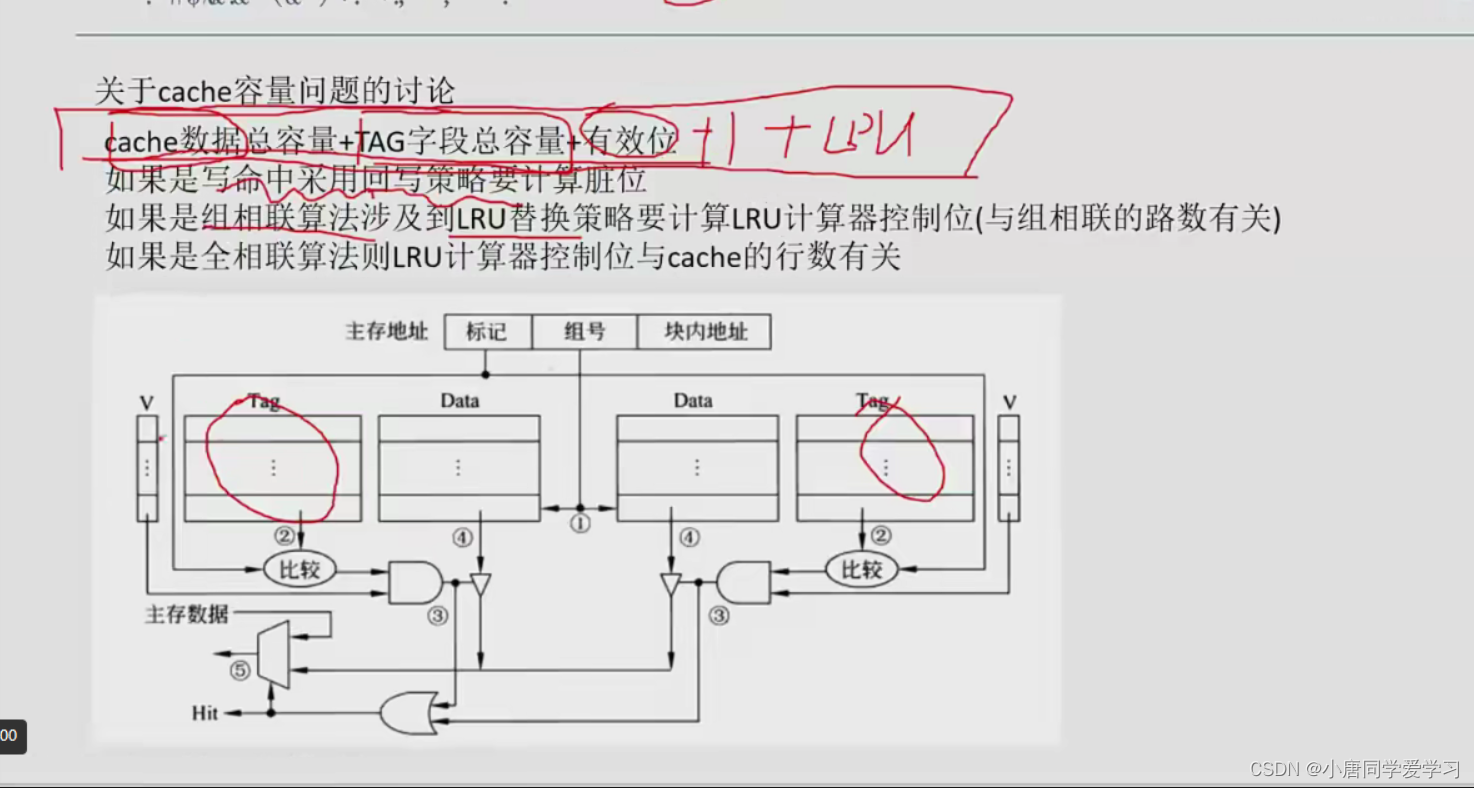

cache命中率问题:

cache(高速缓冲存储器)中的数据就是主存的一个子集,CPU访问存储器时会先访问cache,如果cache没有找到需要的数据,就会去主存找,于是引入cache命中率,用来描述在cache完成存取的占比,我们希望数据都可以在cache直接找到,所以这个命中率越接近1越好。

Nc:在命中过程中cache命中的次数

Nm:在命中过程中主存完成存取的次数

h:表示命中率

ta:表示平均存取时间

tc:表示命中花费的时间

tm:表示在主存中存取花费的时间

计算地址线和数据线的个数:

存储容量: 存储容量是主存中能存放二进制代码的总位数,即存储容量=存储单元个数×存储字长(每个存储单元的位数),也可用字节总数来表示: 存储容量=存储单元个数*存储字长/8

地址线: 存储单元的个数=2^地址线的条数 (地址线是用来传输地址信息用的

数据线: 数据线确定存储字长,数据线的条数=字长的位数。(相当于一次计算所能传输的最大位数(计算机的位数))

eg:

某计算机字长为32位,其存储容量为16M×32位,它的地址线和数据线的总和是?

先进行转换单位为字节Byte

16m=16*1 024(2的10次方)=16777216(B)

32bit=4Byte

数据容量=16777216*4=67108864(64M B=2的26次方)

所以:数据线32条 地址线26条(因为相当于需要26位 每位接一个地址线)

DRAM一次完整的刷新过程需要占用几个存储周期

DRAM的一次完整刷新过程通常需要占用一个存储周期。具体来说,DRAM需要在其存储单元之间循环刷新,并检查每个存储单元的电荷状态以确保它们不会漏电。这个刷新周期通常是以毫秒为单位的,但是它通常会被分成许多小的操作,每个操作需要一个存储周期来完成。因此,可以说DRAM的一次完整刷新过程需要占用一个存储周期。

在408考试中交叉编址方式就是低位交叉

计算机指令地址并不是物理地址(内存地址)而是逻辑地址(外存地址),执行指令的时候通过硬件将指令中的逻辑地址转换成主存的物理地址

指令系统:

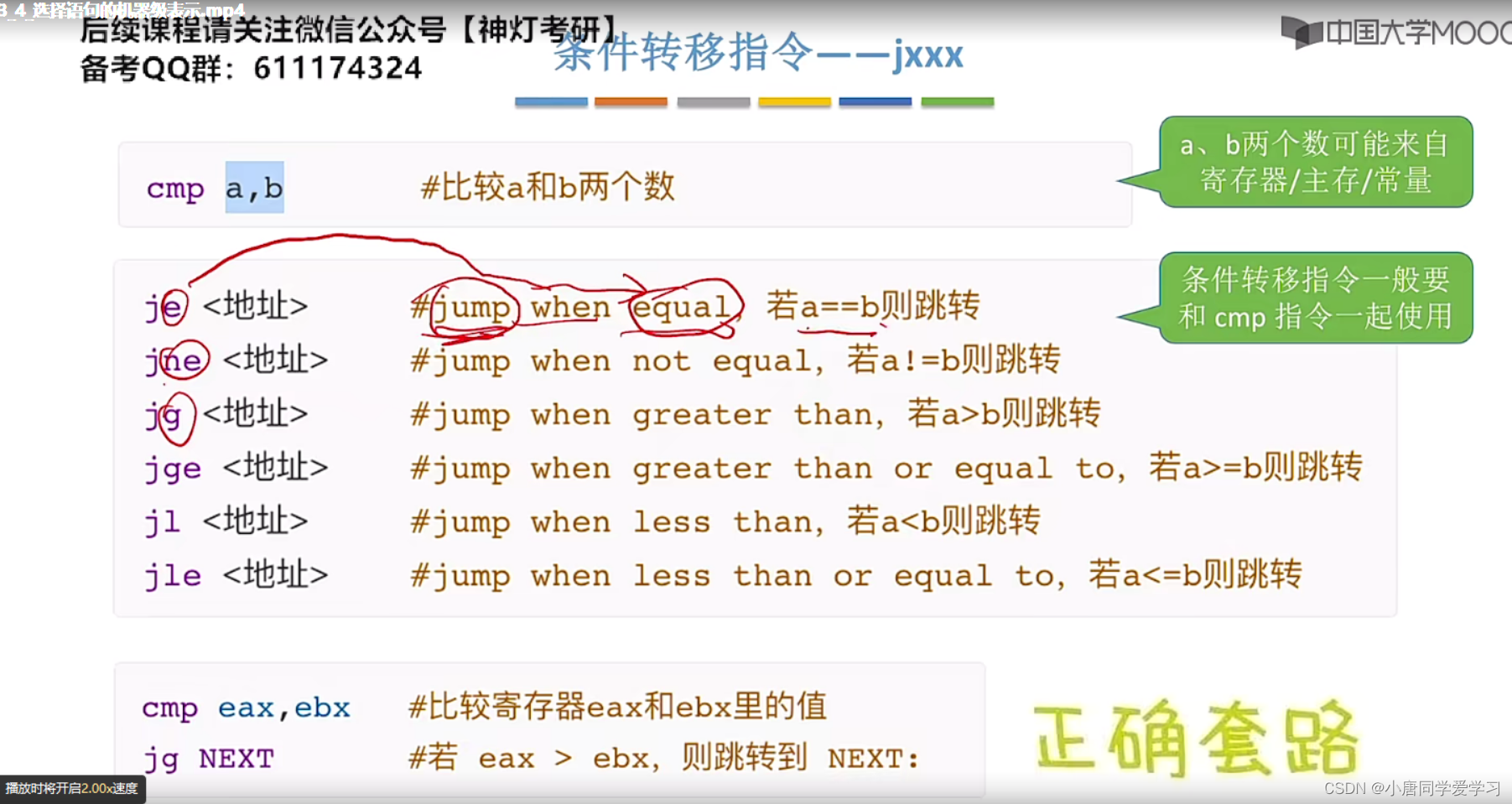

汇编条件转移:

存放在暂存寄存器中的数据为什么存放在通用寄存器中数据会被破坏?

存放在暂存寄存器中的数据是为了临时保存,以便进行后续的操作。通用寄存器是CPU中的一种存储设备,用于存储指令执行过程中需要使用或修改的数据。由于通用寄存器的空间有限,不能同时存放多个数据,因此在不同操作之间必须清空寄存器中的数据。如果在存放在通用寄存器中的数据上直接进行修改而没有保存原始数据,则原始数据会被破坏。

另外,暂存寄存器和通用寄存器的设计目的也不同。暂存寄存器通常用于缓冲输入/输出数据、辅助CPU处理数据等,它们的容量比通用寄存器大,但速度较慢。通用寄存器则专门用于CPU执行指令时的数据存储,容量一般比暂存寄存器小,但速度更快。因此,为了保证CPU指令的正确性和高效性,暂存寄存器和通用寄存器各自扮演不同的角色,在不同的场景下发挥作用。

机器周期通常由存取周期来决定

指令字长一般都取存储字长的整数倍

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?