ARM

首先先介绍一下ARM公司。

ARM成立于1990年11月,前身为Acorn计算机公司

主要设计ARM系列RISC处理器内核

授权ARM内核给生产和销售半导体的合作伙伴

ARM公司不生产芯片

提供基于ARM架构的开发设计技术

软件工具

评估版

调试工具

应用软件

总线架构

外围设备单元等等

CPU中央处理器

首先在芯片中,中央处理器(CPU) 是一台计算机的运算核心和控制核心。

CPU、内部存储器和输入/输出设备是电子计算机三大核心部件。其功能主要是解释计算机指令以及处理计算机软件中的数据。

CPU细分的话可以分为:Kernel(也称为ARM内核) 和外设。

ARM内核

在ARM内核中,主要包括:

ALU:算数逻辑单元

RO~R12:通用寄存器(不可被寻址)

PC:程序寄存器

LR:连接寄存器

SP:栈指针寄存器

Cache:高速缓存

MMU:内存管理单元

因为处理器的编码是一串数字,比较难记,因此开发出了助记符号来降低开发难度提高效率,所以产生了汇编语言,由于汇编语言的结构不是很清晰,因此人们采用了汇编语言来产生较高层次的语言(如C语言)。

编译是从源代码(通常为高级语言)到能直接被计算机或虚拟机执行的目标代码(通常为低级语言或机器语言)的翻译过程。

所以编译流程分为四个步骤:

编译流程分为四个步骤:

预处理(Pre-Processing)

编译(Compiling)

汇编(Assembling)

链接(Linking

ARM三级存储系统

三级存储系统 速度 容量 价格

Cache 快 小 贵

主存储器(RAM) 中 中 小贵

辅助存储器(ROM) 慢 大 便宜

在高速缓冲存储器(Cache)中,CPU可以直接访问,用来存放当前正在执行的程序中的活跃部分,以便快速地向CPU提供指令和数据。

在主存储器中,可由CPU直接访问,用来存放当前正在执行的程序和数据。

在辅助存储器中,设置在主机外部,CPU不能直接访问,用来存放暂时不参与运行的程序和数据,需要时再传送到主存。

RAM分类

(1)sram(static ram) 用晶体管存储0、1。速度快,成本高,存储密度低。

(2)dram(dynamic ram) 动态存储,用电容充放电存储0,1。功耗大,需要外接刷新电路,读写速度低于sram。成本低,存储密度大。

(3)sdram(synchronous dram) 增加了同步电路,提高dram的数据读写速度。

(4)ddr ram (全称ddr sdram即double data rate sdram),为sdram的下一代。目前已发展到ddr5。

(5)iram (internal ram)注意iram并非是真正意义上的某种ram,通常iram就是sram,它通常存在于Soc内部,所以被称为iram。

ROM分类

(1)rom 非易失性存储器,最早的rom在出场时写入数据,之后无法更改。

(2)prom (programmable rom)可编程rom。出场后能够让用户写入一次数据,例如cdrom。

(3)eprom (erasable prom)可擦写prom,出场后可以擦除数据再次写入,但需要特殊的设备。如紫外光等。

(4)eeprom (electically eprom)电可擦写可编程rom,无需专用设备就可以擦写,编程。

(5)flash 闪存,新一代非易失性存储器。

flash存储器可以分为:

①nor(或非) flash :可以被寻址,但是价格贵

②nand(与非) flash

以上就是背景

ARM的工作模式

ARM有7个基本工作模式:

(1)User:非特权模式,大部分任务执行在这种模式

(2)FIQ:当一个高优先级(fast)中断产生时将会进入这种模式

(3)IRQ:当一个低优先级(normal)中断产生时将会进入这种模式

(4)Supervisor:当复位或软中断指令执行时将会进入这种模式

(5)Abort:当存取异常时将会进入这种模式

(6)Undef:当执行未定义指令时会进入这种模式

(7)System:使用和User模式相同寄存器集的特权模式

Cortex-A特有模式:

Monitor:是为了安全而扩展出的用于执行安全监控代码的模式;也是一种特权模式

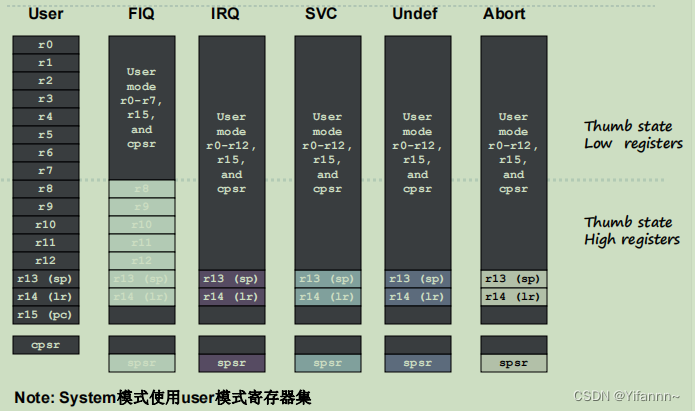

ARM9的通用寄存器

这个内容上面已经介绍过

ARM 寄存器

ARM 有37个32-Bits长的寄存器.

1个用作PC( program counter)

1个用作CPSR(current program status register)

5个用作SPSR(saved program status registers)

30 个通用寄存器

Cortex体系结构下有40个32-Bits长的寄存器

Cortex-A多出3个寄存器,Monitor 模式 r13_mon , r14_mon, spsr_mon

当前处理器的模式决定着哪组寄存器可操作. 任何模式都可以存取:

相应的r0-r12子集

相应的 r13 (the stack pointer, sp) and r14 (the link register, lr)

相应的 r15 ( the program counter, pc)

相应的CPSR(current program status register, cpsr)

特权模式 (除system模式) 还可以存取;

相应的 spsr (saved program status register)

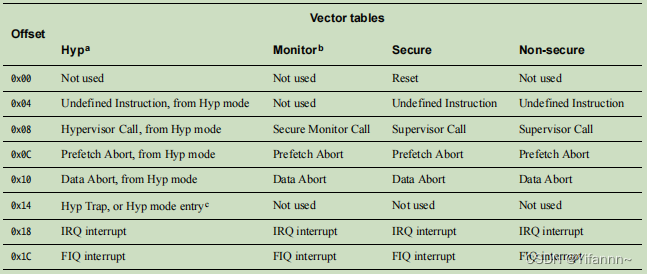

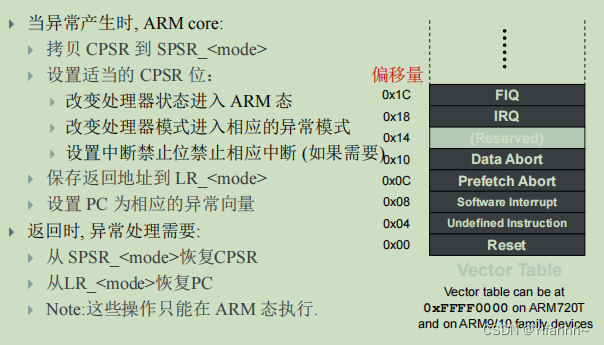

异常向量表中irq的异常向量是多少?

cpsr中的哪几位是用来设置工作模式的?

M[4:0]:用来设置工作模式

User 模式下,不能操作 bit[4:0],即不能切换处理器模式

更常见的情况是,处理器因异常事件而自动改变模式。

处理器模式:

ARM有9个基本工作模式:

(1)User(USR):10000

(2)FIQ:10001

(3)IRQ:10010

(4)Supervisor(SVC):10011

(5)Monitor(MON):10110

(6)Abort(ABT):10111

(7)Hyp(HYP):11010

(8)Undef(UND):11011

(9)System(SYS):11111

T Bit

T = 0;J=0; 处理器处于 ARM 状态

T = 1;J=0 处理器处于 Thumb 状态

T = 1;J=1 处理器处于 ThumbEE 状态

中断禁止位:

I = 1: 禁止 IRQ.

F = 1: 禁止 FIQ

A位:

A=1 禁止不精确的数据异常

E位:

大小端控制位

IT[7:2]:

IF….THEN….指令执行状态位

GE[3:0] :

大于或等于(当执行SIMD指令时有效)

DNM位:

Do Not Modify

J 位:

仅ARM v5TE-J架构支持

T=0;J = 1 处理器处于Jazelle状态

也可以和其他位组合

Q 位:

仅ARM v5TE-J架构支持

指示饱和状态

条件位:

N = Negative result from ALU

Z = Zero result from ALU

C = ALU operation Carried out or borrow

V = ALU operation oVerflowed

r13,r14,15别名是什么?有什么作用?

R13:SP(栈指针寄存器)

每一种异常模式都有其自己独立的R13,它通常指向异常模式所专用的堆栈,也就是说五种异常模式、非异常模式(用户模式和系统模式),都有各自独立的堆栈,用不同的堆栈指针来索引。这样当ARM进入异常模式的时候,程序就可以把一般通用寄存器压入堆栈,返回时再出栈,保证了各种模式下程序的状态的完整性。

R14:LR(连接寄存器)

它有两个特殊功能。

(1)保存子程序返回地址。使用BL或BLX时,跳转指令自动把返回地址放入r14中;子程序通过把r14复制到PC来实现返回。

(2)当异常发生时,异常模式的r14用来保存异常返回地址,将r14如栈可以处理嵌套中断。

R15:PC(程序寄存器)

PC是有读写限制的。当没有超过读取限制的时候,读取的值是指令的地址加上8个字节,由于ARM指令总是以字对齐的,故bit[1:0]总是00。当用str或stm存储PC的时候,偏移量有可能是8或12等其它值。在V3及以下版本中,写入bit[1:0]的值将被忽略,而在V4及以上版本写入r15的bit[1:0]必须为00,否则后果不可预测。

1875

1875

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?