前言

第一次玩手机充电芯片,个人水平有限,如有不对的地方欢迎指出,也欢迎大家在评论区交流!

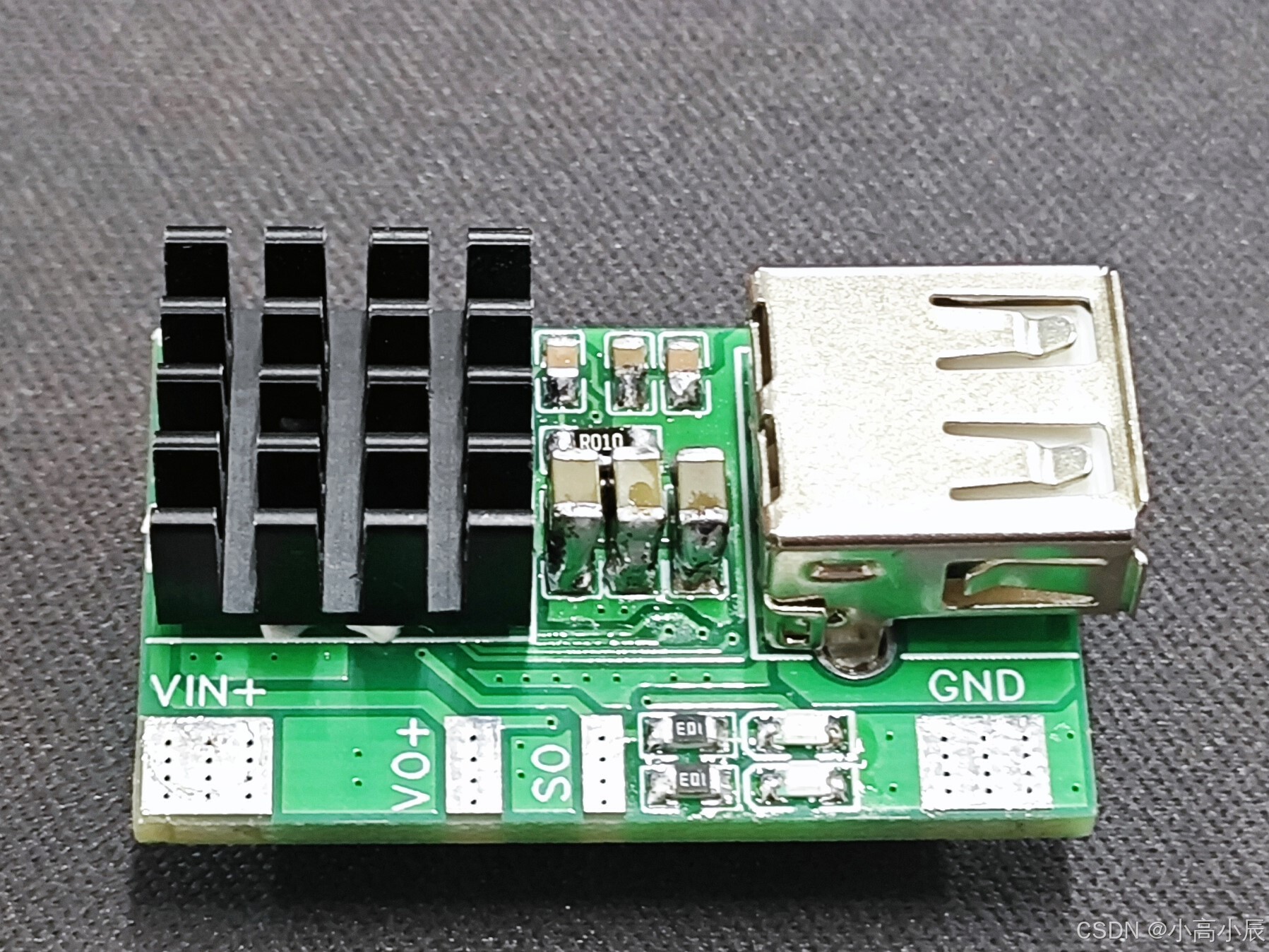

先上外观图,为了兼顾散热片所以把电感放在背面了,为减小体积,用的都是mlcc电容。

本文简单介绍该芯片原理,更多的是探讨其出现的问题!!!输出纹波1.554V!!!

1. SW3526简介

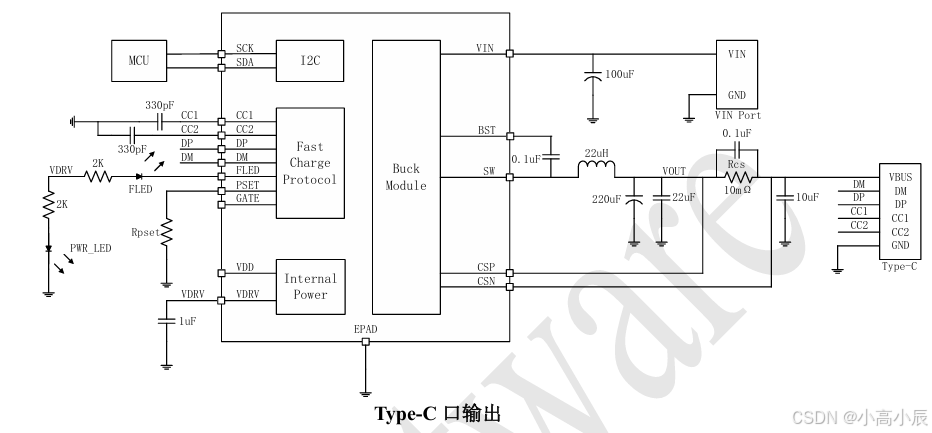

个人认为手机充电芯片大部分都是DC-DC变换器+协议管理,所以阅读手册后发现其内部结构应该是同步buck整流,原理就不多说,有趣的地方是其没有单独的电压反馈线,猜测其可能是用了电流检测的其中一根线检测输出电压,具体不得而知,其手册中未画出buck Module的内部框图。

其中IIC通讯未用到,官方手册也没有描述其通信寄存器。CC1\CC2\DM\DP为充电协议通讯引脚,FLED是快充指示灯,VDRV是内部工作电压,外接PWR_LED可监测芯片上电状态,实测为5V左右,PSET是输出(充电)功率编程引脚,详见手册,BST为上N管的Bootstrap引脚,其实就是自举升压到VOUT+NMOS驱动电压以驱动上管,而其没有续流二极管,则可见其是同步整流,续流二极管使用一个MOS管代替,其工作频率为125kHz,经过计算,在输入24V输出20V3A时,输出电感值选择22uH是合适的,当输入24V输出5V3A时,选择33uH较为合适,最终测试使用22uH电感,RCS是电流采样电阻,将电流信号转换为电压信号,经芯片内部的放大等处理后得到输出电流值,原理大概就这样,更多更细的部分可以自己探索。

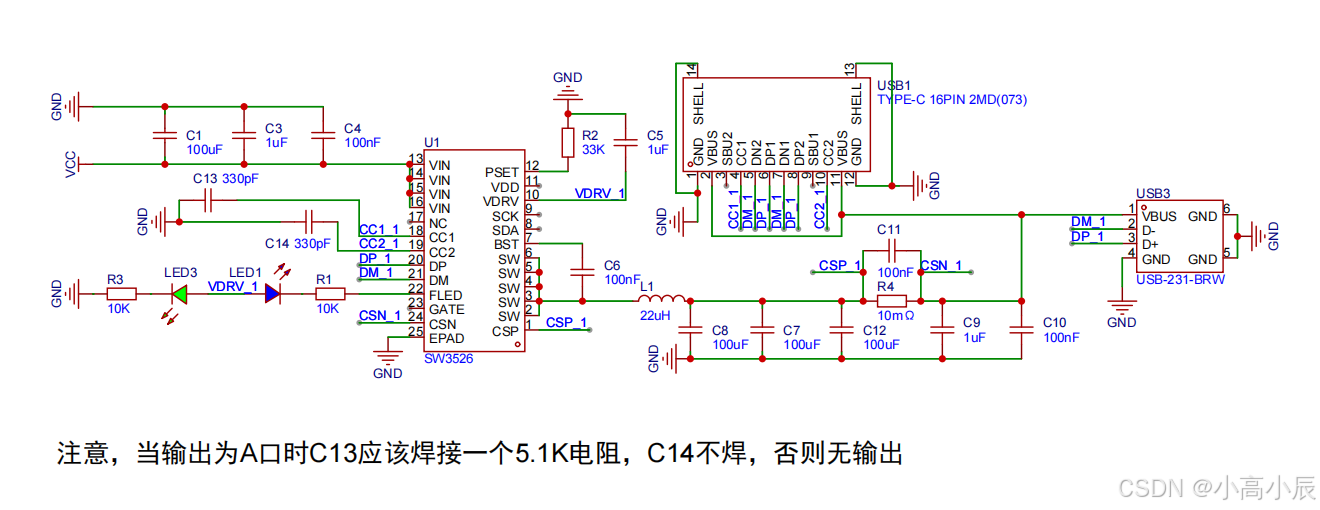

值得注意的是在输出口为A口时CC1应该连接一个5.1k的下拉电阻,否则无输出。

2. 手机充电器对纹波的要求

国际电工委员会(IEC)和欧盟(CE)分别制定了IEC 60320和EN 60320两项标准,规定了纹波的最大值。 IEC标准要求输出电压和电流纹波最大值为输出值的2%,而EN标准则更为严格,要求纹波最大值为输出值的1%。 测试充电器纹波的方法包括准备测试设备如数字万用表、电子负载仪和示波器,进行空载测试和带载测试。

依据我国的先行规范GB/T 35590-2017中要求纹波不大于200mv。

3. 纹波

3.1 测试条件

3.1.1 说明

- 示波器探头去掉地夹头,使用专用的纹波测试探针测试。

- 使用取电器获取不同的电压输出。

- 使用电子负载为测试负载,恒流模式。

- 测试点为A口的输出引脚,非电子负载仪接口处。

- 输入电压统一为24V输入。

- 为最大程度保持结果的准确,所有条件的改变都在同一块PCB上进行。

声明:非专业测试!!!设备也不专业,更没有校准!!!

由于PCB布局,电感材质、电容材质及质量等也会影响纹波,所以结果不具任何参考价值!!!

3.1.2 原理图

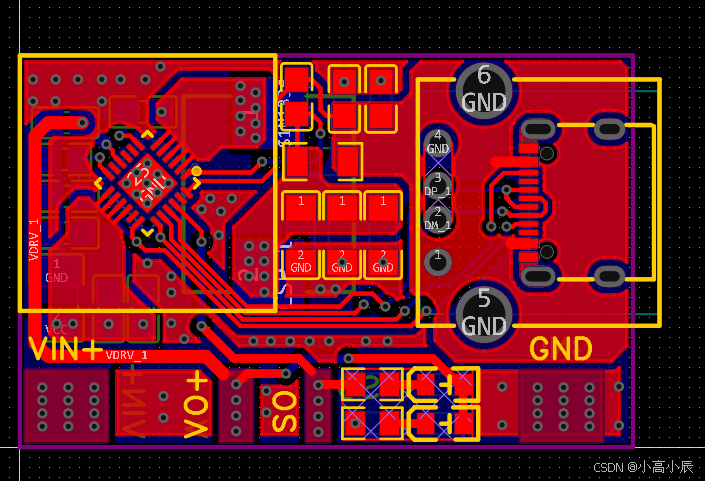

为了控制PCB大小,全用的MLCC电容。

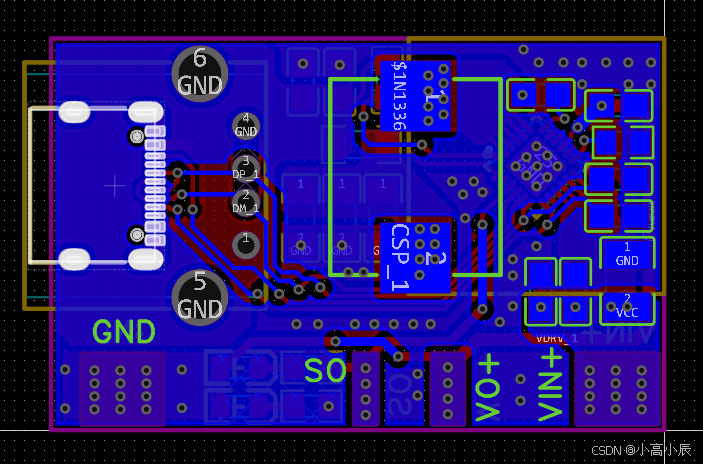

3.1.3 PCB

3.2 测试结果

3.2.1 效率

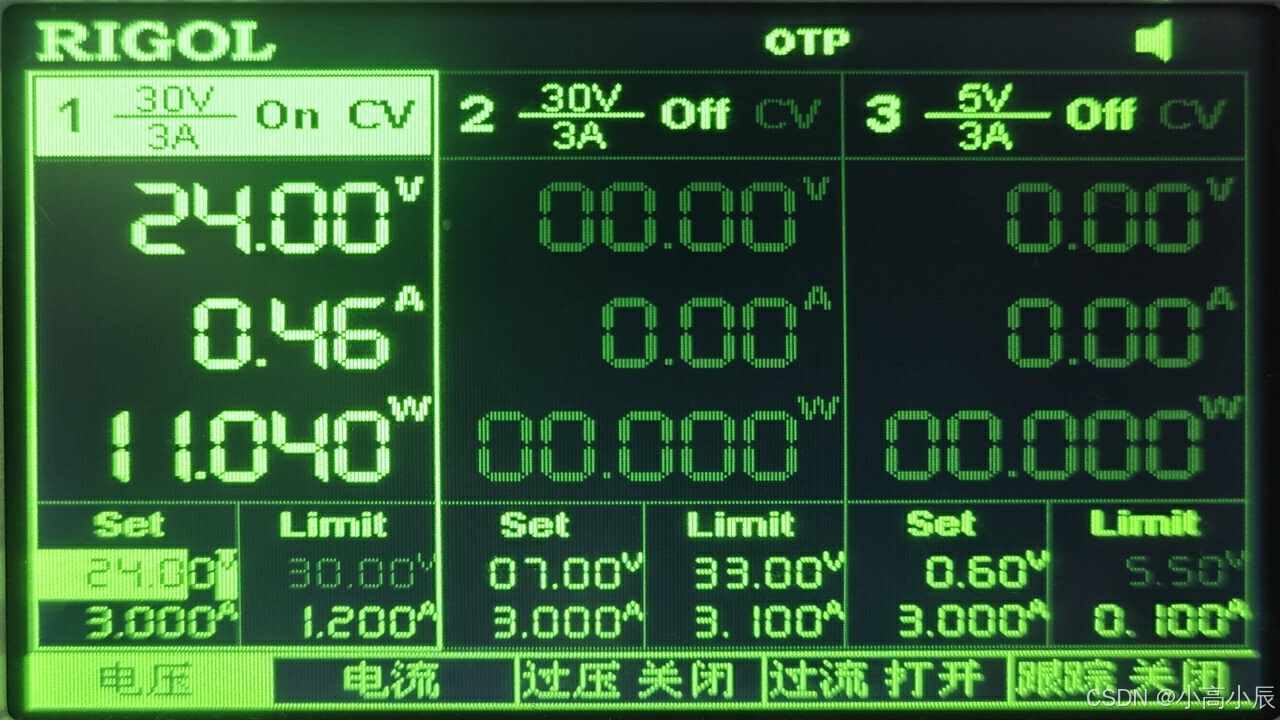

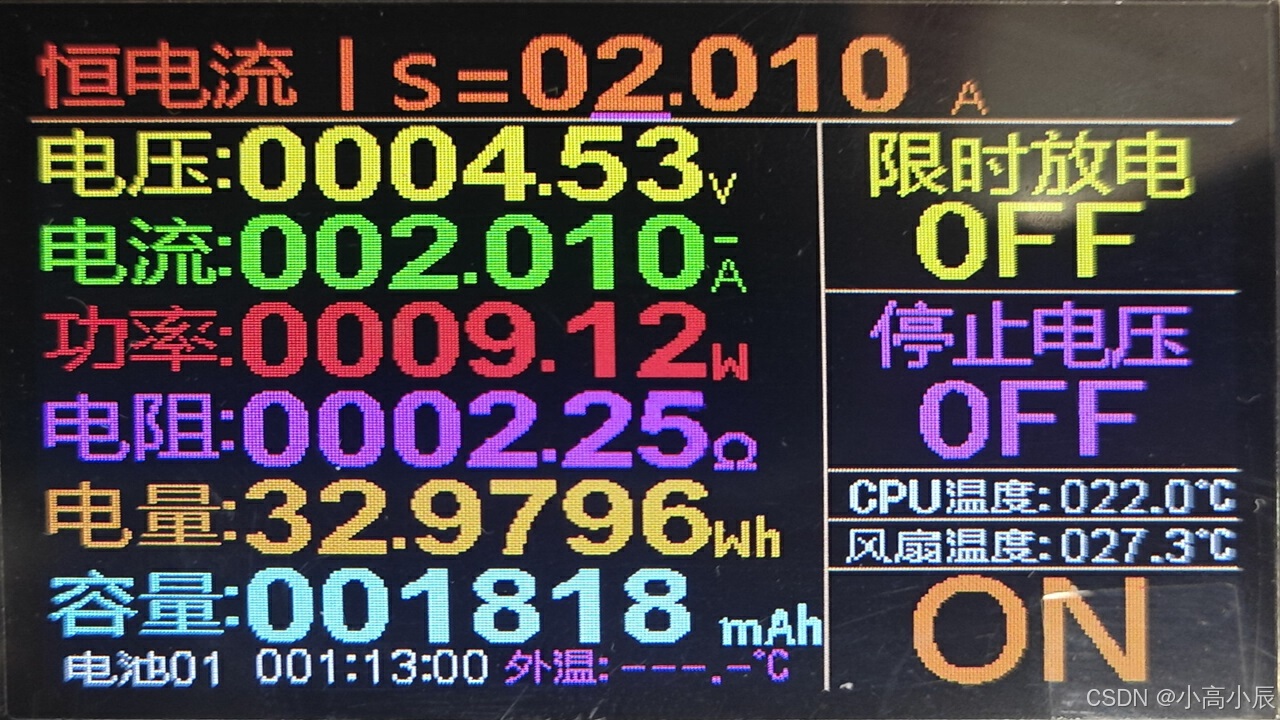

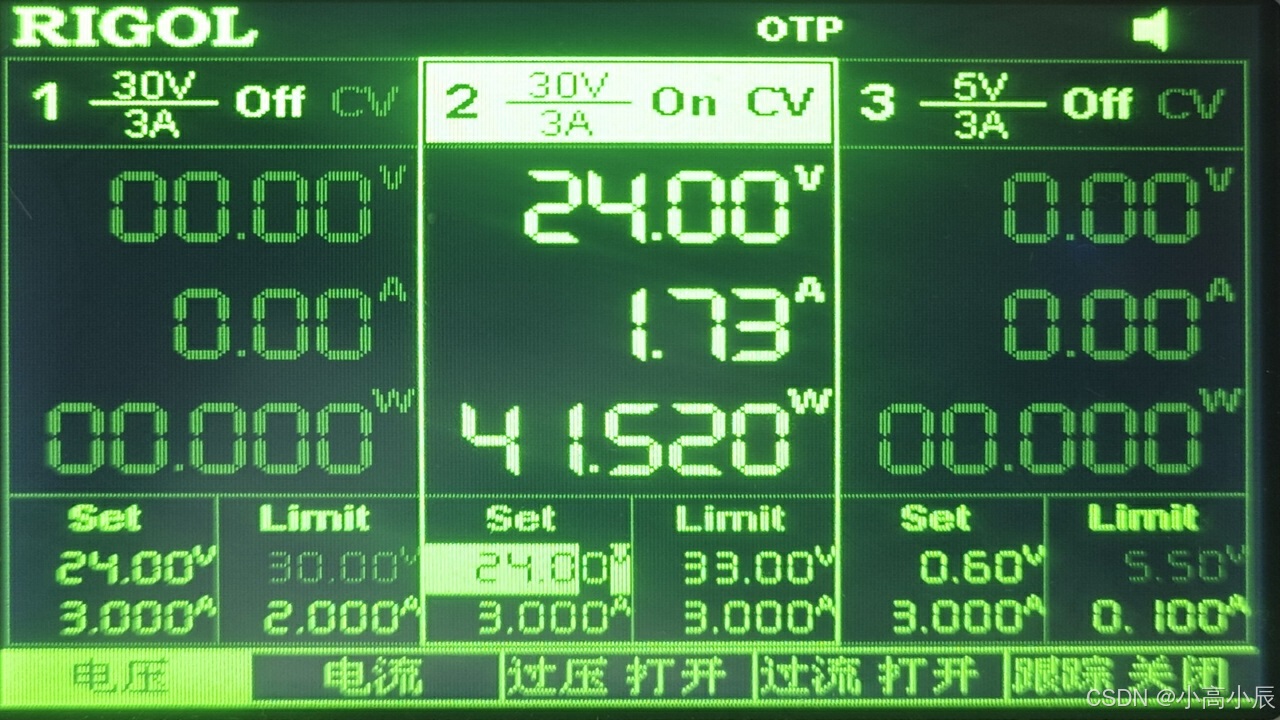

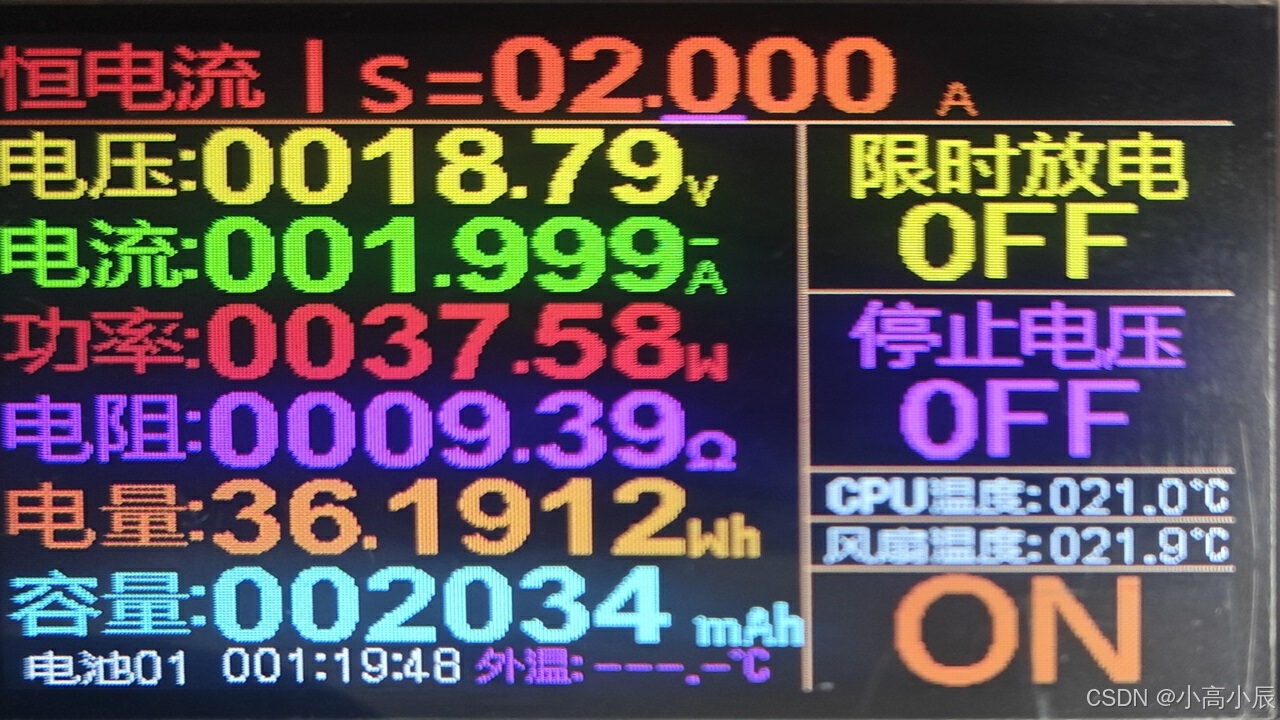

输出5V2A(左图为电源箱输出功率即SW3526输入功率,右图为电子负载功率,下同)

但是!!!由于线损的存在,实际效率应该还要高一些,下面的也一样!!!

输出5V3A

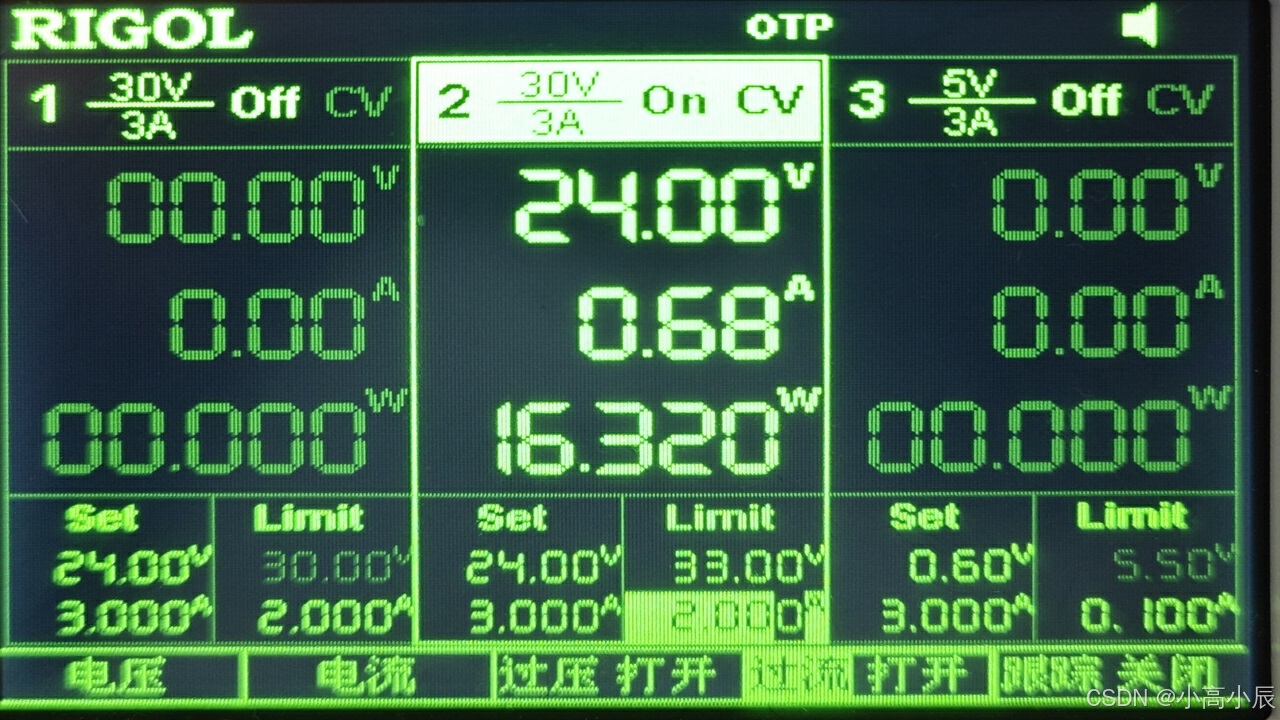

输出20V2A

总结:效率还是不错的,由于我装了散热片,发热也还好,虽然没有测手册中描述的最大效率点VIN=12V,VOUT=5V,IOUT=3A(效率>94%),但是总体来看,个人认为效率表现还是不错的。

3.2.2 纹波表现

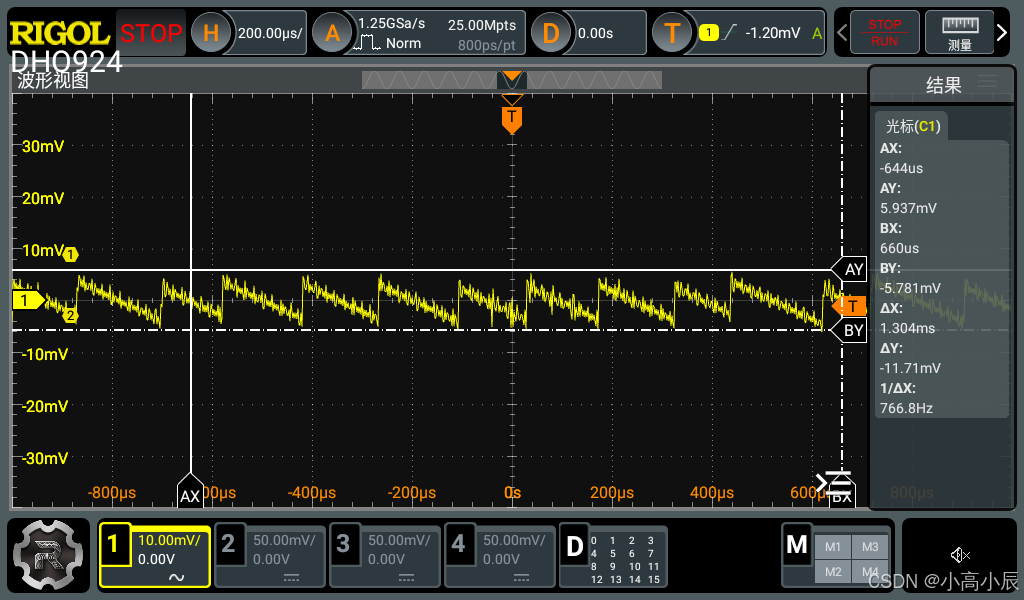

左图5V空载 11.71mV,右图5V3A 37.18mV

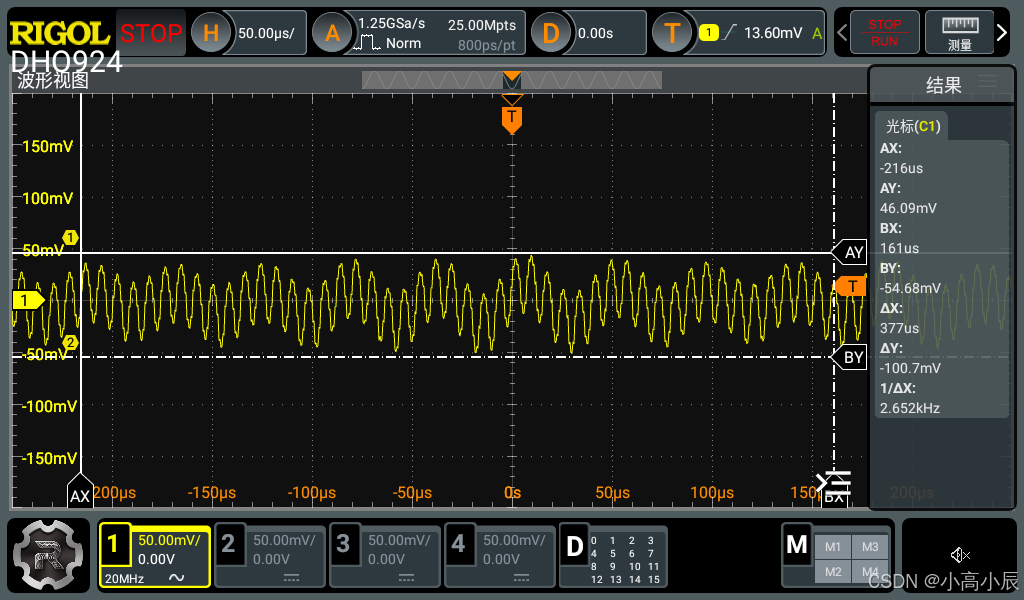

左图9V空载 11.09mV,右图9V3A 100.7mV

此时的纹波表现已经不满足EN标准了,但是还在IEC标准和国标要求范围内。

3.2.3 纹波超限

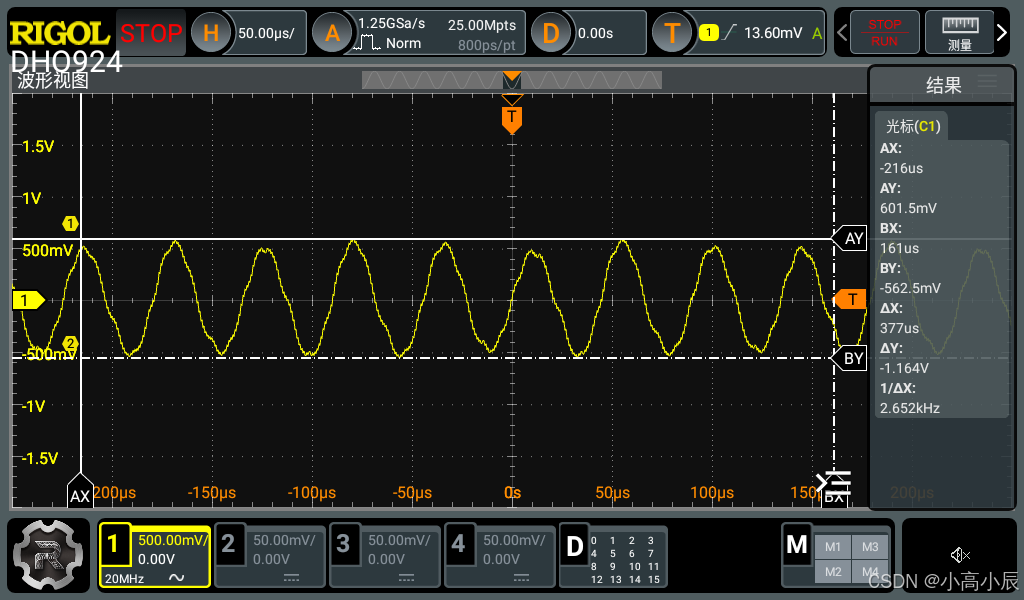

输出为12V3A时,输出纹波来到了 1.164V,非常严重!!!

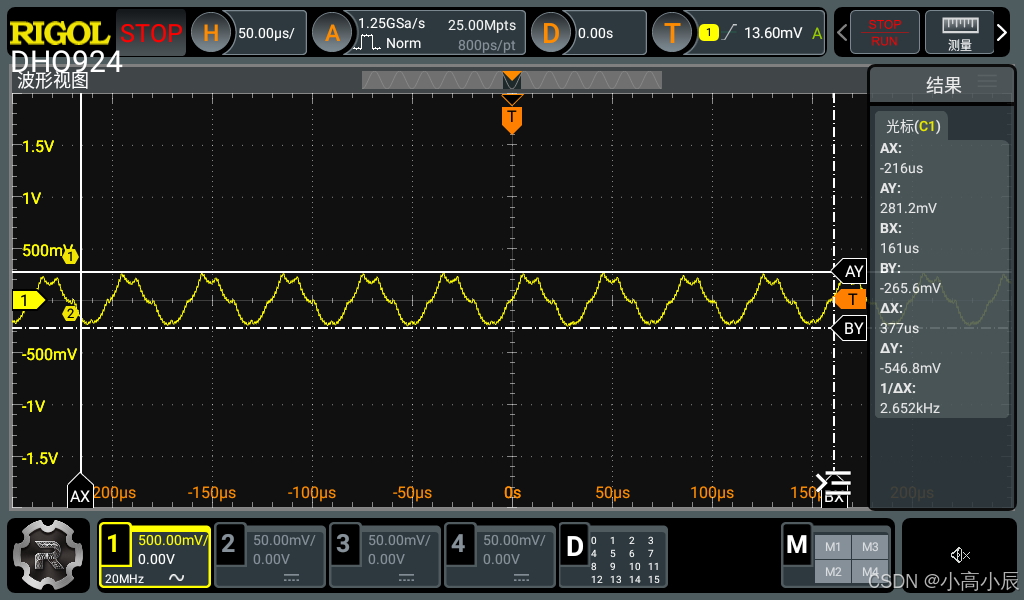

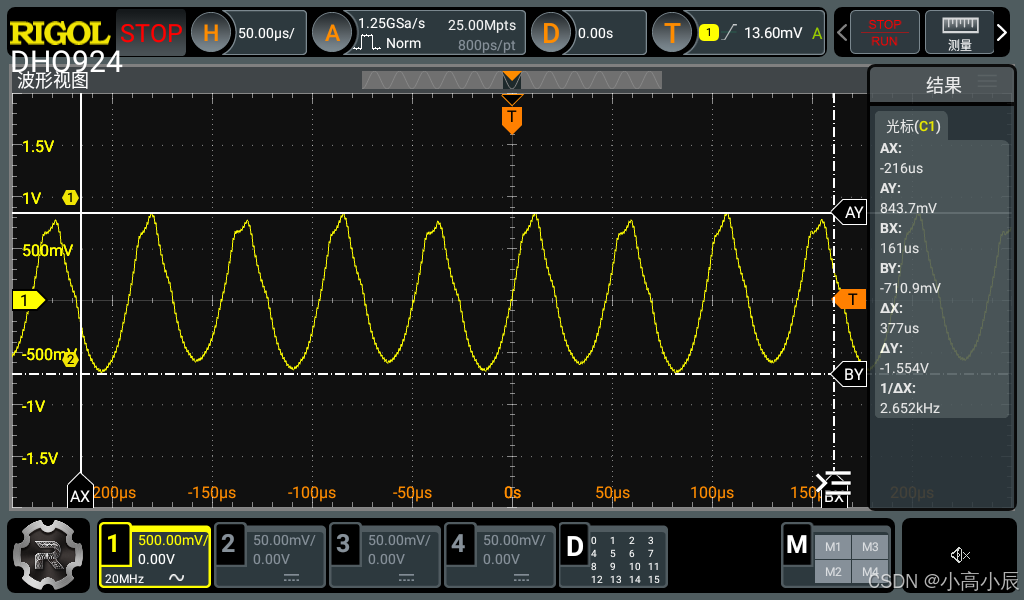

左图20V1A 546.8mV,右图20V2A 1.554V

我不禁怀疑自己,是不是自己的技术太差,这玩意能给设备充电吗?

3.3 改善纹波

首先排除负载影响,因为纹波也会受负载影响,所以我找来了几个水泥电阻

测试后发现纹波几乎没什么变化,所以排除掉!

3.3.1 对于DC-DC变换器的纹波,主要影响有以下两大因数

- 电感峰值电流。

- 输出阻抗。

另外的原因就是反馈回路的不稳定,也可能造成较大的输出“纹波”。

3.3.2 电感峰值电流

对于Buck电路的电感峰值电流,其简要公式为

其中D为占空比,Ts为周期,定性分析:如果要降低纹波,就必须要减小电感峰值电流,观察公式可以发现可以减小纹波的情况如下

- 当周期减小时

- 当L增大时

- D值减小

来讨论这三种情况

- 此时会发现SW3526的工作频率为固定的125kHz,无法减小Ts,除非换工作频率更高的芯片。

- 而22uH保证在大功率输出时电感不会饱和,若要增大L值,则必须使用更大饱和电流的电感,而在同体积下,饱和电流与电感量成反比,而饱和电流、电感量与体积成正比,若想从电感下手,则必然要更大体积的电感、更大的PCB空间、更大的成本,则此路不好走。

- 而D值则是由实际工作情况而定,从能量传输的角度来说,若要输出更大的功率,则占空比这个“门”必须开的更大,这样才能让更多的能量从变换器的输入传递到输出,则D值更是不好调整。因为我就是要大功率!

发现开关频率、电感量、D值无法调整。

3.3.3 输出阻抗

这里必须提到电容的ESR参数,不同类型的输出电容,寄生参数的大小不同,使用不同类型的输出电容会得到不同波形的电压纹波。

电容非理想电容,如下电容等效图,其由一个等效串联电阻ESR、等效串联电感ESL和一个等效并联电阻Rleak组成的电路。

而ESR是影响纹波的重要条件,当电流流经电容时,势必会“流过”ESR,则此时由基本的欧姆定律可知,其定会产生电压,而这个电压会叠加在输出电压波形中,就变成了我们看到的纹波。

常见电容的ESR

- 钽电容的ESR通常都在100毫欧以下,在低频段,其ESR比陶瓷电容高,但在中频段,其ESR相对较低,且较为稳定。

- 陶瓷电容包括多层陶瓷电容(MLCC)等,在标准规格频率100kHz下,由于其多层结构,ESR值最低。不过在低频段,二类MLCC电容器的ESR比其他类型的电容要高。

- 薄膜电容的ESR较低,其优势在于高压、高频高温性能好、寿命长、可靠性好、ESR和ESL较低等,但尺寸相对较大、单体电容的容量较小且成本高昂。

- 铝电解电容的ESR相对较大,并且受频率和温度的影响较明显。低频低温下,氧化铝对整体ESR的贡献最大;高频高温下,电解质对ESR的贡献最大。不过市面上的聚合物和混合电极的电解电容,ESR更低、更稳定。

而我使用的是MLCC电容,理应ESR不高,使用镊子电桥实际测量的结果如下图

左图是普通电解电容50V100uF的测量结果:96.82uF 601.3mΩ

左图是正在使用的MLCC电容50V100uF的测量结果:60.93uF 49.5mΩ

不难看出其ESR都不是一个量级的,但是标的100uF的MLCC电容值明显太低,那么到现在,似乎都没问题,难道就束手无策了吗?

对于MLCC电容值的问题,购买时商品标题如下图

商家标明了是107K,而尾缀K是误差范围,如下图

K代表±10%的误差,则理应其容值不会低于90uF,询问商家后,商家是这样回的

这我就纳闷了,第一次听所要上机测,不过我确实上机测量了,结果还真和商家说的一样,我就没有深究,有知道原因的朋友欢迎在评论区发表。

4. 电容的容值及不同电容在不同频段的ESR 精华

4.1 容值

观察下面两张图!

左图是20V2A的输出纹波1.554V

右图是20V3A的输出纹波约800mV(忘记在示波器上测量了)

纹波下来了!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

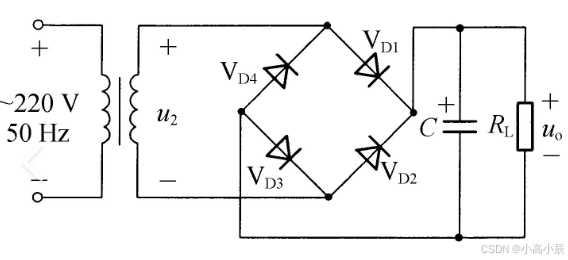

原因是我由原理图的3个100uF增加到了6个100uF,容量的加大,其容值的增加,必然会减小纹波,原因我认为可以从能量传递的角度理解,如下图对220V交流电进行整流滤波

整流滤波后的RL两端波形如下

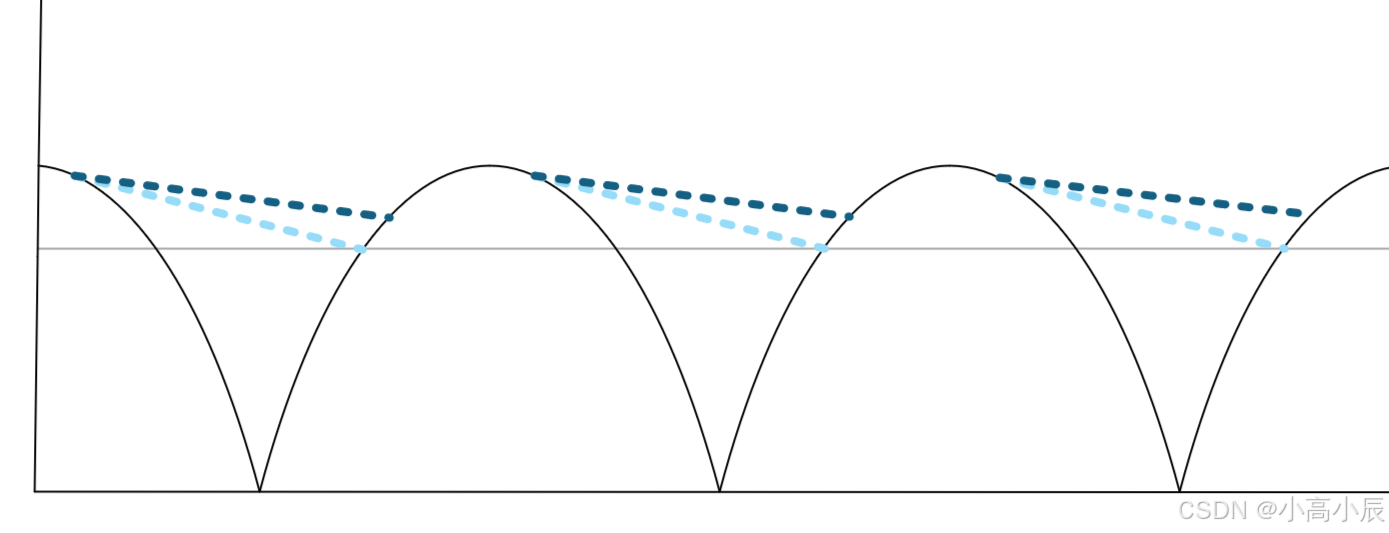

图中的黑色线是经过整流但不滤波(不接电容C)的波形曲线,浅色线是接入电容C(容值xxxuF Cx)的波形,较深色线是接入电容C(容值yyyuF Cy)的波形,其关系是xxx > yyy,也就是Cx > Cy,即深色线的滤波电容比浅色线的大。

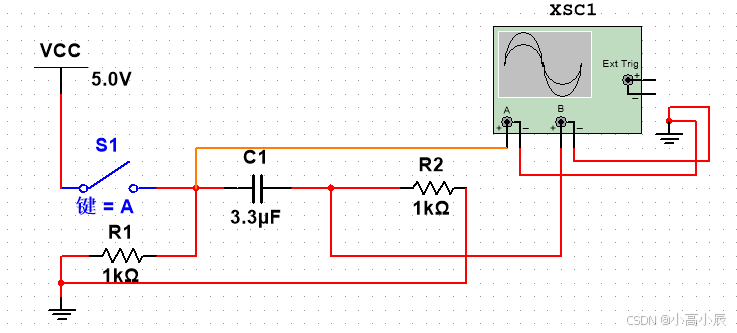

开始分析前,我们要知道电容的特性是阻止其两端电压的突变,看仿真图

在开关S1断开时,C1两端通过电阻接地,此时C1两端的压差为0,在开关S1闭合时,C1左端被上拉到5V、右端被下拉到地,此时R2变成负载。

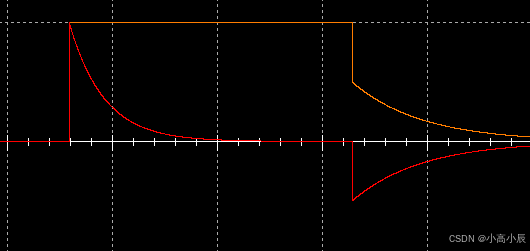

仿真得到的波形图

其中,橙色线是C1的左端波形曲线,红色线是C1的右端波形曲线

- 开始时,开关S1断开,C1左右两端被下拉到地,两端压差为0。

- 开关S1闭合瞬间,橙色线瞬间被拉到5V,而红色线也瞬间抬升到5V,原因就是保持两端压差为0。此时电流为正向,也就是从5V流过C1、R2后到地。

- 开关S1闭合后,C1左端电压不再变化,由于电容的通高频阻低频特性,再加上C1右端的下拉电阻(负载),其电压开始下降,直到地,压差变为5V。此时的电流,依旧从5V流过C1、R2后到地缓慢减小,C1右端下降到0V后,电流截止。(这一状态我的解释也不一定对,尽力了!)

- 开关S1断开后,橙色波形瞬间下降到2.5V左右,红色波形瞬间下降到-2.5V左右,可以认为压差依旧是5V,由于电容存储的能量有限,能量开始减少,压差也减小,直到0V。为什么不是瞬间下降到0V呢?我也不清楚,可能是R1的缘故,也可能是电容的其它特性,不深究,结果也依然是维持了其两端压差。

回到前面的整流滤波后的波形,可见

- 当整流后的电压低于电容电压时,为维持电容两端的电压差,电容开始放电,此时能量从电容中传递到负载。而由于电容容量有限,其能释放的能量有限,维持两端的压差效果微乎其微,压差开始反向增大。

- 当整流后的电压高于电容电压时,为维持电容两端的电压差,电容开始充电,此时能量从电源传递到电容和负载,而由于电容容量有限,其能吸收的能量有限,维持两端的压差效果微乎其微,压差开始正向增大。

然后来比较不同电容值的效果

Cy > Cx ,显然易见使用Cy电容的滤波效果比Cx电容的滤波效果更加平缓,更趋向于理想的DC电压波形,究其原因就是可以存储的能量更多,当需要电容充电时,可吸收更多的能量,进一步减小电压增大的幅度,当电容需要放电时,可以释放更多的能量,进一步减小电压下降的幅度。

所以当我将3个100uF并联增加到6个100uF时,输出的纹波出现了较为明显的下降。

但是这纹波表现依旧不符合要求!!!

最后终于还是发现了问题所在,电容在不同频段的ESR!

4.2电容在不同频段的ESR

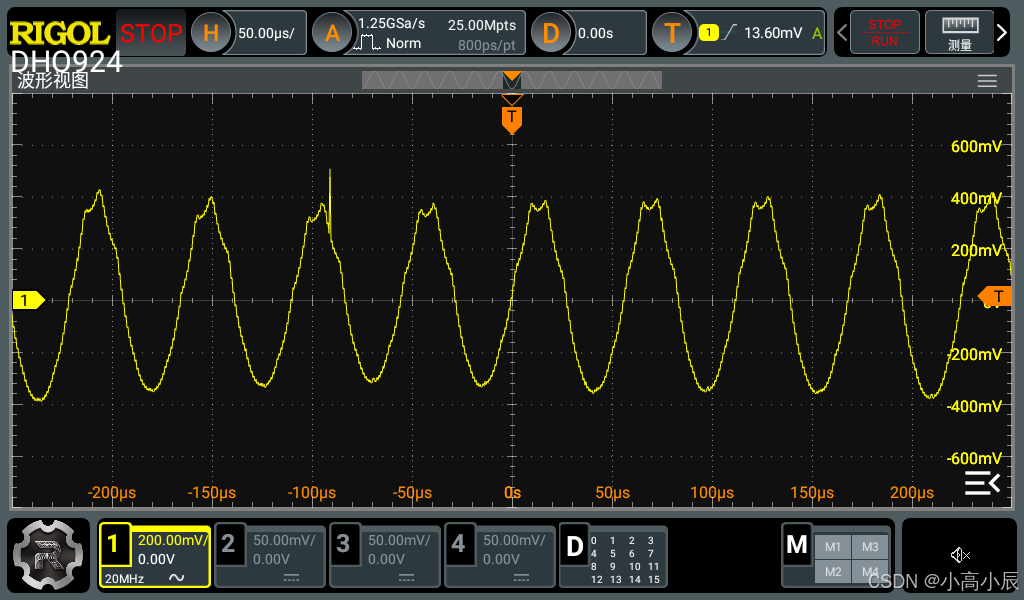

先看图

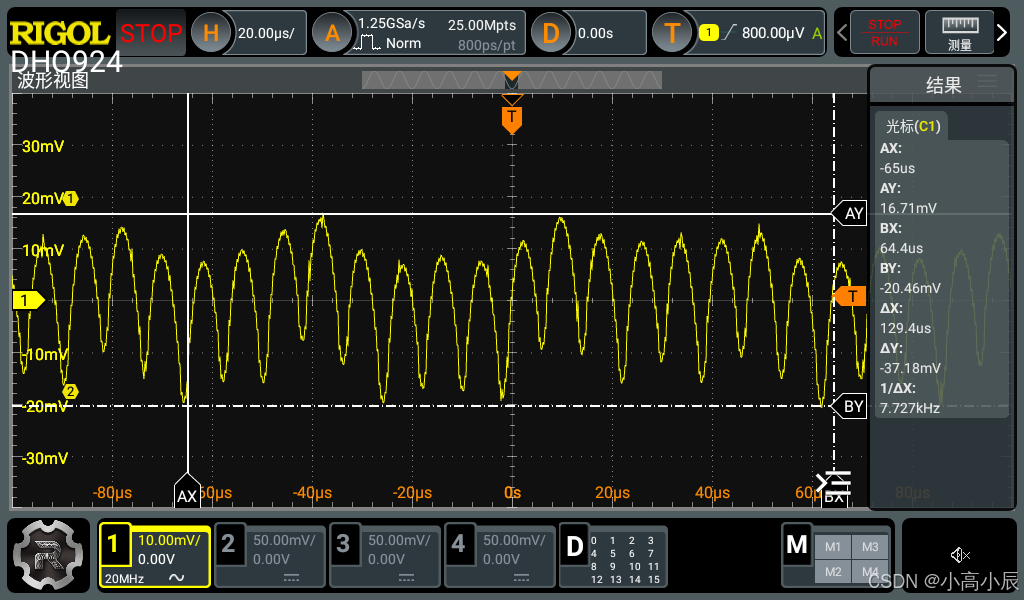

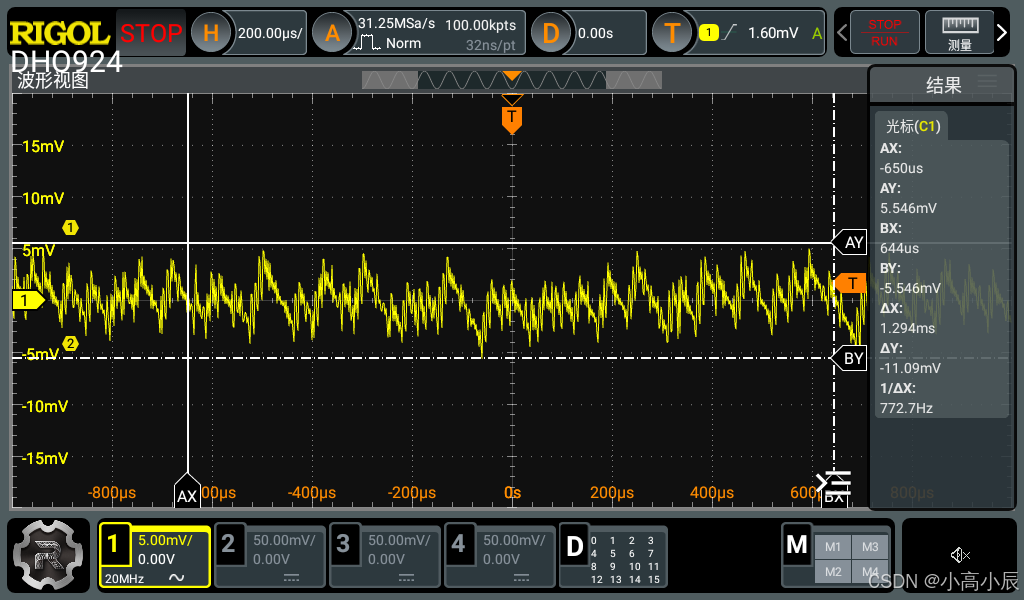

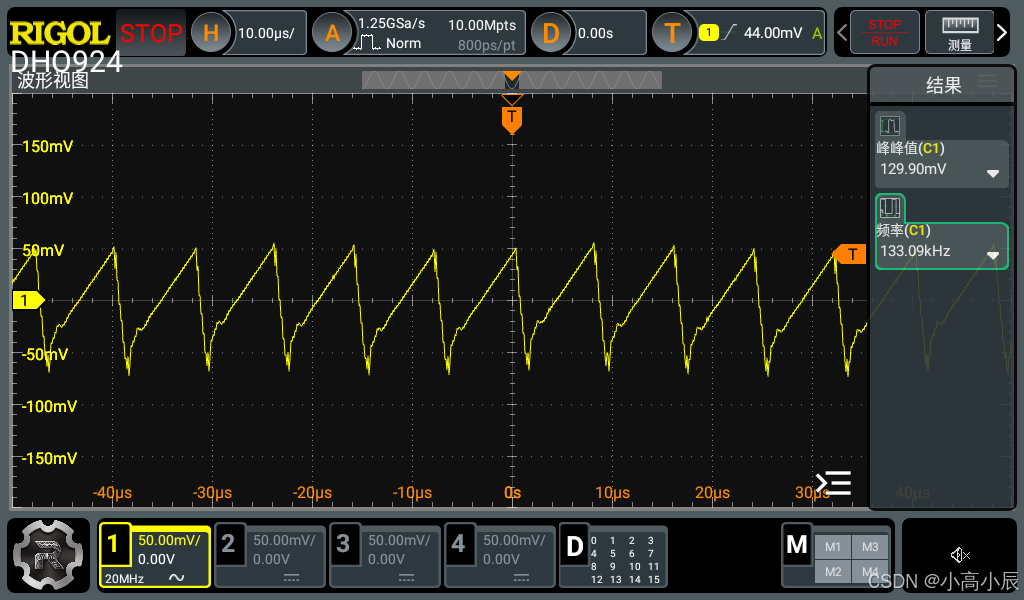

左图是20V3A时的纹波 129.9mV 133.09kHz

左图是20V3A时的纹波 129.9mV 133.09kHz

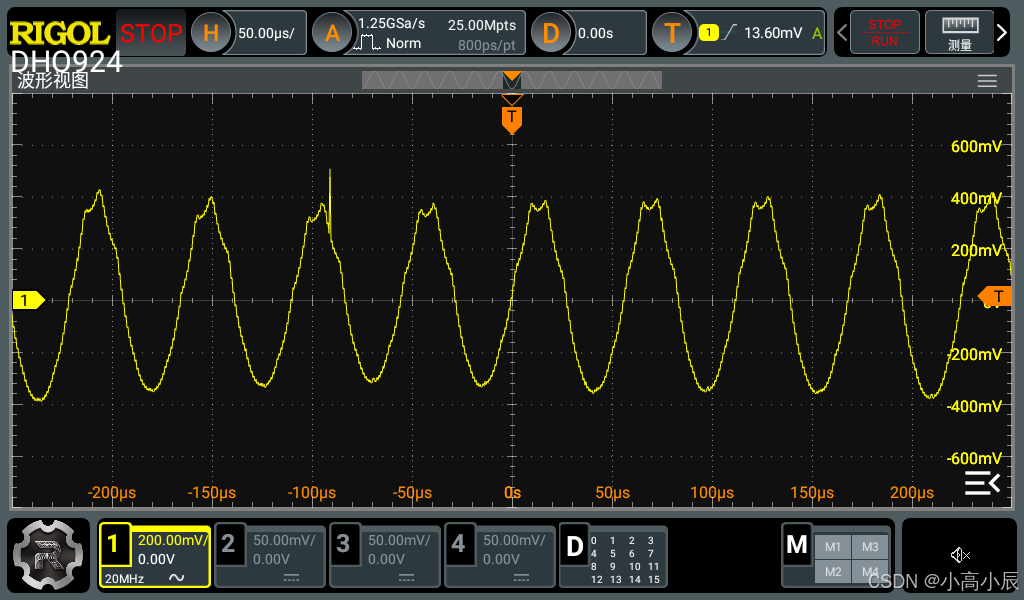

右图是20V3A时的纹波 约800mV 约20kHz

纹波完全符合国标要求,符合IEC标准要求,符合CE标准要求,呜呜呜呜!!!

原因是经过我的仔细观察,发现了这纹波的频率相较于开关频率太低,然后就想到了这个问题。

左图是去掉6个100uF(MLCC)电容,使用470uF电解电容代替而得到得结果,右图是6个100uF(MLCC)电容。可见纹波得频率在工作频率125kHz附近,频率较高,这就正常了。

我们常用得MLCC有X7R、X5R等材质的,这些都是二类电容,在低频段,二类MLCC电容器的ESR比电解电容等的电容要高,输出阻抗高,所以对低频的纹波滤除效果不尽人意。

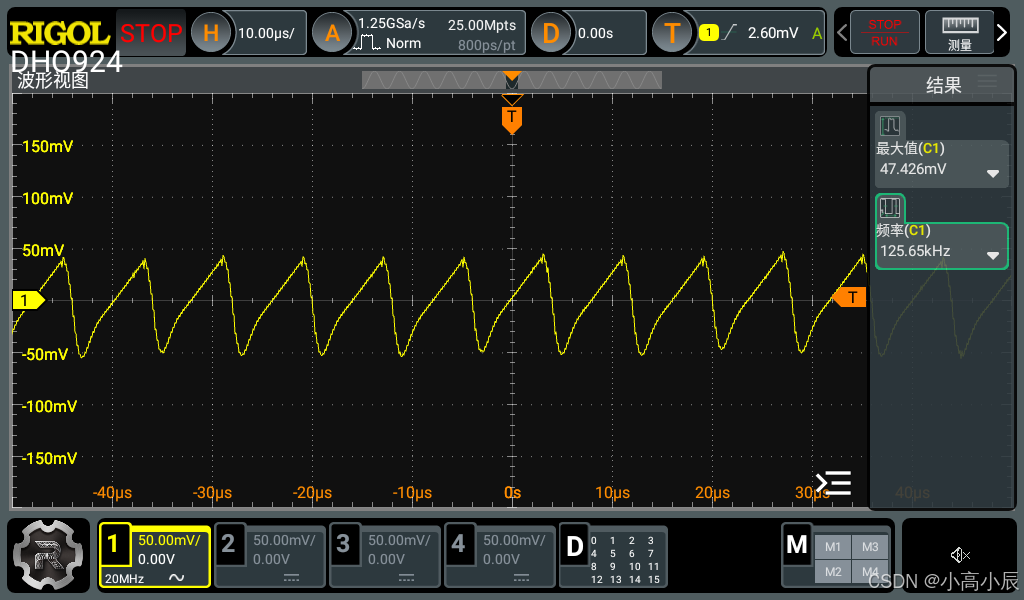

现在的输出电容是470uF(电解电容)+1uF(MLCC)+100nF(MLCC),如果我再加一个100uF(MLCC)呢? 干!

结果如下

同是20V3A输出,其纹波来到了47.426mV,可喜可贺啊!!!

如下图,某音博主阿甘体验在21年测量的品牌手机充电器纹波表现

现在SW3526纹波表现也是相当不错了,不过碍于自己DIY的产品,没有成本控制等等限制,自然不能与品牌手机充电器相提并论!

5. 文章到这里就结束了

简单总结一下:输出纹波主要由电感峰值电流、输出阻抗、输出电容容值大小影响,当无法改变电感电流时,更改输出电阻,是更为直接高效的措施,应该注意,当纹波频率明显低于工作(开关)频率时,应该增加低频特性更好的电容,如电解电容,当纹波频率与工作(开关)频率相近时,应该增加高频特性更好的电容,如MLCC电容。

又要重新画一版PCB了,难受!

6. 声明

- 由于本人水平实在有限(DXS),希望各位朋友自己注意辨别文章中的内容。

- 由于测试的不专业性,文中的任何测量结果均不具参考意义。

- 本设计已经在嘉立创开源平台开源,链接http:// https://oshwhub.com/gaochen1/zhuo-mian-chong-dian-zhan

568

568

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?