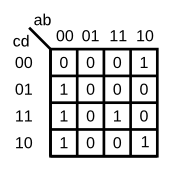

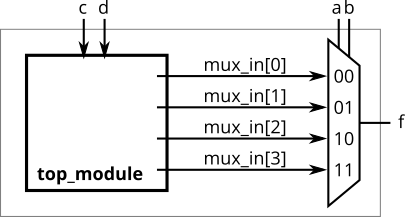

For the following Karnaugh map, give the circuit implementation using one 4-to-1 multiplexer and as many 2-to-1 multiplexers as required, but using as few as possible. You are not allowed to use any other logic gate and you must use a and b as the multiplexer selector inputs, as shown on the 4-to-1 multiplexer below.

You are implementing just the portion labelled top_module, such that the entire circuit (including the 4-to-1 mux) implements the K-map.

module top_module (//我的answer横着拆

input c,

input d,

output reg [3:0] mux_in

);

wire [1:0] cd;//注意这里一定不要忘记声明长度!

assign cd={c,d};

always@(*) begin

case(cd)

2'b00:mux_in=4'b0100;

2'b01:mux_in=4'b0001;

2'b10:mux_in=4'b0101;

2'b11:mux_in=4'b1001;

endcase

end

endmodule

module top_module (//refer answer竖着拆

input c,

input d,

output [3:0] mux_in

);

// After splitting the truth table into four columns,

// the rest of this question involves implementing logic functions

// using only multiplexers (no other gates).

// I will use the conditional operator for each 2-to-1 mux: (s ? a : b)

assign mux_in[0] = c ? 1 : d; // 1 mux: c|d

assign mux_in[1] = 0; // No muxes: 0

assign mux_in[2] = d ? 0 : 1; // 1 mux: ~d

assign mux_in[3] = c ? d : 0; // 1 mux: c&d

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?