这部分需要把检材3和检材4仿真都开起来

一、第一步我们先把检材4数据库服务器的网络配置起来

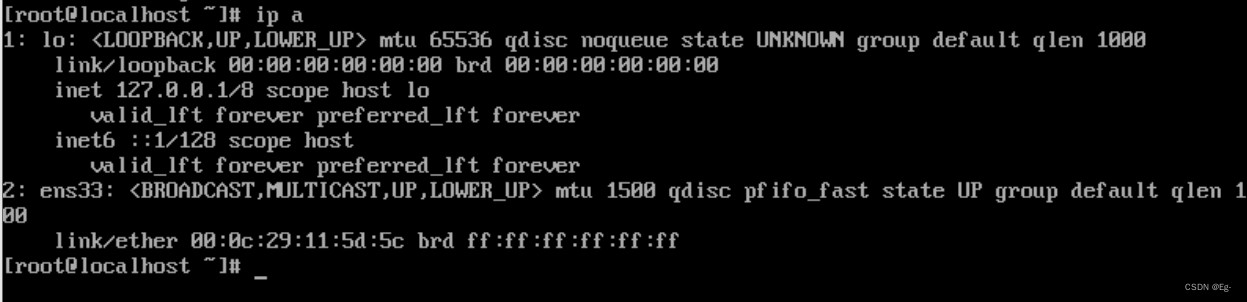

进入检材4的仿真,输入ip a命令看一下配置发现什么都没有

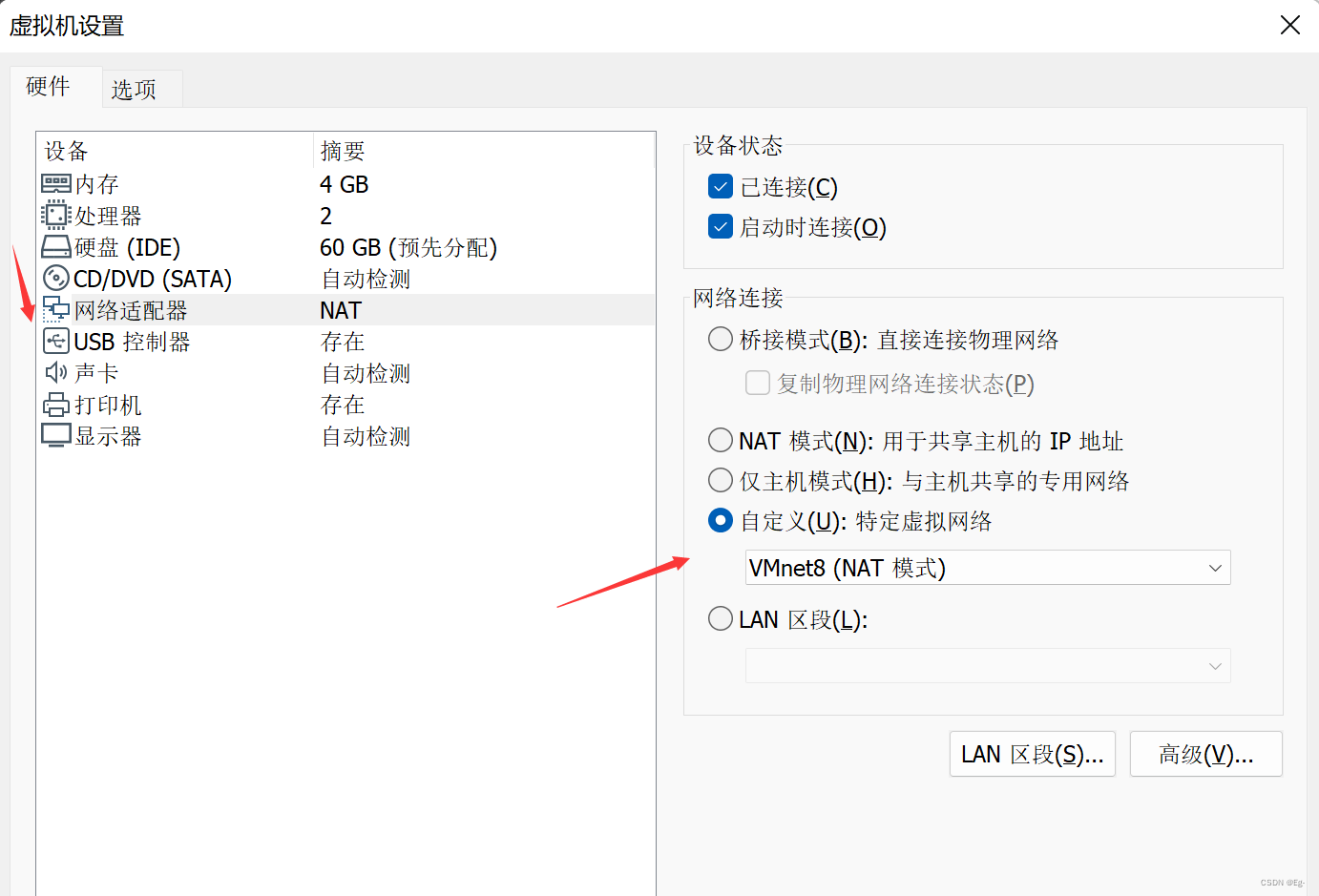

1、在虚拟机的设置里把网络连接模式设置为自定义:vmnet8

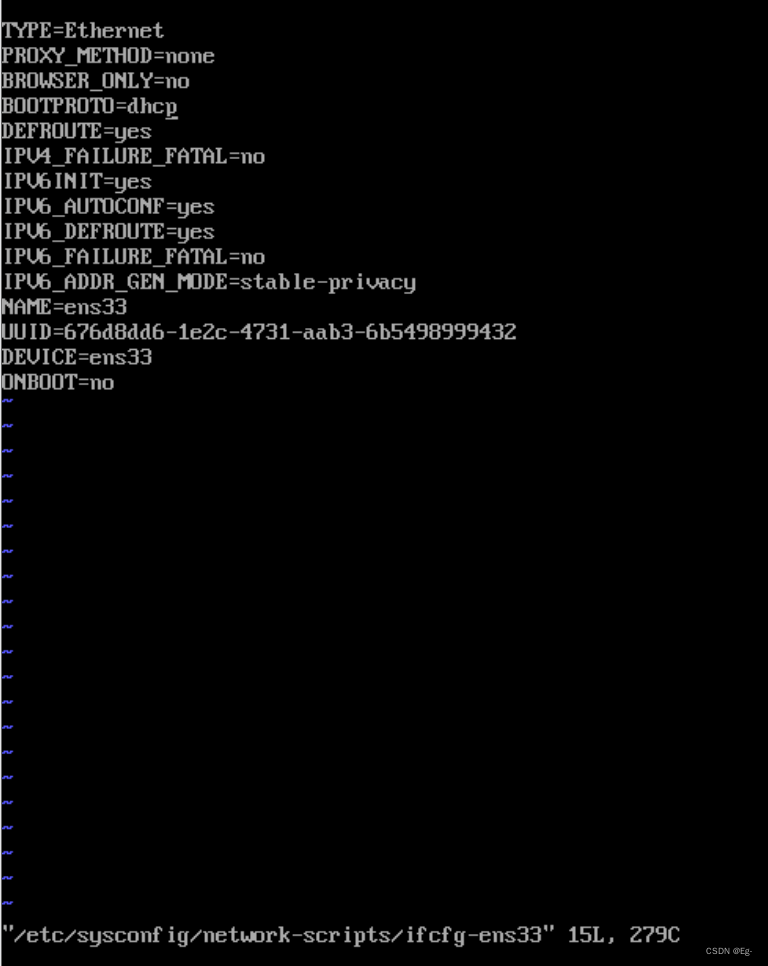

2、编辑网络配置文件

vi /etc/sysconfig/network-scripts/ifcfg-ens33按o进入编辑模式,Linux系统大小写敏感,注意不要输错

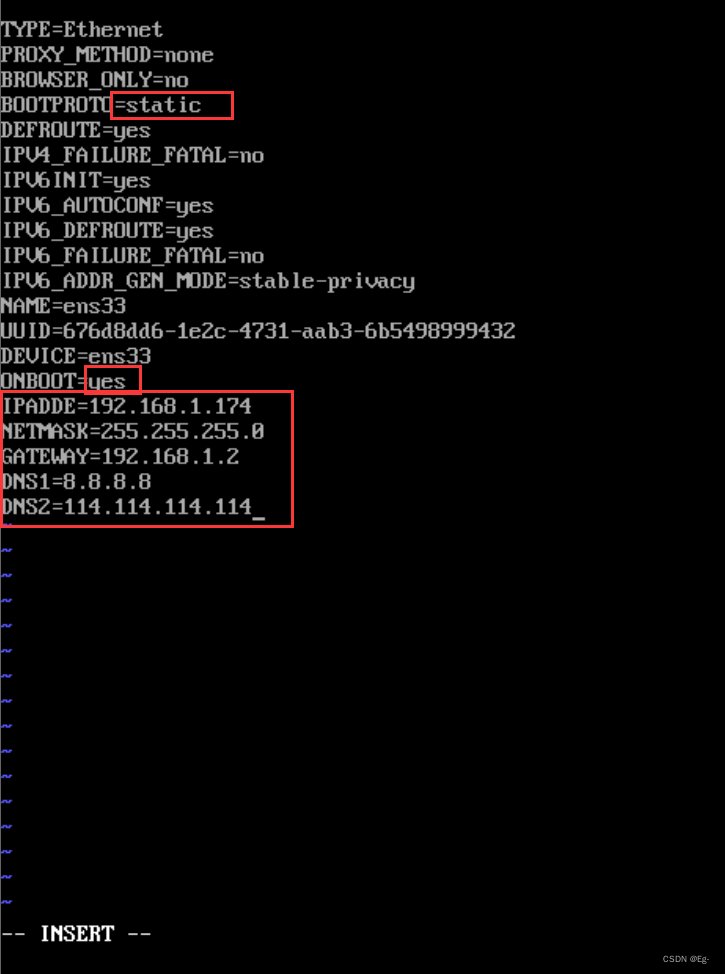

BOOTPROTO=dhcp改为BOOTPROTO=static

ONBOOT=no改为ONBOOT=yes

增加

IPADDR=192.168.1.174

NETMASK=255.255.255.0

GATEWAY=192.168.1.2

DNS1=8.8.8.8

DNS2=114.114.114.114

下面是修改前和修改后的设置

按Esc退出编辑模式,然后按:wq保存文件并退出vi

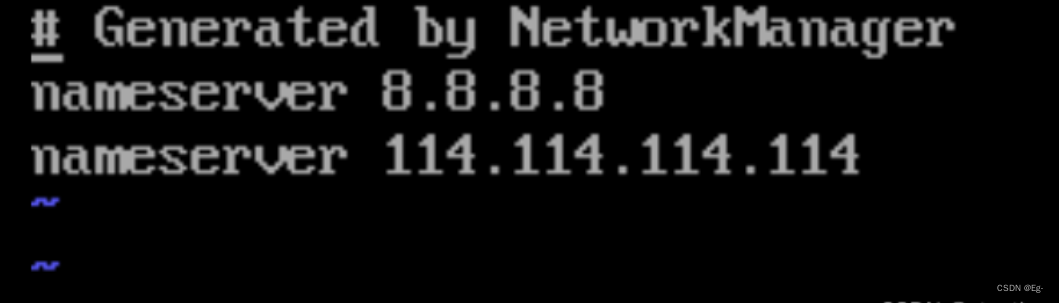

3、DNS配置

vi /etc/resolv.conf

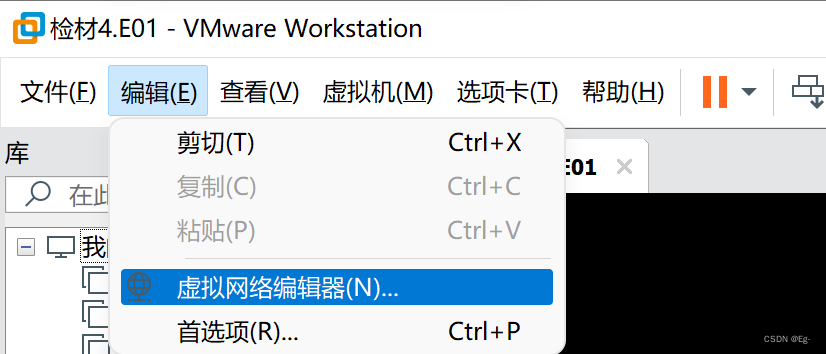

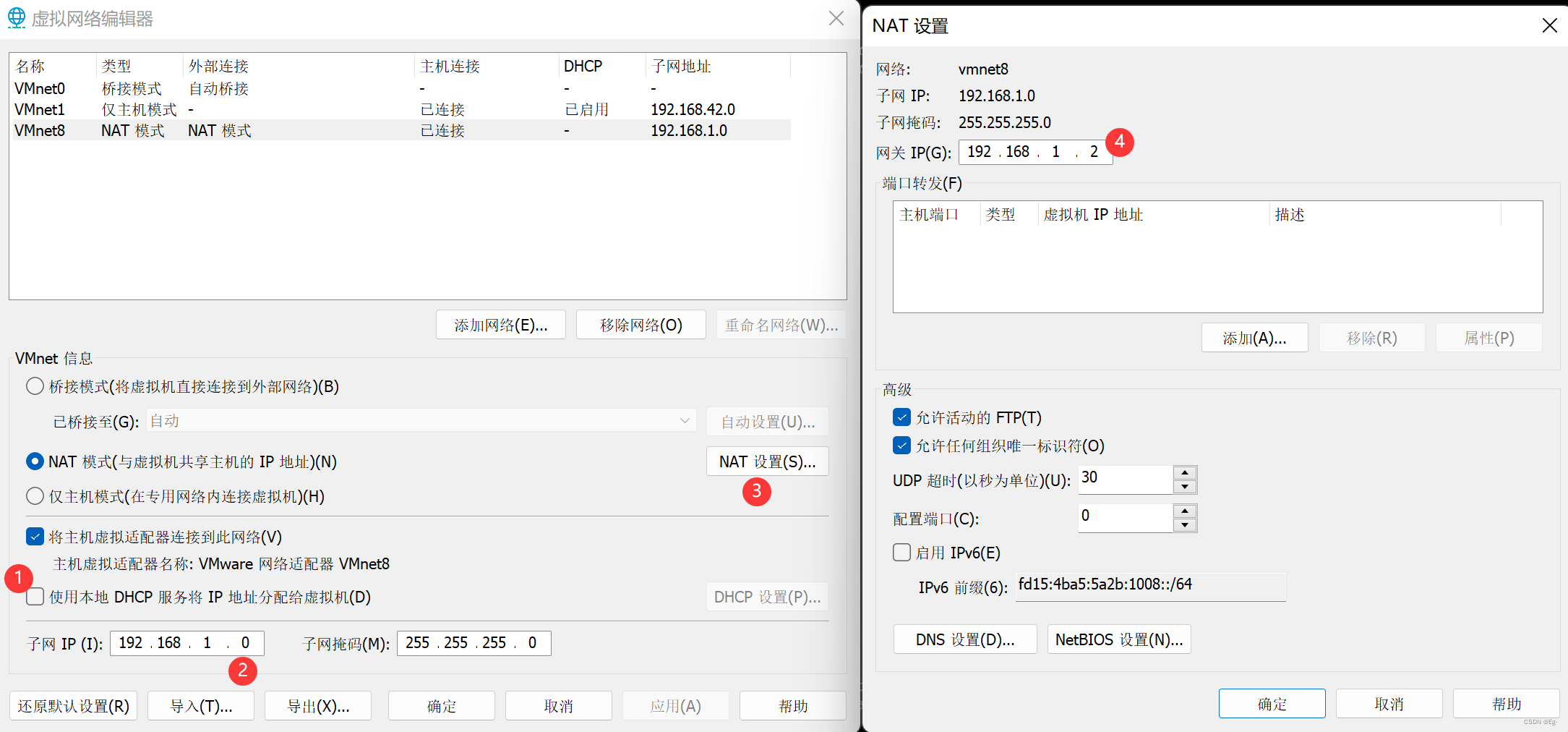

4、自定义VMnet8

取消DHCP,更改子网IP和网关IP

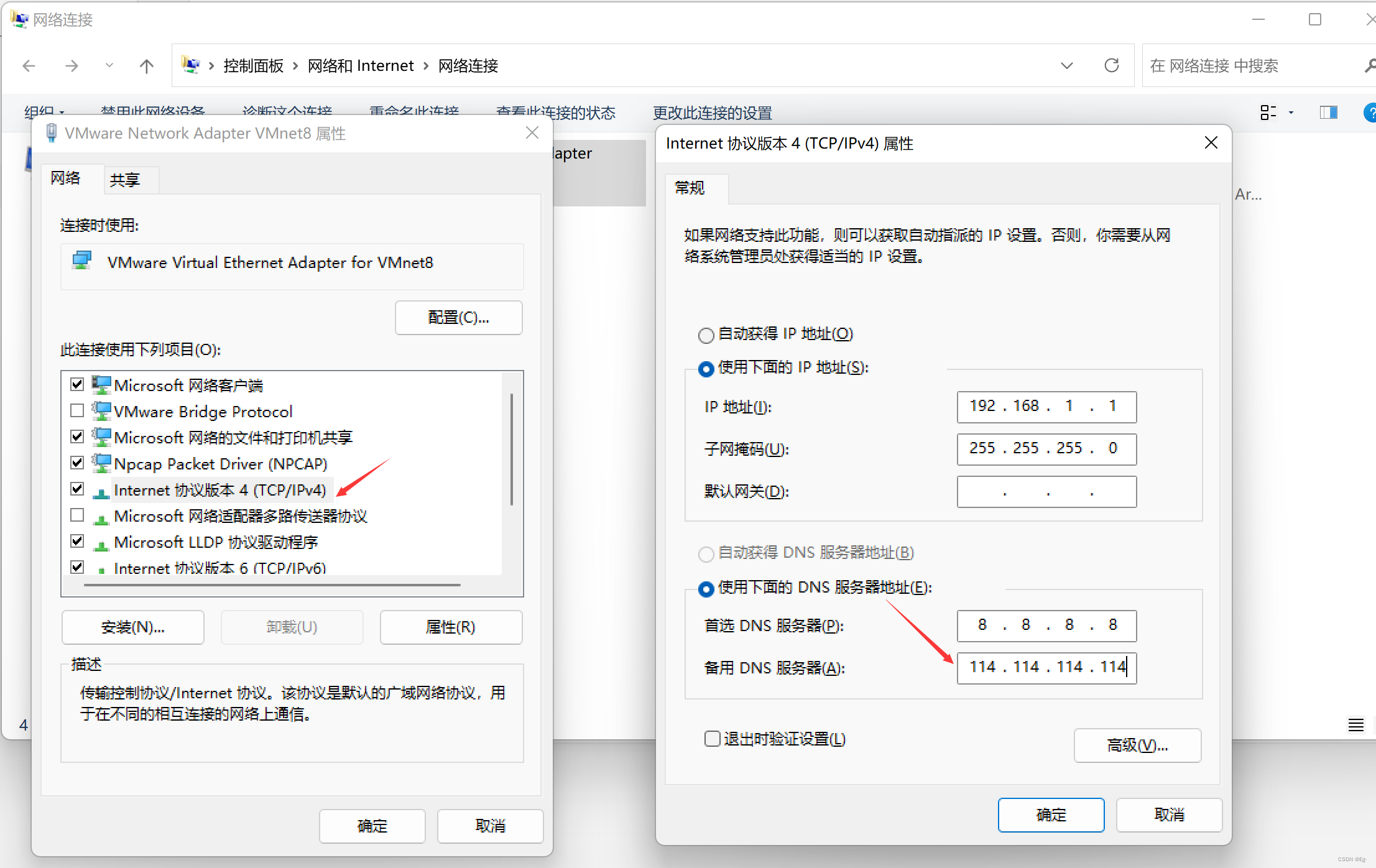

5、在本机上配置一下

6、回到检材4仿真

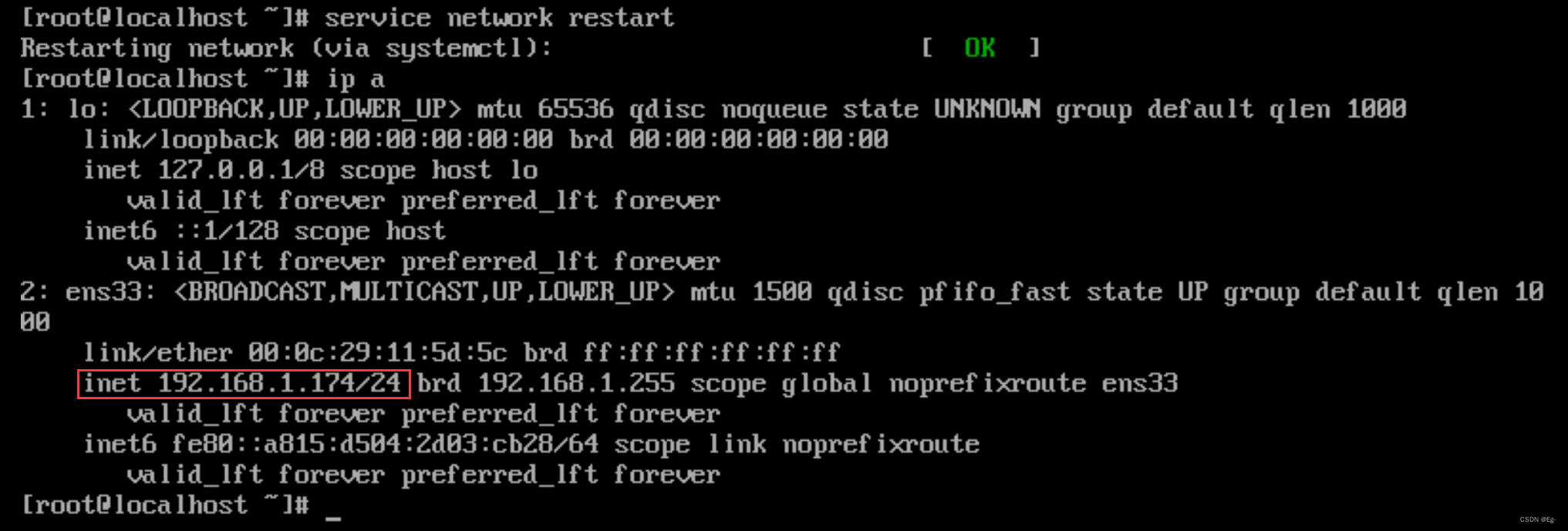

service network restart 重启网卡输入ip a命令查看,IP已经配置好了

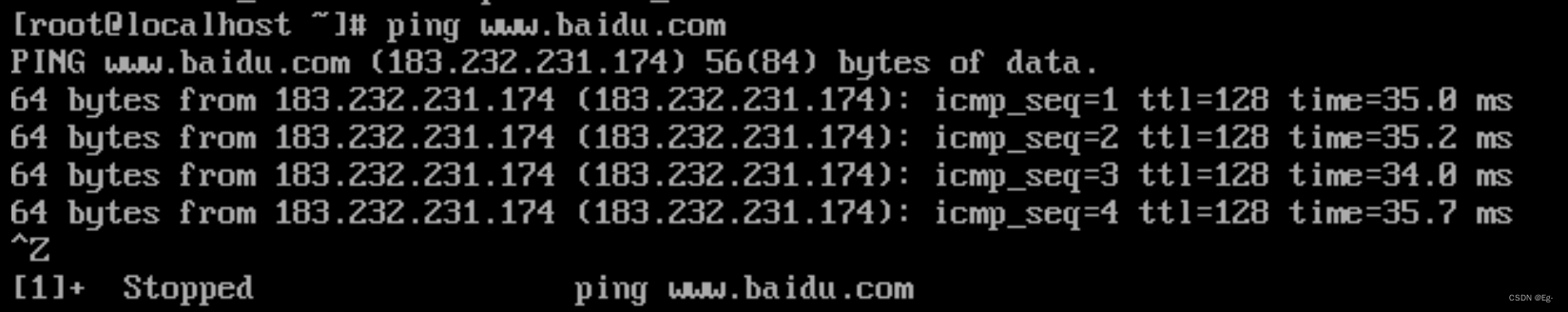

ping一下百度看看,是可以ping通的

然后开启下面这些服务

systemctl start docker开启docker服务

docker start sql1开数据库容器

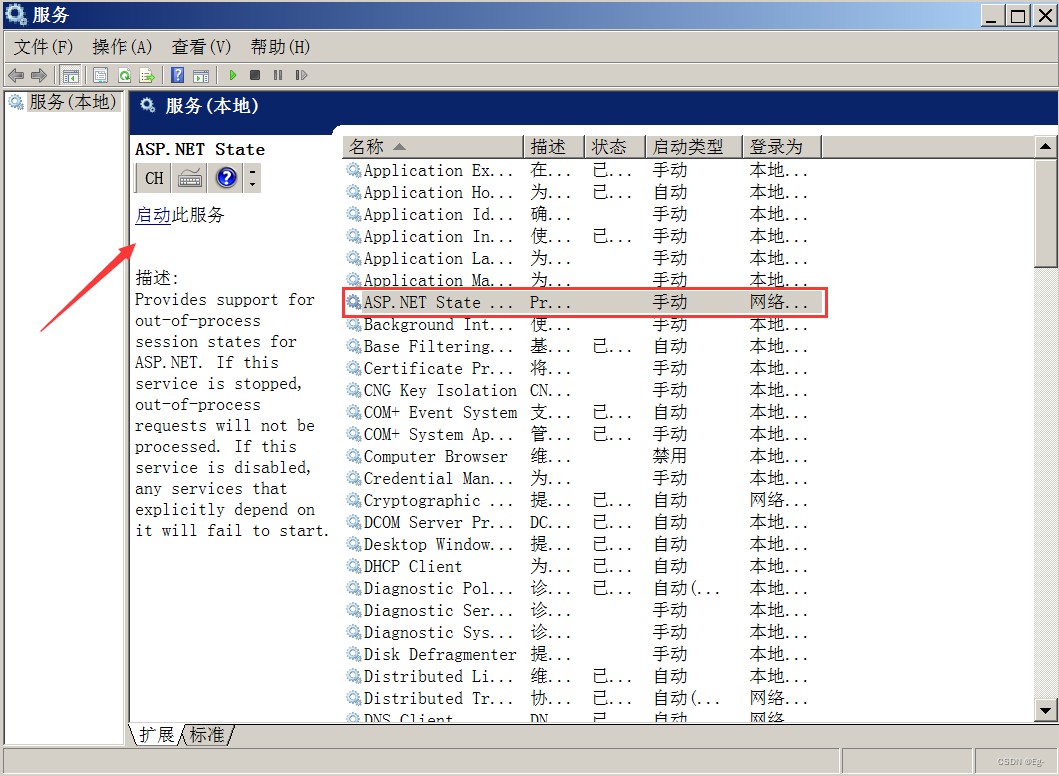

systemctl start mssql-server开数据库服务7、在检材3里面win+r输入services.msc,开启ASP服务

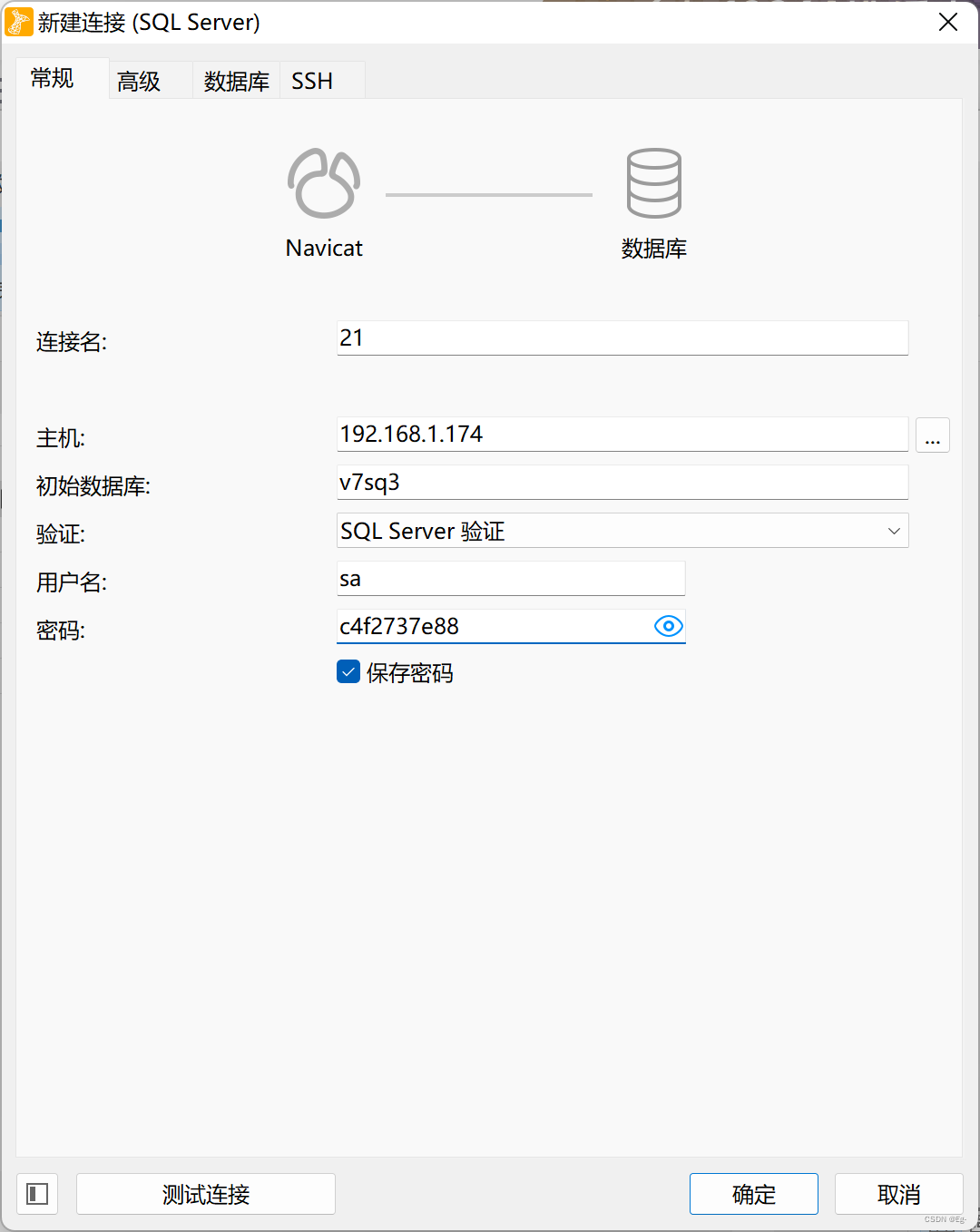

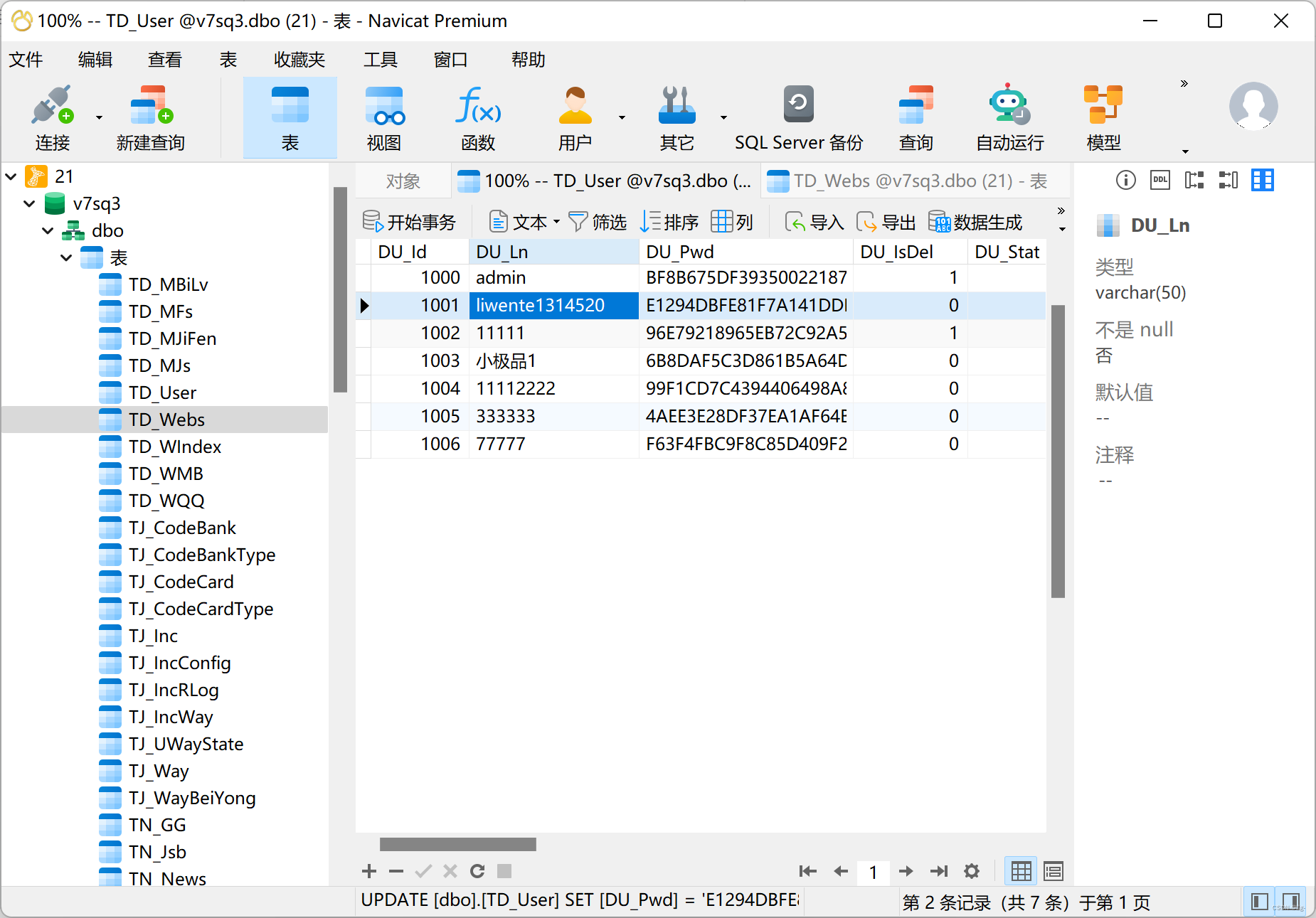

8、用navicat连,编辑-连接

连接成功

1549

1549

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?