实验三 16位算术逻辑运算实验

1、验证算术逻辑运算功能发生器 74LS181的16位运算组合功能。

2、掌握16位运算器的数据传送通路组成原理。

3、按要求和给出的数据完成几种指定的算术逻辑运算。

1、实验原理

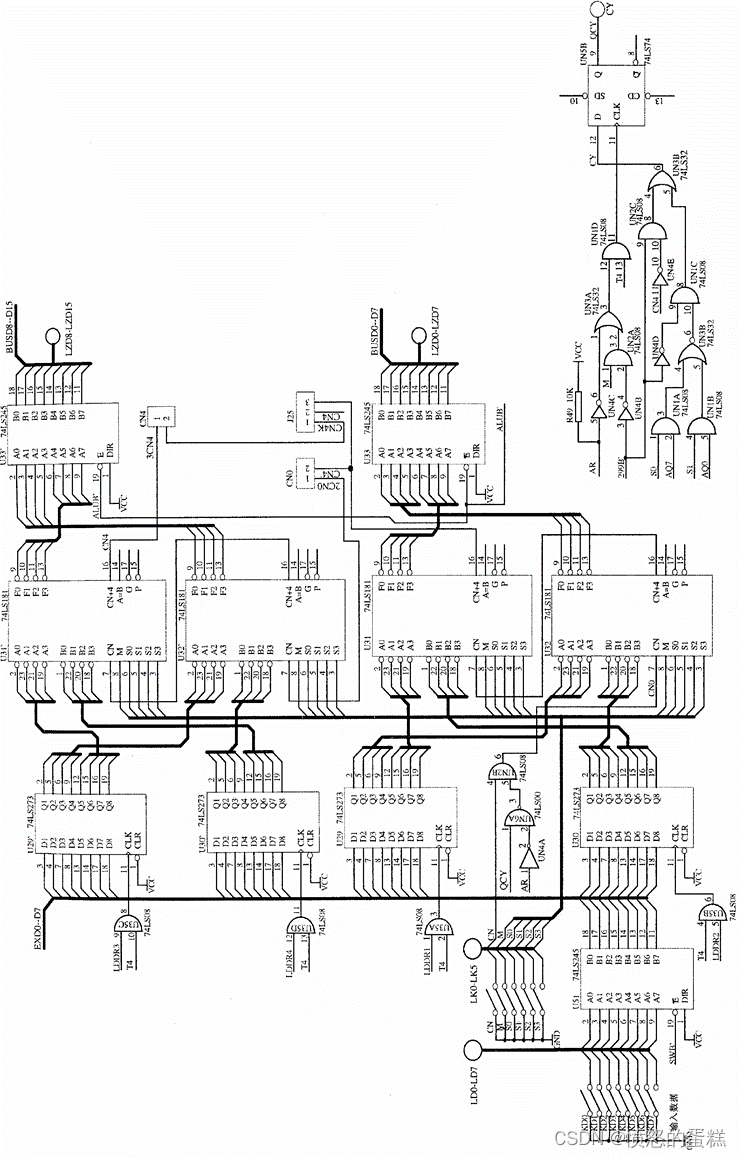

实验中所用16位运算器数据通路如图3.1所示。其中运算器由四片74LS181以并/串形成16位字长的ALU构成。低8位运算器的输出经过一个三态门74LS245(U33)到内部总线,低8位数据总线通过LZD0~LZD7显示灯显示;高8位运算器的输出经过一个三态门74LS245(U33`)到ALUO1`插座,实验时用8芯排线和高8位数据总线BUSD8~D15插座KBUS1或KBUS2相连,高8位数据总线通过LZD8~LZD15显示灯显示;参与运算的四个数据输入端分别由四个锁存器74LS273(U29、U30、U29`、U30、)锁存,实验时四个锁存器的输入并联连至内部数据总线再用8芯线连接到外部数据总线EXD0~D7插座EXJ1~EXJ3中的任一个;参与运算的数据源来自于8位数据开并KD0~KD7,并经过一三态门74LS245(U51)直接连至外部数据总线EXD0~EXD7,输入的数据通过LD0~LD7显示。

2、实验接线

本实验需用到6个主要模块:① 低8位运算器模块;② 数据输入并显示模块;③ 数据总线显示模块;④ 功能开关模块(借用微地址输入模块);⑤ 高8位运算器模;⑥ 高8位(扩展)数据总线显示模块。

根据实验原理详细接线如下(接线①~⑤同实验一):

(1)J20,J21,J22,接上短路片,

(2)J24,J25,J26接左边;

(3)J27,J28 左边

(4)J23 置右边T4选“ SD”

(5)JA5 置“接通”;

(6)JA6 置“手动”;

(7)JA3 置“接通”;

(8)JA1,JA2,JA4置“高阻”;

(9)JA8 置上面“微地址”

(10)EXJ1接BUS3

(11)ALO1'接KBUS1

(12)开关CE 、AR 置1

(13)0ZI2,CN4,CN0接上短路片

图3.1 16位运算器数据通路图

3、实验步骤

(1)连接线路,仔细查线无误后,接通电源。

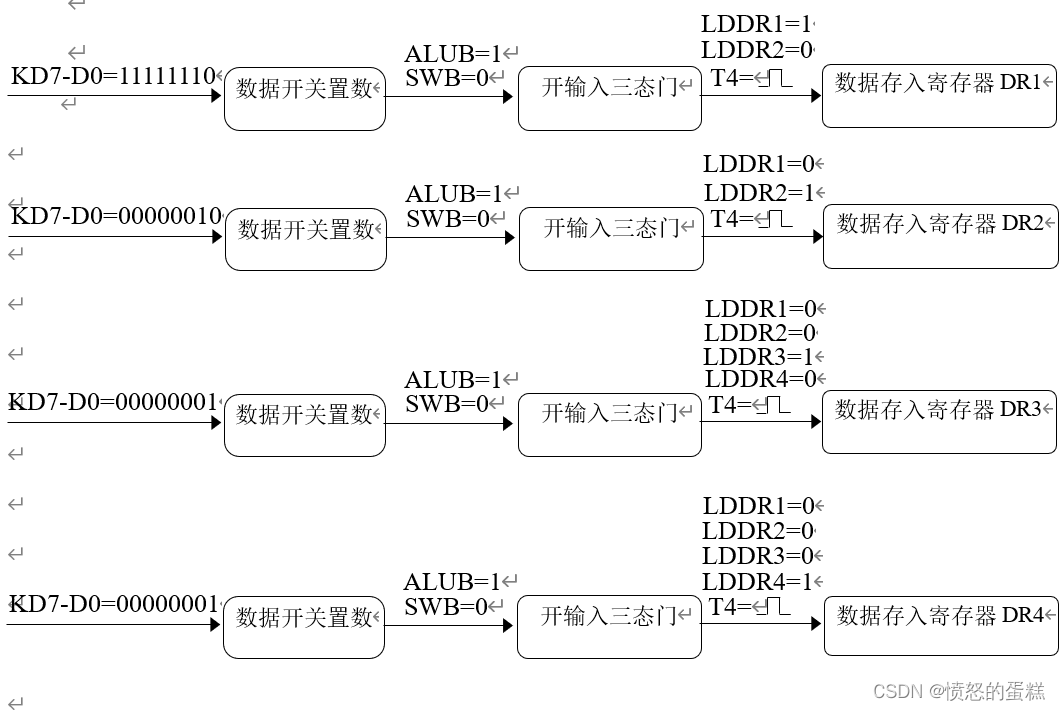

(2)用二进制数码开关KD7~KD0向DR1、DR2、DR3、DR4寄存器置数。方法:关闭ALU输出三态门应使ALUB`=1(即开关ALUB=1),开启输入三态门应使SWB`=0(即开关SWB=0),选通哪一个寄存器用对应开关LDDR1~LDDR4(高电平有效),其中LDDR3、LDDR4开关在高8位运算器上部,输入脉冲T4按手动脉冲发生按钮。设置数据开关具体操作步骤图示如下:

说明:LDDR1、LDDR2、ALUB`、SWB`、LDDR3、LDDR4六个信号电平由对应的开关LDDR1、LDDR2、ALUB、SWB、LDDR3、LDDR4给出,拨至上面为“1”,拨至下面为“0”,电平值由对应显示灯显示;T4由手动脉冲开关给出。

(3)验证74LS181的16位算术运算和逻辑运算功能(采用正逻辑)。

·开关SWB=1,关闭输入三态门;

·开关ALUB=0,打开输出三态门;

·LDDR1~LDDR4四个开关全拨至“0”电平。

说明:如果要实现16位带进位控制算术逻辑运算,只需在实验二的基础上将开 关AR=1置成AR=0即可。

·根据表3.1所示内容,置功能开关S3、S2、S1、S0、M、CN改变74LS181的算术运算和逻辑运算功能设置,观察运算器输出,将观察结果填入表3.1中,并将理论计算结果写入表3.2中,进行比较验证。

表3.1 实验结果

| 加数1 高位 DR3 | 加数1 低位 DR1 | 加数2 高位 DR4 | 加数2 低位 DR2 | S3 S2 S1 S0 | M=0(算术运算) | M=1 (逻辑运算) | |

| Cn=1 无进位 | Cn=0 有进位 | ||||||

| 01 | FE | 01 | 02 | 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | F=(01FF) F=(01FF) F=(FFFF) F=(FFFF) F=(02FA) F=(02FA) F=(00FB) F=(00FB) F=(0300) F=(0300) F=(0101) F=(0101) F=(03FC) F=(03FC) F=(01FD) F=(01FD)

| F=(01FF) F=(01FF) F=(0000) F=(0000) F=(02FB) F=(02FB) F=(00FC) F=(00FC) F=(0301) F=(0301) F=(0102) F=(0102) F=(03FD) F=(03FD) F=(01FE) F=(01FE) | F=(FE01) F=(FE01) F=(0000) F=(0000) F=(FEFD) F=(FEFD) F=(00FC) F=(00FC) F=(FF03) F=(FF03) F=(0102) F=(0102) F=(FFFF) F=(FFFF) F=(01FE) F=(01FE) |

注意:本实验做完后,拔掉连线ALUBUS`和ALUO1`,去掉短路套ZI2、CN0、CN4。

1、 若有两个16位二进制数 :00FFH和2D5AH, 要求通过74LS181的运算,计算这两数相与的结果。

(1)实现的方法

将S3,S2,S1,S0置为1011,M置0、Cn置0,实现两数相与。

(2)实验步骤

a.连接线路,仔细查线无误后,接通电源。

b.用二进制数码开关KD7~KD0向DR1、DR2、DR3、DR4寄存器置数。

方法:关闭ALU输出三态门应使ALUB`=1(即开关ALUB=1),开启输入三

态门应使SWB`=0(即开关SWB=0),选通哪一个寄存器用对应开关LDDR1

~LDDR4(高电平有效),其中LDDR3、LDDR4开关在高8位运算器上部,

输入脉冲T4按手动脉冲发生按钮。

(3)实验结果

D25A

(4)理论计算结果

D25A

2、 若有两个16位二进制数 :1234H和A987H, 要求通过74LS181的运算,计算这两数之和。

(1)实现的方法

将S3,S2,S1,S0置为1001,M置0、Cn置1,实现两数之和

(2)实验结果

BBBB

(3)理论计算结果

BBBB

3、若被减数为7C69H和减数为1234H, 要求通过74LS181的运算,计算这两数之差。

(1)实现的方法

将S3,S2,S1,S0置为0110,M置0、Cn置0,实现两数之差。

(2)实验结果

6A35

(3)两数之差

6A35

4、若被减数为1234 H和减数为7C69H, 要求通过74LS181的运算,计算这两数之差。和题4结果比较。

(1)实验步骤

a.连接线路,仔细查线无误后,接通电源。

b.用二进制数码开关KD7~KD0向DR1、DR2、DR3、DR4寄存器置数。

方法:关闭ALU输出三态门应使ALUB`=1(即开关ALUB=1),开启输入三态门应使SWB`=0(即开关SWB=0),选通哪一个寄存器用对应开关LDDR1~LDDR4(高电平有效),其中LDDR3、LDDR4开关在高8位运算器上部,

输入脉冲T4按手动脉冲发生按钮。

(2)实验结果

95CB

(3)实验结果表示的是什么

答:实验结果表示1234H和7C69H的差。

(4)比较题4和题3结果,并加以说明。

答:题4和题3结果分别是6A35和95CB,两者和为0000,所以互为相反数。

四、实验结果分析及总结

16位的数据拆成两个8位输入,DR1存放加数1的低位,DR2存放加数2的低位,DR3存放加数1的高位,DR4存放加数2的高位。置数操作没有变化,打开相应寄存器的门,按下手动脉冲T4就行。然后拨动S0~S3,M,CN,验证实验结果。

实验3是在实验1的基础上扩展,但是大体思路没有变,注意存数就行。经过了3次实验,对整个实验流程有了进一步的掌握,体会到了74181的算术逻辑运算功能。实验时,注意接线,按照实验指导书一步一步来做,就没有太大的问题。

4329

4329

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?