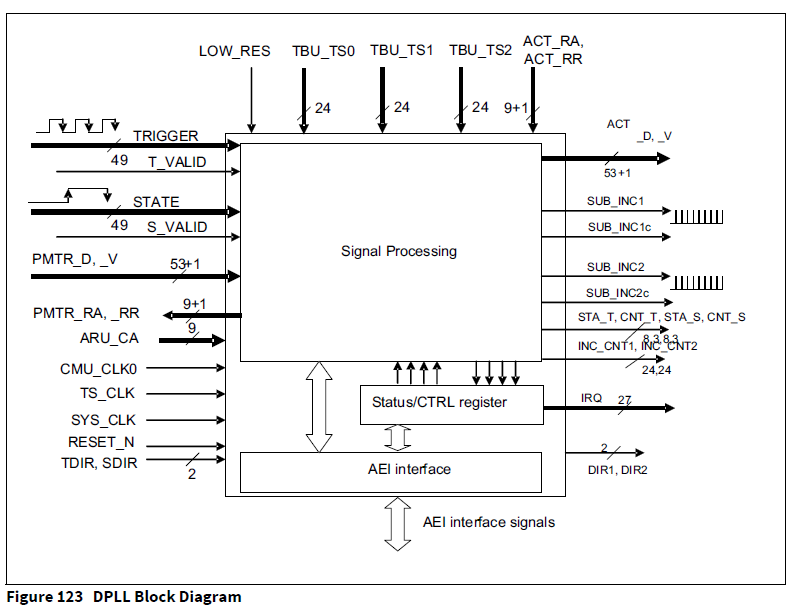

1、主要框图

2、主要信号说明

以下对各信号简单说明

注意TIM1 CH0使用的是TIEM测量模式

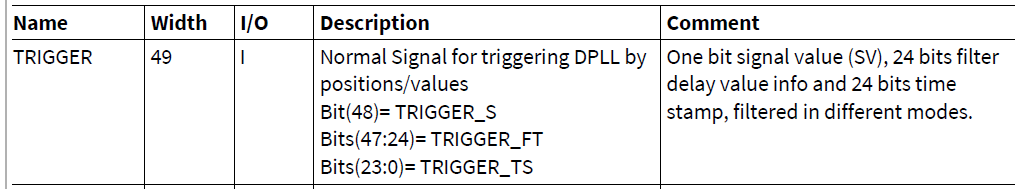

2.1、TRIGGER(49bit)

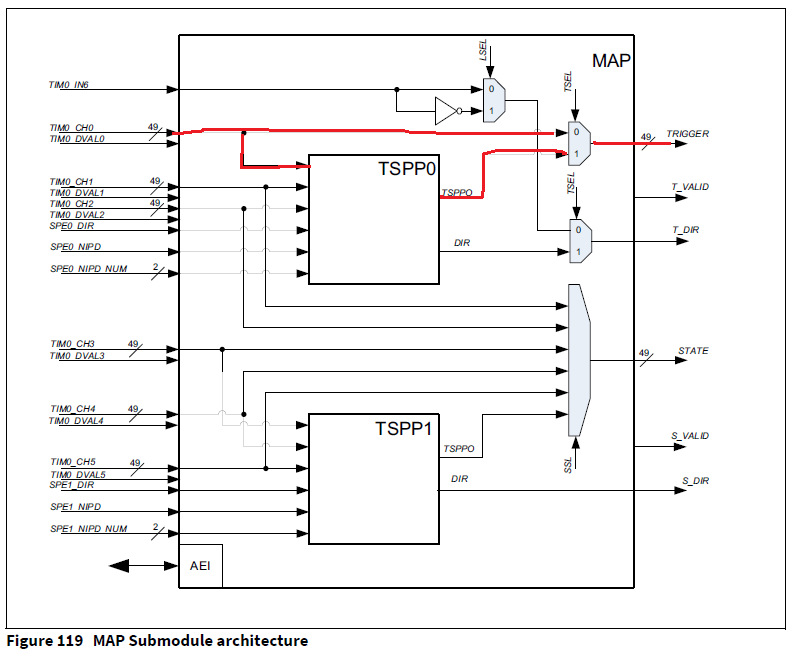

来自TIM0_CH0或来自TSPP0处理TIM0_CH0后的信号TSPPO。本文只讨论来自TIM0_CH0的信号。

其中

bit0~bit23是时基,链接到ARU_OUT(23:0),即TBU_TS0存到GPR0;

bit47~bit24是时基,链接到ARU_OUT(47:24),即TBU_TS0存到GPR1;

bit49是信号值,链接到ARU_OUT(48),即TIM0 CH0采集的信号是上升沿还是下降沿。当也原始信号出现上升沿时,整个ECNT计数器值总是奇数,而当也原始信号出现下降沿时,它总是偶数,可以通过判断ECNT寄存器的bit0(即ARU_OUT(48))判断是上升沿还是下降沿。

总结:TRIGGER代表测量的来自TIM0_IN0(原始的信号)经过滤波等处理后TIM0_OUT0的信号。其中bit48代表上升沿(0)还是下降沿(1),bit47~24代表TBU_TS0,bit23~0代表TBU_TS0。

2.2、T_VALID

TRIGGER值的有效性,未理解含义,未理解实际怎么使用。

2.3、STATE

类似于TRIGGER,STATE代表测量的来自TIM0_IN1(原始的信号)经过滤波等处理后TIM0_OUT1的信号。

2.4、S_VALID

STATE值的有效性,未理解含义,未理解实际怎么使用。

2.5、PMTR_D

3、主要功能

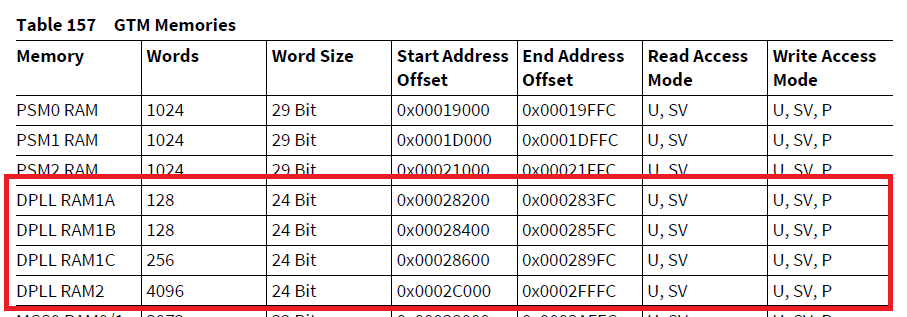

3.1、DPLL RAM

DPLL模块自带RAM模块,各子功能RAM的地址和大小如下图。主要有RAM1A,RAM1B,RAM1C,RAM2四块RAN区域。

注意:以下地址为相对地址。

以下为GTM模块的地址0xF0100000u。举例DPLL_RAM2的绝对地址是:

0xF0100000u+0x0002C000 = 0xF012C000

4、主要寄存器

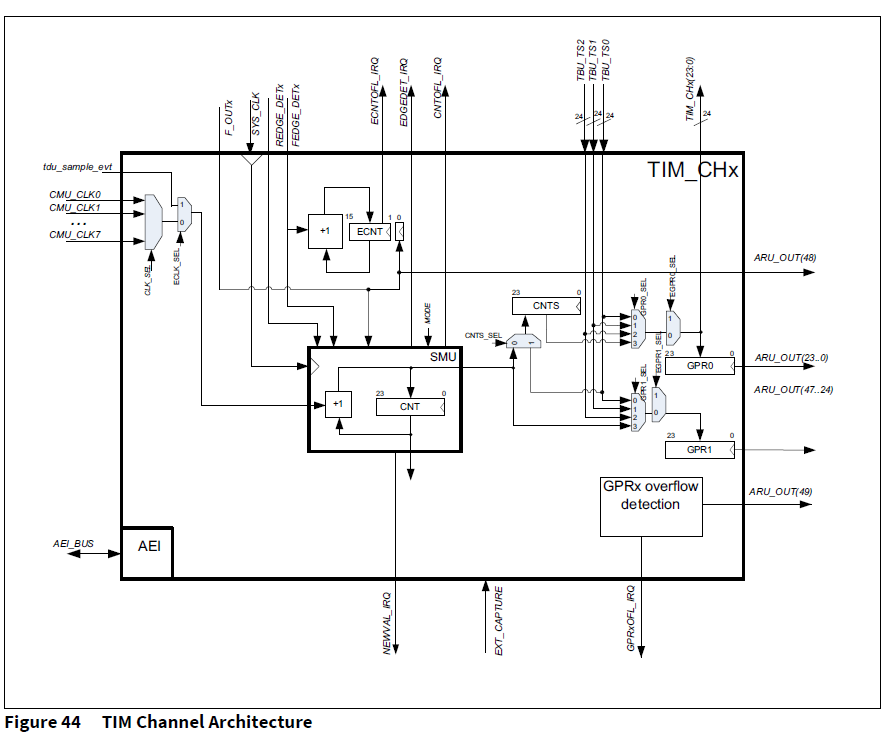

4.1、TIM0 CH0主要寄存器

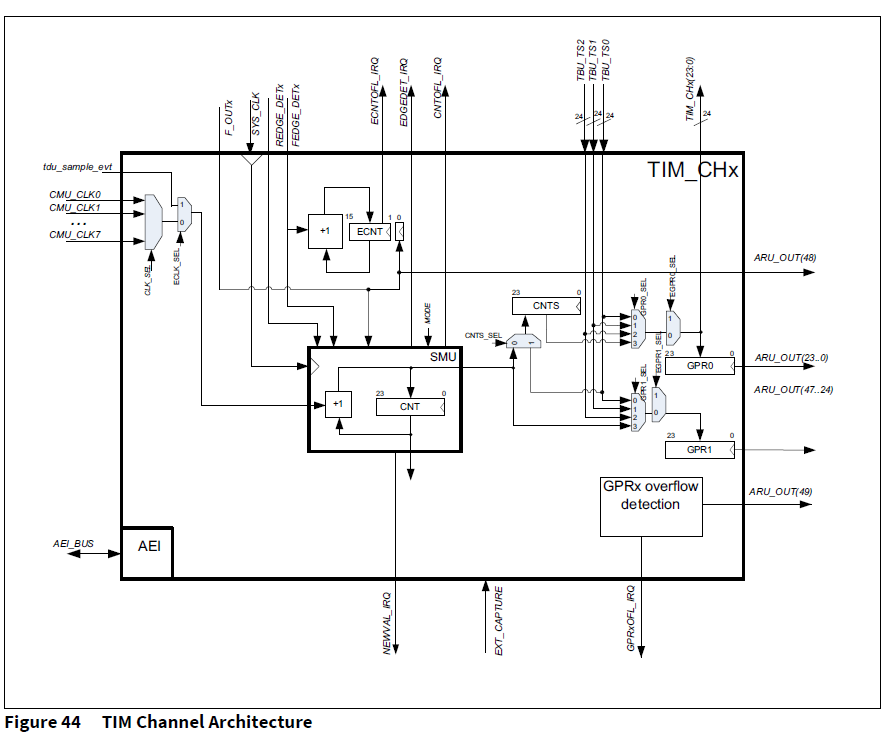

主要基于下图涉及的寄存器讲解

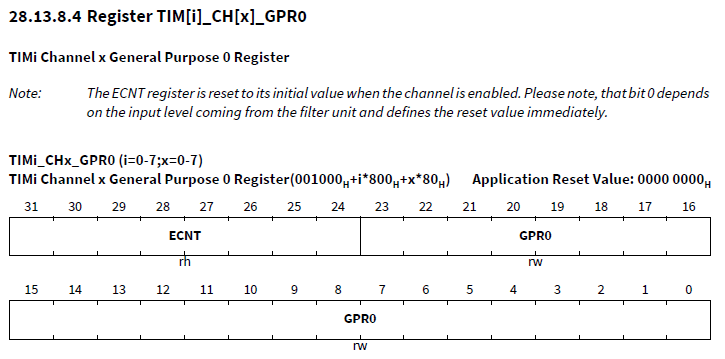

4.1.1、GPR0寄存器

包含了8bit的ECNT边沿检测和24bit的GPR0寄存器。

8bit ECNT只读,为奇数时表示上升沿,偶数时表示下降沿;

24bit GPR0寄存器的值可以来源于以下4种可能:

24bit CNTS寄存器(影子寄存器);

24bit TBU_TS0;

24bit TBU_TS1;

24bit TBU_TS2;

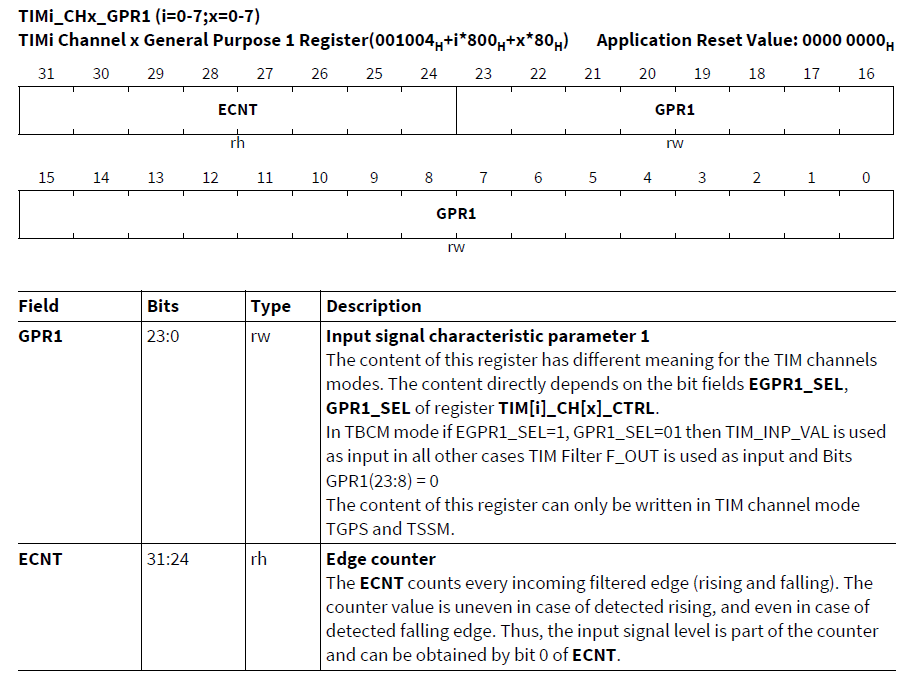

4.1.2、GPR1寄存器

包含了8bit的ECNT边沿检测和24bit的GPR1寄存器。

8bit ECNT只读,为奇数时表示上升沿,偶数时表示下降沿;

24bit GPR1寄存器的值可以来源于以下4种可能:

24bit SMU的CNT寄存器;

24bit TBU_TS0;

24bit TBU_TS1;

24bit TBU_TS2;

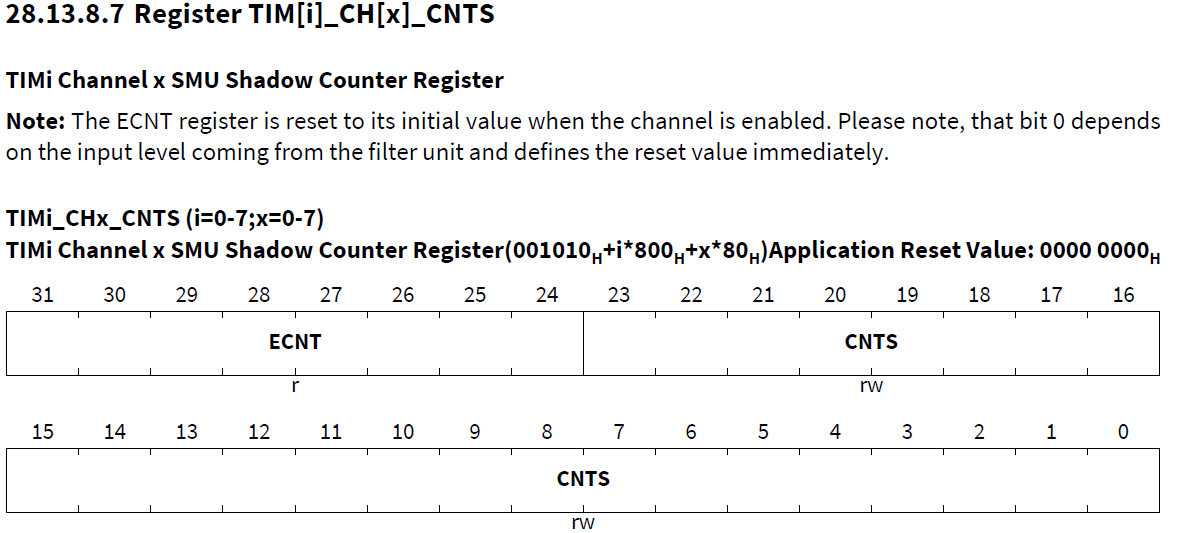

4.1.3、CNTS寄存器

包含了8bit的ECNT寄存器、24bit的CNTS影子寄存器

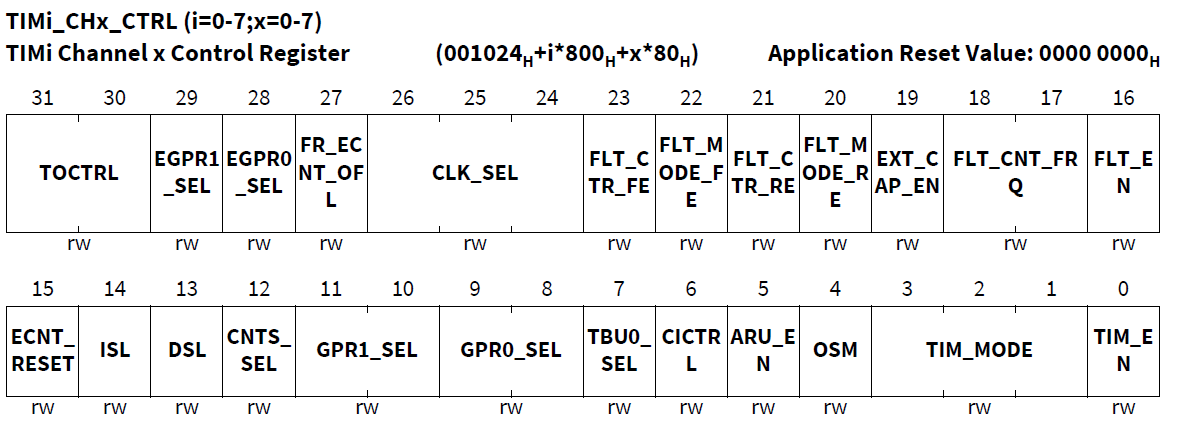

4.1.4、控制寄存器

bit0:TIM_EN,TIM channel x enable,通道使能

bit1~bit3:TIM_MODE,TIM channel x mode,通道模式,有6种模式,TPWM、TPIM、TIEM、TIPM、TBCM、TGPS和TSSM。

bit4:OSM,One-shot mode,连续采集模式还是一次采集模式

bit5:ARU_EN,GPR0 and GPR1 register values routed to ARU,GPR0和GPR1寄存器是否通过ARU传输

bit6:CICTRL,通道输入使用本通道还是上一个通道

bit7:TBU0_SEL,使用TBU_TS0(共27bit)的高24bit还是低24bit存储GPR0和GPR1寄存器的值

bit8~bit9:GPR0_SEL,选择GPR0来源。

来源可以是:

TBU_TS0(24bit)+ ECNT(8bit)组成32bit GPR0寄存器。使用EGPR0_SEL控制是否接到GPR0寄存器(EGPR0_SEL=0表示接,EGPR0_SEL=1表示断开)

TBU_TS1(24bit)+ TIM_INP_VAL(8bit)组成32bit GPR0寄存器。使用EGPR0_SEL控制是否接到GPR0寄存器(EGPR0_SEL=0表示接,EGPR0_SEL=1表示断开)

TBU_TS2(24bit)+ 预留(8bit)组成32bit GPR0寄存器。使用EGPR0_SEL控制是否接到GPR0寄存器(EGPR0_SEL=0表示接,EGPR0_SEL=1表示断开)

CNTS寄存器(24bit)+ 预留(8bit)组成32bit GPR0寄存器。使用EGPR0_SEL控制是否接到GPR0寄存器(EGPR0_SEL=0表示接,EGPR0_SEL=1表示断开)

bit10~11:GPR1_SEL,选择GPR1来源。

来源可以是:

TBU_TS0(24bit)+ ECNT(8bit)组成32bit GPR1寄存器。使用EGPR1_SEL控制是否接到GPR1寄存器(EGPR1_SEL=0表示接,EGPR1_SEL=1表示断开)

TBU_TS1(24bit)+ TIM_INP_VAL(8bit)组成32bit GPR1寄存器。使用EGPR1_SEL控制是否接到GPR1寄存器(EGPR1_SEL=0表示接,EGPR1_SEL=1表示断开)

TBU_TS2(24bit)+ 预留(8bit)组成32bit GPR1寄存器。使用EGPR1_SEL控制是否接到GPR1寄存器(EGPR1_SEL=0表示接,EGPR1_SEL=1表示断开)

SMU的CNT寄存器(24bit)+ 预留(8bit)组成32bit GPR1寄存器。使用EGPR1_SEL控制是否接到GPR1寄存器(EGPR1_SEL=0表示接,EGPR1_SEL=1表示断开)

bit12:CNTS_SEL,选择影子寄存器CNTS。可来源于:TBU_TS0或SMU的CNT寄存器

bit13:DSL,测量上升沿或下降沿选择(仅

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2164

2164

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?